在开发FPGA绑定管脚时,经常会看到HP Bank、HR Bank和HD Bank,它们分别是什么意思?分别可以适用于哪些应用个?

首先我们要明确一点,这几个概念都是在7系列之后才有的,其中7系列的FPGA中有HP Bank和HR Bank,UltraScale FPGA有HP Bank、HR Bank和HD Bank,但并不是一个FPGA中会同时包含HP/HR/HD Bank。

HP:High Performance

HR:High Range

HD:High Density

HP Bank,从名字就可以看出来,应用于高性能也就是速度比较高的场景,比如DDR或者其它高速差分总线(不是gtx),由于速率比较高,Bank电压最高也只能到1.8V。

HR Bank表示支持wider range of I/O standards,最高能够支持到3.3V的电压。

HD Bank应用于低速I/O的场景,最高速率限制在250M以内,最高电压也是支持到3.3V

Kintex UltraScale 和Virtex UltraScale中有HP Bank和HR Bank,Virtex UltraScale+系列中只有HP Bank,Zynq UltraScale+ MPSoC 和Kintex UltraScale+ 系列包含HP和HR Bank。

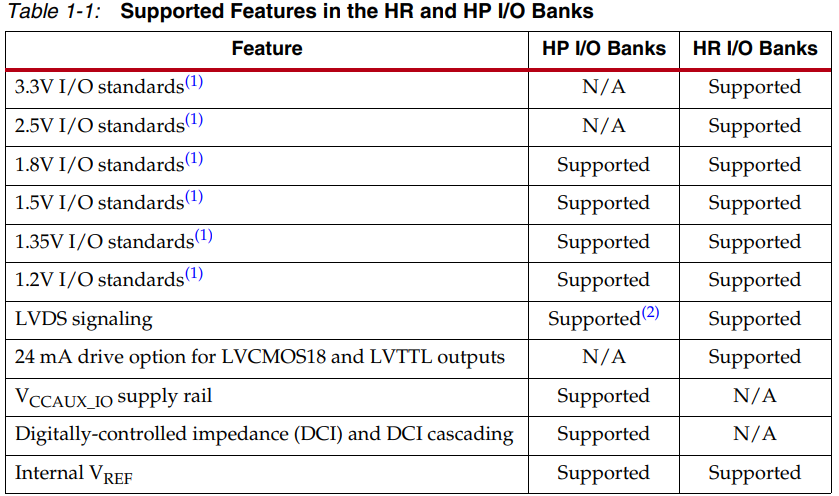

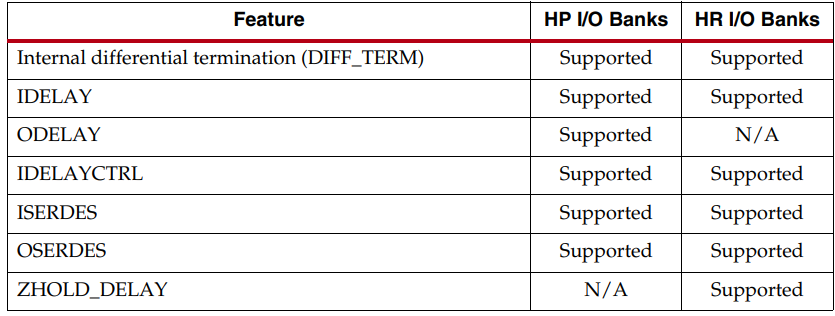

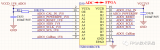

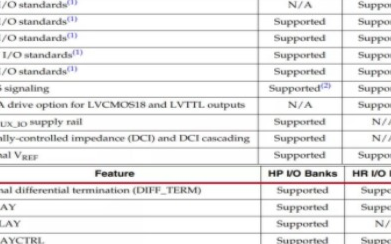

由于应用场景不同,支持的IO原语也有差异,下图是7系列FPGA HP Bank和HR Bank支持的特性:

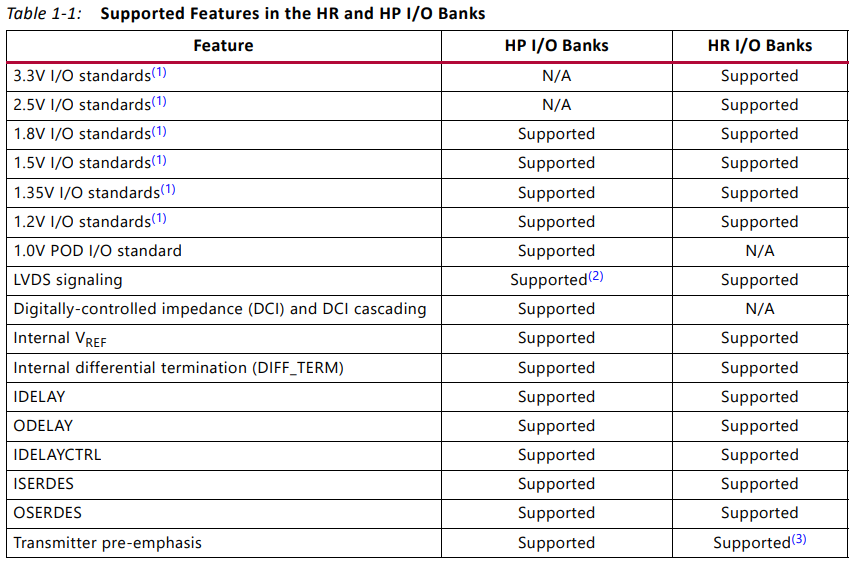

下图是UltraScale系列FPGA HP Bank和HR Bank支持的特性:

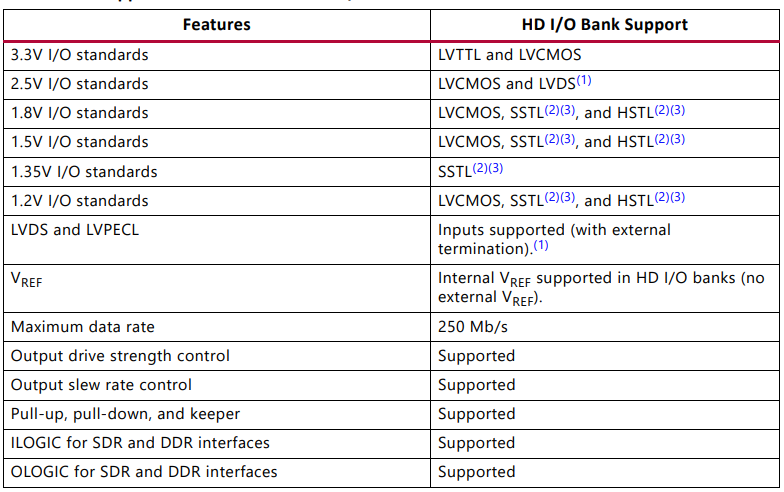

HD Bank由于相对特殊一些,单独列了出来:

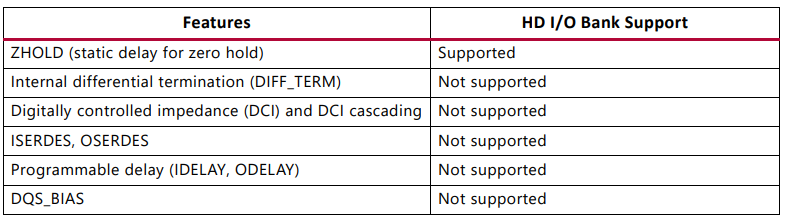

在UG575中也可以看到不同的FPGA中HR、HP和HD Bank的IO数量:

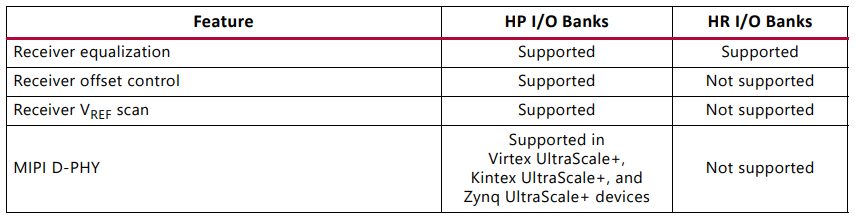

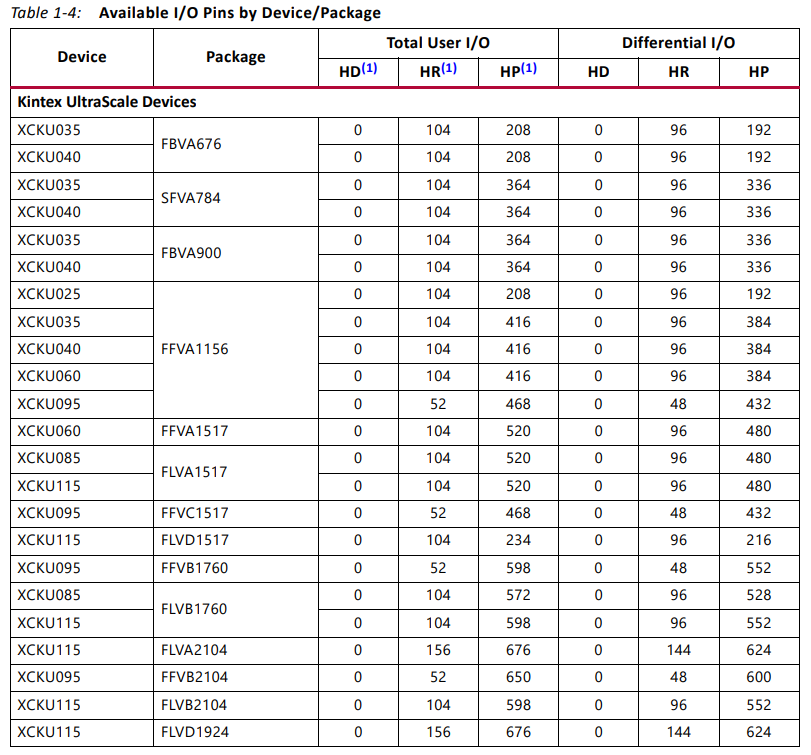

这里我们讲到了7系列和UltraScale系列,就顺便提一下UltraScale系列相对7系列的新的feature:

原文标题:Xilinx FPGA中HP HR HD bank分别是什么用途

文章出处:【微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22554浏览量

640512 -

电压

+关注

关注

45文章

5798浏览量

122511 -

bank

+关注

关注

0文章

16浏览量

15279

原文标题:Xilinx FPGA中HP HR HD bank分别是什么用途

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AD9910的SYNC_IN+、SYNC_IN-这2个LVDS输入时钟是否可以和FPGA的HP bank(1.8V供电)输出的LVDS时钟相连吗?

在HP Bank中如何连接PCI?

可以直接将时钟缓冲器的输出连接到HR库吗?

7系列FPGA HR bank IO如何与DDR3连接?

HR / HP bank中的7系列LVDS输入延迟的解决办法?

XAPP520将符合2.5V和3.3V I/O标准的7系列FPGA高性能I/O Bank进行连接

DCI是什么?Xilinx 7系列FPGA的HP bank都支持DCI

如何解决FPGA引脚与LVDS信号相连时兼容性的问题

HR和HP banks基本介绍

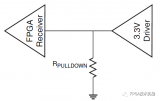

Xilinx 7系列FPGA高性能接口与2.5V/3.3V外设IO接口设计

基于TXS0108实现FPGA IO Bank接不同外设IO接口电压转换

FPGA中HP/HR/HD Bank的应用

FPGA中HP/HR/HD Bank的应用

评论