TCL在IC领域中常用的脚本有Tcl、Perl、Shell、Python等,在这些脚本里面,Tcl(“工具命令语言”( 即Tcl的全称Tool Command Language))由于其语法简单,易上手等特点,在FPGA开发中越来越受到重视。

John K. Ousterhout于 1988 年开始开发 Tcl/Tk(读作“tickle tee-kay”),然后是加州大学伯克利分校的一名教授继续对它进行开发。目前TCL在很多EDA工具(Design Complier、quartus、Synplify、modesim、finesim、Vivado等)中都扮演重要角色,这也是为什么在FPGA设计中受到重视的主要原因。

TCL让FPGA开发更完美

目前FPGA几大厂商中,Xilinx和Intel无疑在国内占据很大市场,其对应的开发的EDA工具分别为Quartus II和Vivado(老版本ISE),接下来以Vivado为例简单说明其Tcl在开发过程中的应用。

Xilinx的设计套件Vivado相比上一代产品ISE,在运行速度、算法优化和功能整合等很多方面都有了显著地改进。其中约束语言XDC及脚本语言TCL的引入更是让其开发更加完美。

下面从几个方面说明一下Tcl在Vivado中的应用:

非工程模式(NoneProject Mode)

传统的FPGA开发都是通过GUI界面进行相关的“按钮”式操作,Vivado则在引入Tcl解释器后,可以通过非工程模式进行操作,一个Tcl脚本即可自动化建立工程,对工程进行分析。

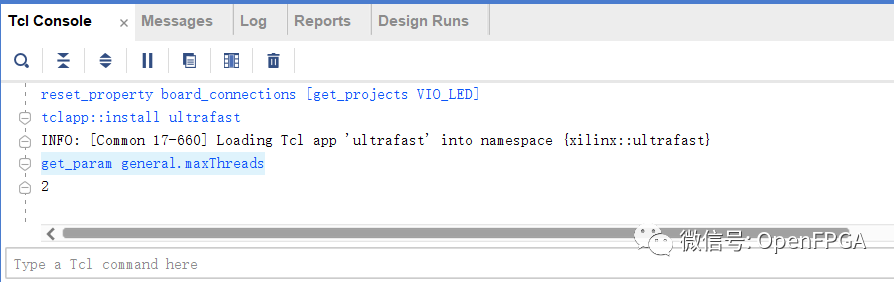

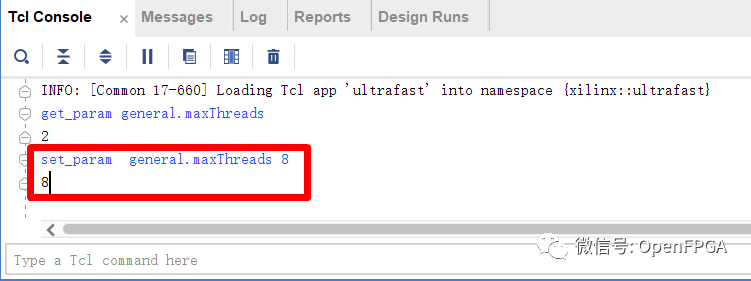

提高编译效率

Vivado“出现”的比较晚,所以对于多线程的支持还是比较友好的,默认情况下,Vivado在Windows默认是2个线程(综合阶段,Windows/Linux操作系统都是2),实现阶段Windows默认也是2个线程(Linux操作系统的默认线程数为8),我们可以通过

同时可以通过

使用Tcl定位目标

Vivado实现完成后,可以对出问题的路径进行分析,同时对网表中的目标进行查找、定位和遍历,其中常见的命令大家应该都有见过:

get_ports

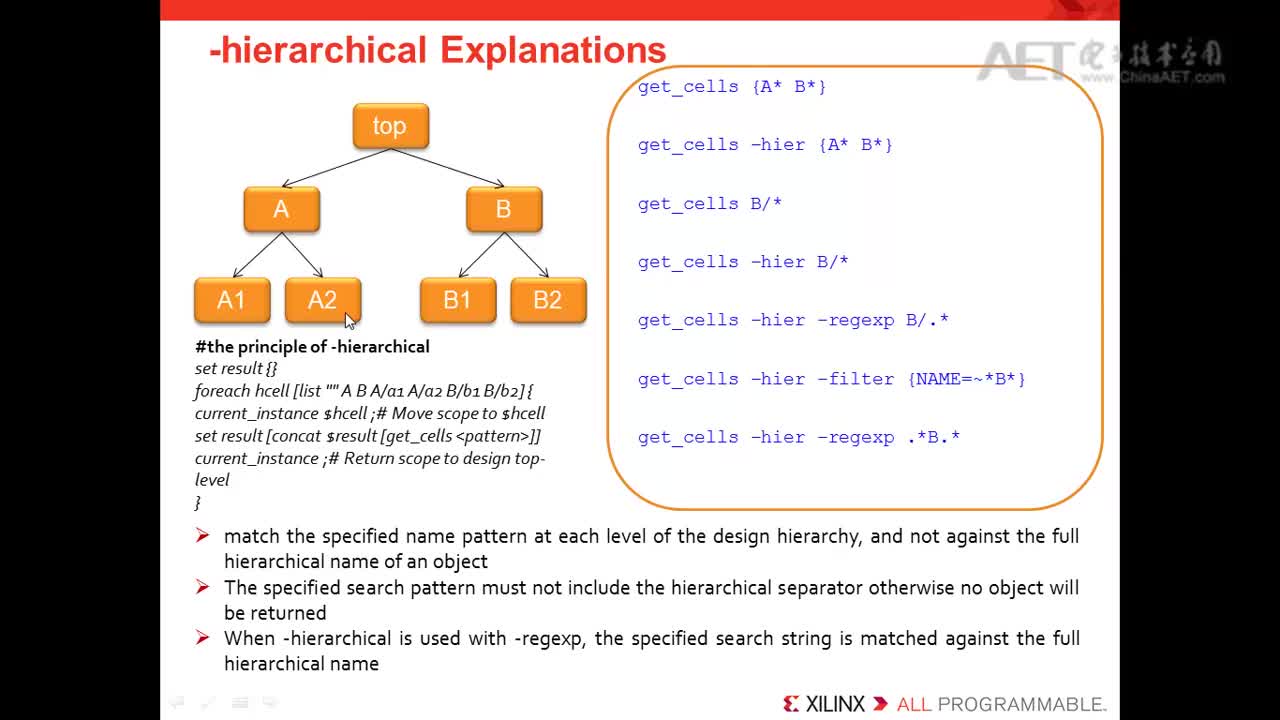

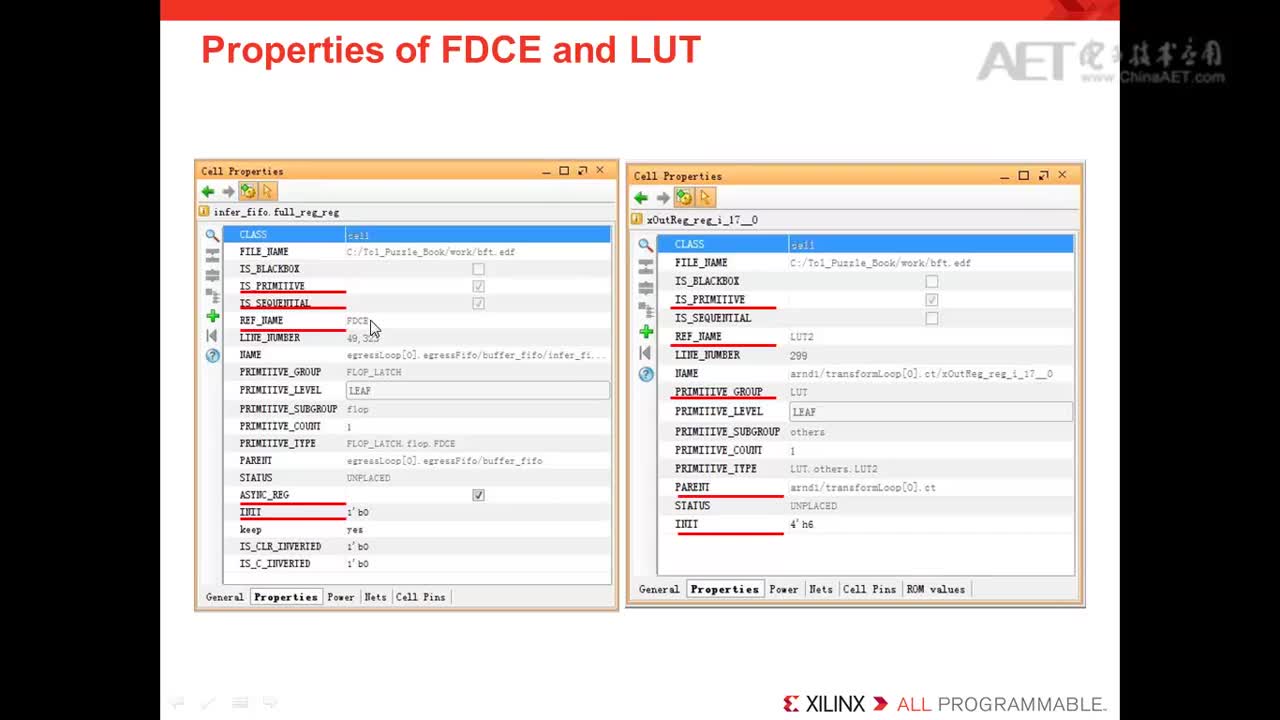

get_cells/get_nets

get_pins

以上只是简单介绍了几个Tcl在Vivado中的应用,还有很多很多方面Vivado的开发都不得不借助Tcl脚本,像XDC约束文本,等等。在一些“高级”应用中,像包括ECO、PR、HD Flow等等都是从Tcl脚本方式开始支持。

所以在目前的FPGA开发模式中Tcl是一个绕不开的语言,同时其特点也让FPGA开发更完美。

FPGA便捷开发-TCL商店

Vivado在设计中集成了很多基础的Tcl命令,所有的命令及作用都在Xilinx官方文档UG835中,下面是链接(浏览器打开即可阅读):

❝

https://www.xilinx.com/content/dam/xilinx/support/documentation/sw_manuals/xilinx2021_2/ug835-vivado-tcl-commands.pdf

但是,一旦遇到自己想要的功能(比如:获取MMCM/PLL信息),但是Vivado中没有集成进去怎么办?

今天的主角就闪亮登场了(铺垫够久了)-开源项目XilinxTclStore

❝

https://github.com/Xilinx/XilinxTclStore

方面下载链接(后面都会提供):

❝

https://gitee.com/mirrors_Xilinx/XilinxTclStore

简介

Tcl Store 是 Tcl 代码的开源存储库,主要用于 Xilinx Vivado 设计套件。应用程序是由所有者发布和维护的一个或多个 Tcl 脚本的组或集合。应用程序所有者充当该代码的看门人,我们只接受所有者对应用程序的贡献。此外,整个存储库由 Xilinx 官方管理,它控制对公共存储库的推送和审核。

更多的介绍可以看下下面的视频(带字幕):

项目的WIKI界面有更详细的介绍:

❝

https://github.com/Xilinx/XilinxTclStore/wiki/Xilinx-Tcl-Store-Home

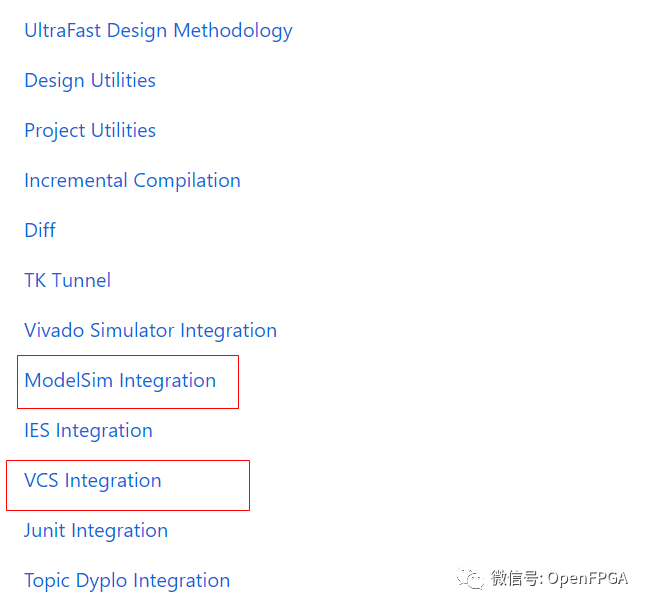

目前支持的几大部分如下:

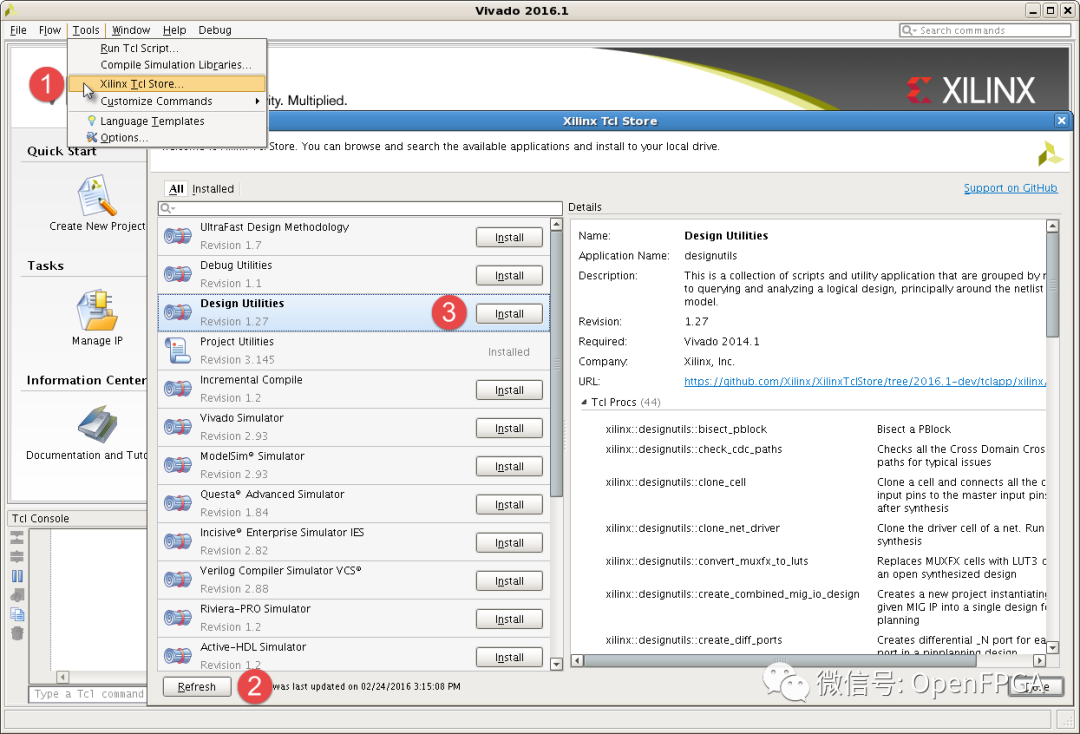

使用

其实整个开源项目主要目的是可以大家集思广益对项目做贡献,使用时非常简单的,只需要两三步即可完成:

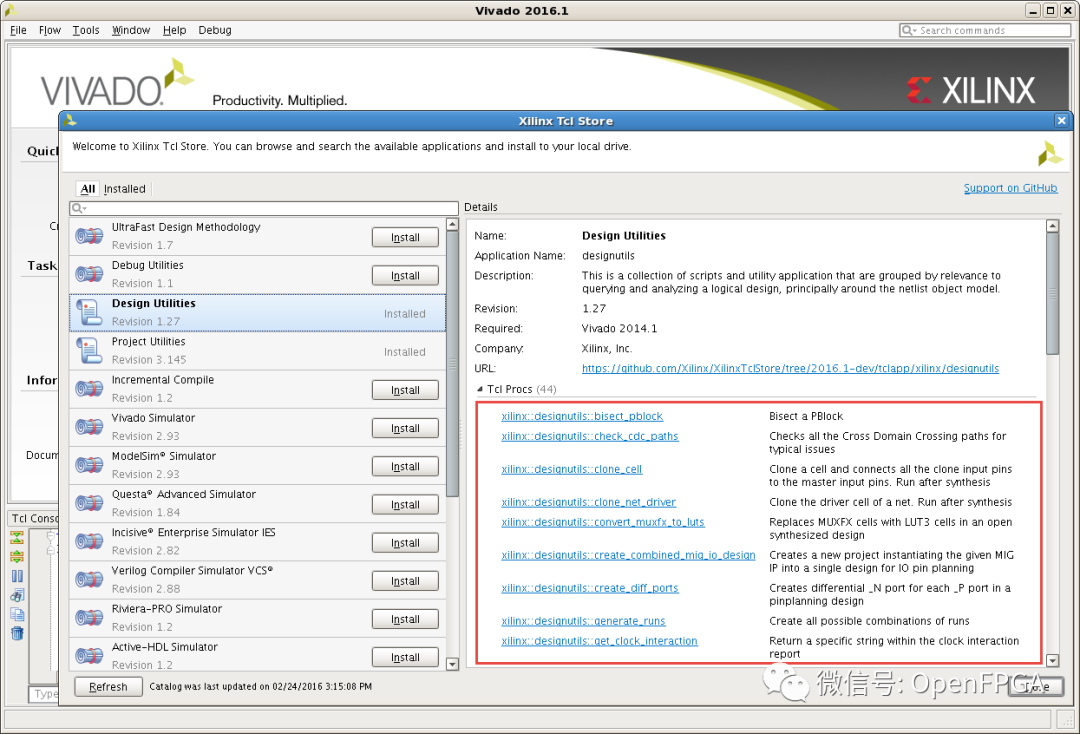

Vivado界面:Tool--> Xilinx Tcl Store,点击Inatall即可安装:

安装程序后,将报告应用程序中可用的 Tcl proc 列表以及一行摘要。

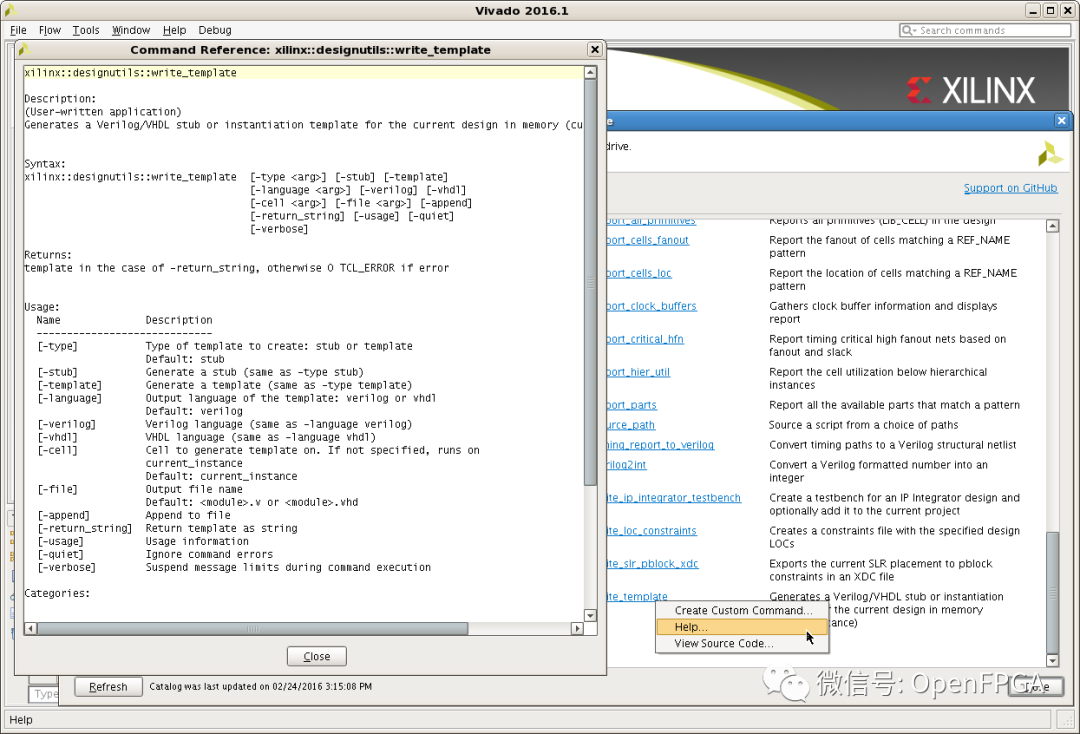

安装程序后,proc 名称将更改为超链接。单击任何 proc 名称会打开一个带有帮助菜单项的上下文窗口。选择帮助会打开所选过程的嵌入式帮助信息。

安装程序后,可以通过两种不同的方式访问属于该应用程序的所有 proc:

来自<::myapp 命名空间>。当 Vivado 启动时,会自动为<::myapp 命名空间>下所有已安装应用程序的所有 proc 创建一个入口点(包装器)。 从定义 proc的应用命名空间<::myapp>中。

上面说的有点绕口,其实就在安装完成就有一个命令,如下(以designutils为例):

圆圈中的命令就可以直接在Tcl中运行

上面就是方式一的调用方式。还有方式二不常用就举例如下:

vivado>::add_probe vivado>::add_probe

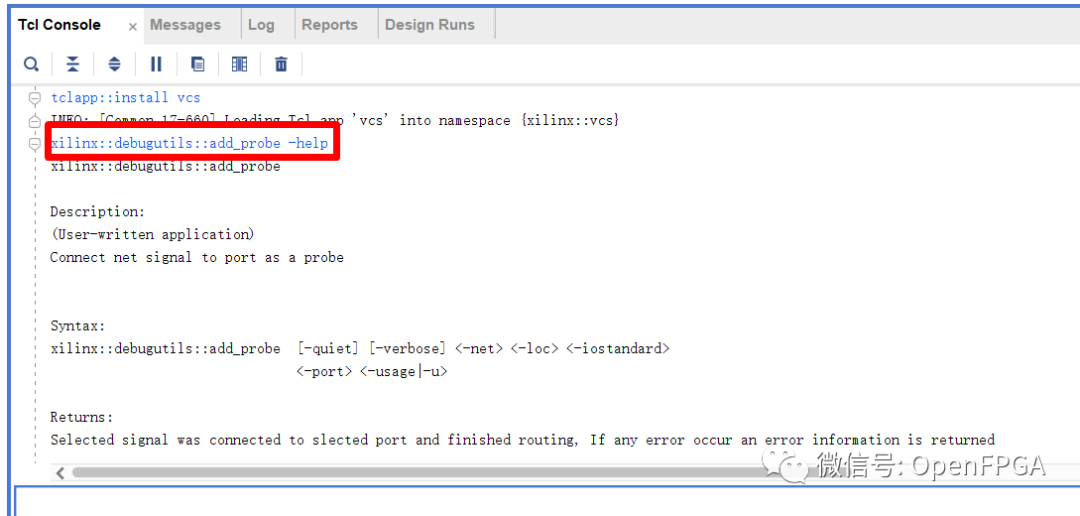

方式一常用的原因是可以带一些默认参数,例如 -help、-verbose 和 -quiet

vivado>::add_probe-help

使用比较简单,一些命令很有用,比如在ila中插入一个PROBE,当然可以结合自己的使用习惯建一些常见的Tcl命令。

关于怎么提交自己的代码,可以看下这个项目的WIKI,讲解的很详细。

总结

今天介绍的项目,应该是方便、便捷大家开发FPGA的开源项目,对于一些不怎么常用Tcl的用户,可以慢慢学起来了,因为从目前看,一些高级的调试技巧都是从Tcl出发的。

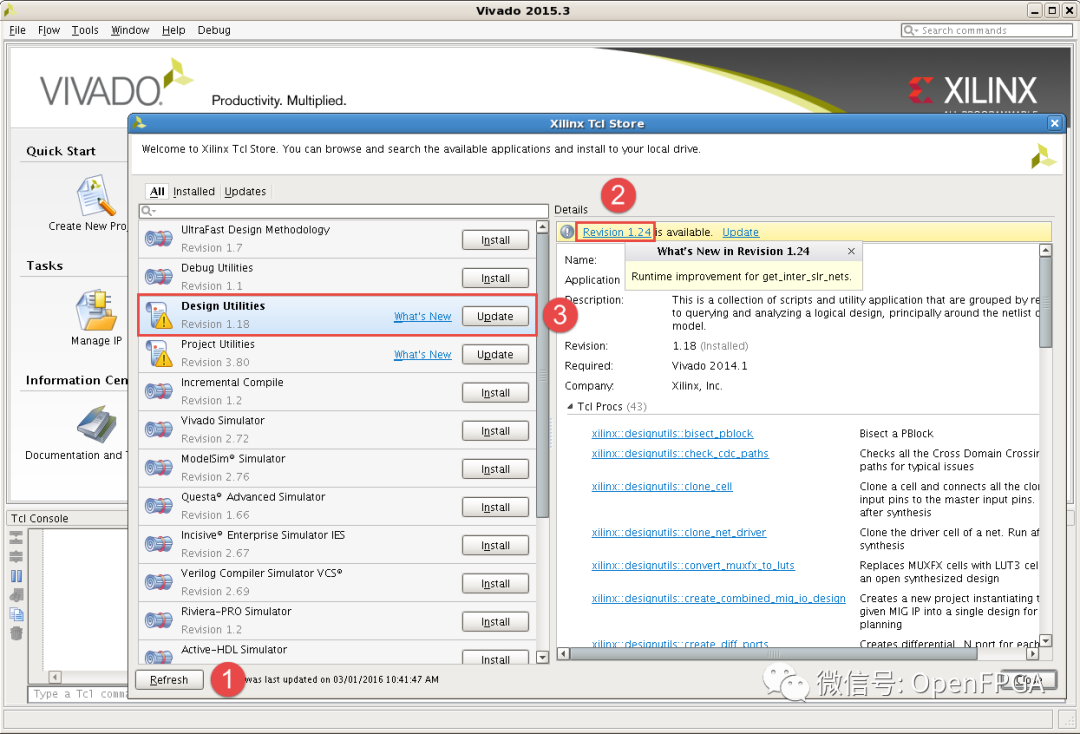

整个项目使用也是异常简单的,而且注意实时更新,因为官方会经常更新一些命令,对于一些比较成熟的项目,官方会集成到新的EDA工具中,更新方法如下:

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

审核编辑 :李倩

-

FPGA

+关注

关注

1638文章

21857浏览量

609745 -

IC

+关注

关注

36文章

6036浏览量

177360 -

开源

+关注

关注

3文章

3492浏览量

43083

原文标题:FPGA便捷开发-TCL商店(开源)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

#硬声创作季 #FPGA Xilinx开发-08 Vivado里最常用的5个Tcl命令-1

#硬声创作季 #FPGA Xilinx开发-08 Vivado里最常用的5个Tcl命令-2

FPGA便捷开发-TCL商店(开源)

FPGA便捷开发-TCL商店(开源)

评论