DDR仿真作为一个非常普遍的仿真模块,基本上入门SI行业的人都会首先接触到。记得本人刚接触这个行业的时候,也是先接触DDR模块的仿真。从DDR2到DDR4,可能很多同行都一直使用同一套的仿真方法,就是先提取无源链路(RLC链路或者S参数),再加入有源的模型(例如IBIS模型),然后码型跑起来,芯片驱动接收配置调起来就能看到扫描的结果。

有源的模型这个没什么好说的,就摆在这里,我们也只能管管模型对不对。那我们说说提取链路的无源参数吧。我们以DDR4的数据信号(2400Mbps)为例来说明。我们看到2400Mbps,大家都知道该速率对于的最高码型的频率为1200MHz,也就是我们所说的基频。那我们在提取链路的S参数时,是不是只需要提取到1200MHz就好了呢?

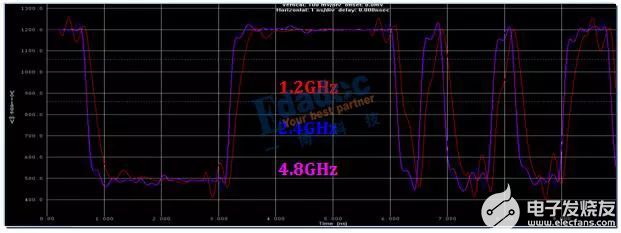

我们首先来看看提取到下面三个频率后加入有源模型的波形差异。

信号波形如下所示:

可以看到提取到不同的频率对波形的差别很大,尤其在1.2GHz和2.4GHz的差别,几乎上升/下降沿都对不上,而2.4GHz和4.8GHz时在稳定电平上的波形也有不小的差异。

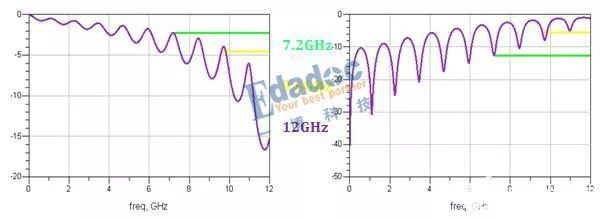

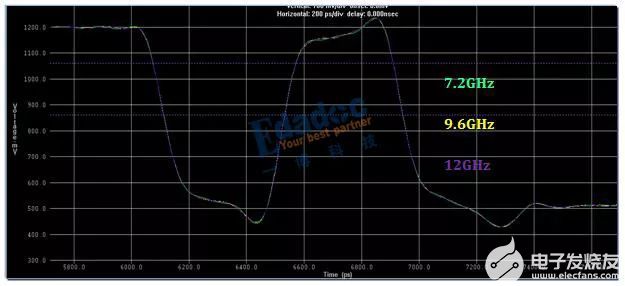

那我们再提取更高的频率看看,如下:

然后我们再来看看波形结果,可以看到在这几个频率下,无论是沿还是稳定电平的振荡情况都比较接近,区别不大了。

看来我们提取无源参数的时候还真不能只按照基频来提取。

-

DDR4

+关注

关注

12文章

321浏览量

40792 -

有源

+关注

关注

0文章

123浏览量

22664 -

数据信号

+关注

关注

0文章

58浏览量

11971

发布评论请先 登录

相关推荐

DDR5内存与DDR4内存性能差异

DDR内存频率对性能的影响

如何选择DDR内存条 DDR3与DDR4内存区别

锁相放大器的频率怎么选

什么是DDR4内存的工作频率

DDR4内存频率最高多少

DDR4时钟频率和速率的关系

calibre后仿真参数提取

为什么多片DDR菊花链拓扑连接时末端需要接很多的电阻

DDR终端匹配电阻的长度多少合适?

DDR仿真需要提取到多少频率?

DDR仿真需要提取到多少频率?

评论