系统总览

RapidIO标准分为三层:逻辑,传输和物理。

逻辑层定义整体协议和数据包格式。这是端点启动和完成事务(transaction)所必需的信息。

传输层提供数据包从端点移动到端点所需的路由信息。

物理层描述了设备级接口细节,例如数据包传输机制,流控制,电气特性和低级错误管理。

这种划分提供了将新事务类型添加到逻辑规范的灵活性,而无需修改传输或物理层规范。

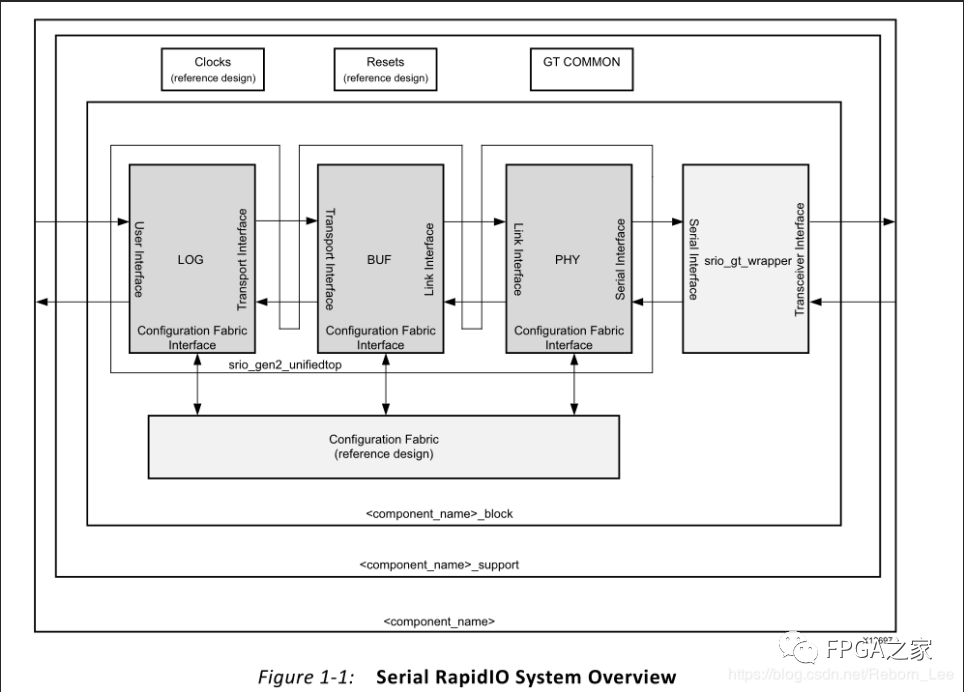

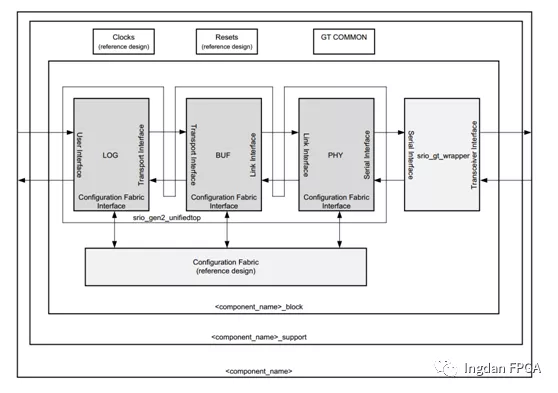

下图是FPGA端 SRIO IP核系统总览图:

从图中可以看出:

The SRIO Gen2 Endpoint is comprised of the following:

• A Serial RapidIO Gen2 top-level wrapper (srio_gen2__unifiedtop) containing:

Serial RapidIO Gen2 Physical Layer (PHY)

Serial RapidIO Gen2 Logical (I/O) and Transport Layer (LOG)

Serial RapidIO Gen2 Buffer Design (BUF)

• Reference design for clocking, resets, and configuration accesses

图中的层次结构如下:

The srio_gen2__unifiedtop wrapper contains the LOG, BUF, and PHY.

The _block integrates the srio_gen2__unifiedtop wrapper, the srio_gt_wrapper, and configuration fabric reference design.

The _support wrapper contains the clock and reset modules.

is the top-level wrapper. This wrapper is used to integrate an entire SRIO Gen2 Endpoint into your design.

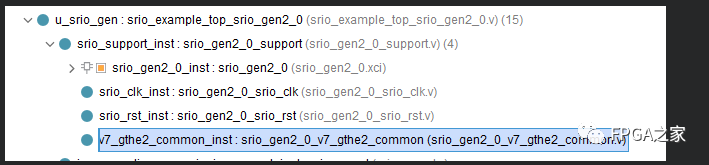

上面的这张图的关系,也可以通过IP提供的例子程序的层次结构窥见一二:

Top-Level Wrapper

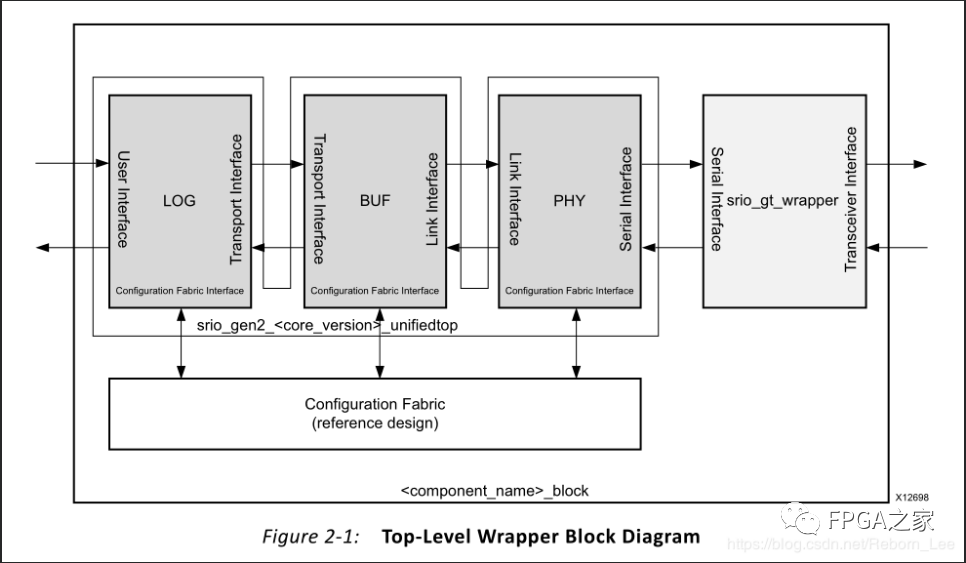

如下图为顶层封装原理图:

_block模块捆绑了SRIO Gen2端点的每个组件,包括参考设计,以提供围绕其设计的打包解决方案。图2-1提供了 _block模块每个部分的基本框图,以及 _block设计的每个部分之间的数据交互的一般视图。

Port Descriptions

Logical Layer Interfaces

The LOG has three interfaces:

• User Interface

• Transport Interface

• Configuration Fabric Interface

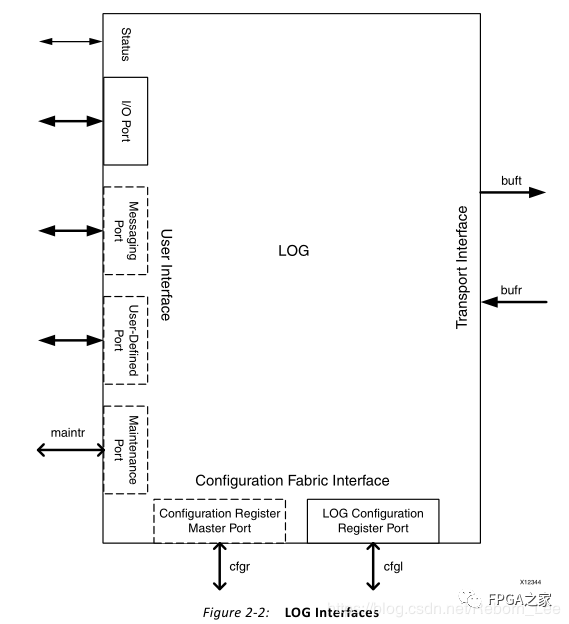

如下图为逻辑层接口的详细视图:

Figure 2-2 shows the ports associated with each of the LOG interfaces.

上图中,实箭头表示AXI4-Stream ports,空箭头为AXI4-Lite ports;

这两种端口的区别?自行了解。

用户端口包含可以发出或使用数据包的端口。生成IP核时,可以配置与每个端口关联的端口数和事务(Transaction)类型。还可以从这些端口启动配置读和写访问到驻留在此 SRIO Gen2 终结点设备中的配置寄存器或远程设备。这些接口通过Serial RapidIO包装器输出,用于数据包生成和使用。

传输接口包含两个端口,接收和发送,旨在与RapidIO兼容的物理层或缓冲应用程序连接。此接口在包装器模块外部是不可见的。

配置结构接口包含两个端口:

• Configuration Master port,通过Configuration Fabric发出对本地配置空间的读写。

• LOG Configuration Register port,它是一个从接口,用于读取和写入任何配置寄存器,这些寄存器定义为逻辑或传输层的一部分。

配置结构解码来自配置总线主机的读或写地址,并将它们传递到LOG,PHY和BUF的配置寄存器端口。此交互完全保留在 _block模块中。

User Interfaces

上面说的逻辑层的端口分为用户端口、传输端口以及配置端口,这里来细看下用户端口:

The user interface contains a set of I/O ports and the following optional ports:

• Messaging Port

• Maintenance Port

• User-Defined Port

每种事务(transaction)类型都分配给特定端口。通常,在I / O端口上发送或接收任何支持的I / O事务,例如NWRITE,NWRITE_R,SWRITE,NREAD和RESPONSE(不包括MAINTENANCE响应)。MESSAGE事务(如果支持)可以分配给Messaging端口或I / O端口。无论消息端口是否存在,DOORBELL事务都使用I / O端口。如果启用了维护(maintenance)端口,则维护端口上应支持所有维护数据包。如果事务是用户定义的,不受支持的类型,或者没有分配的端口,则它使用用户定义的端口(当禁用用户定义的端口时,将丢弃与另一个端口不对应的接收数据包)。

I/O Port

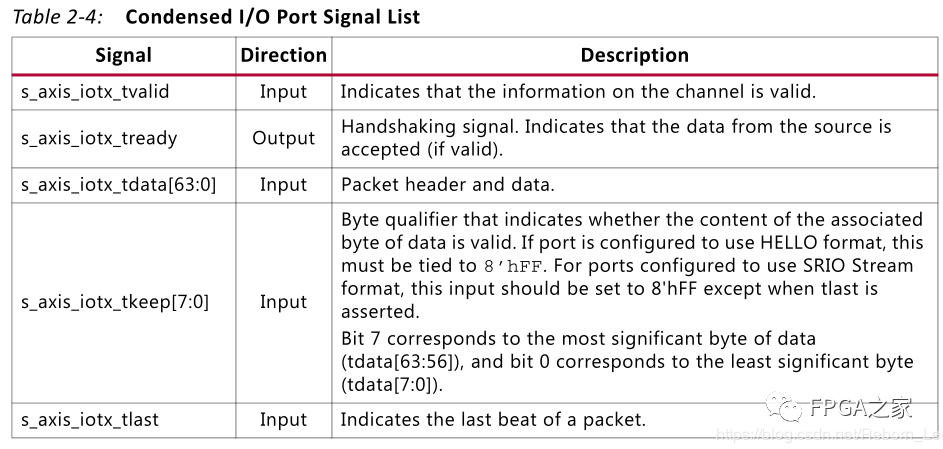

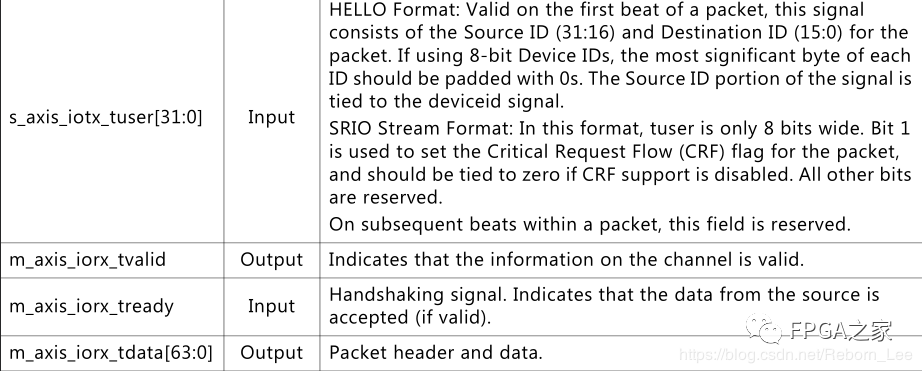

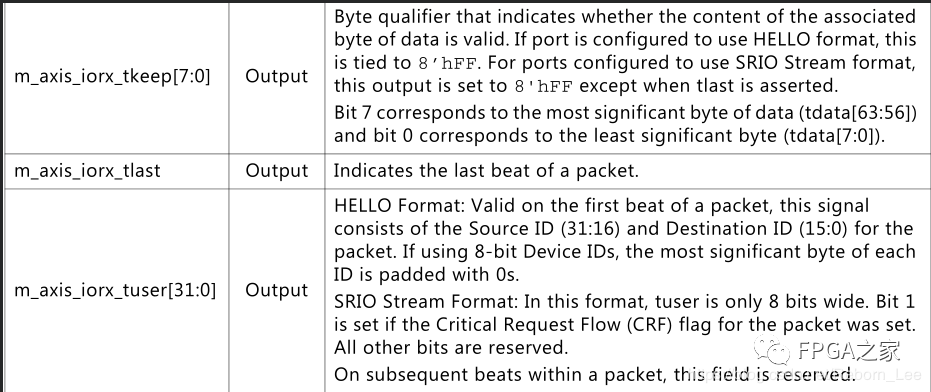

I / O端口可以配置为两种样式之一:Condensed I/O or Initiator/Target. 。可用信号取决于IP核生成期间选择的样式。

The I/O port is built from AXI4-Stream channels,有两种数据包格式:

• HELLO

• SRIO Stream

I / O端口中的所有通道必须使用相同的数据包格式,该格式在生成核心时选择。

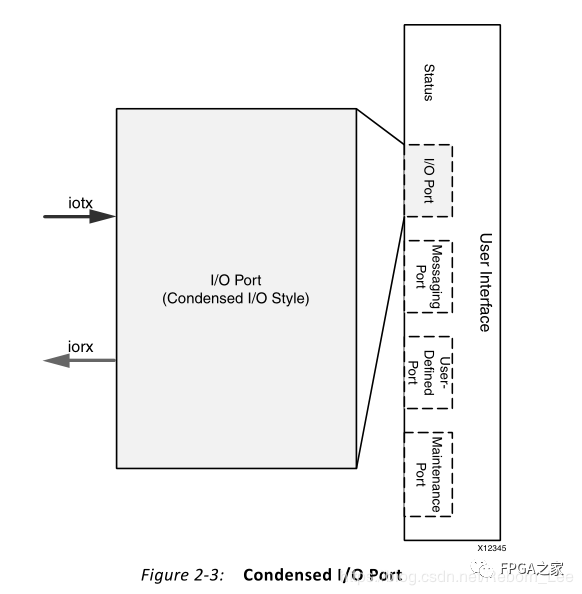

Condensed I/O

The Condensed I/O 样式减少了用于传输和接收I / O数据包的通道数。有一个AXI4-Stream通道用于传输与I / O端口(iotx)相关的所有数据包类型。类似地,有一个信道用于所有接收的I / O端口数据包(iorx)。图2-3显示了Condensed I / O端口。

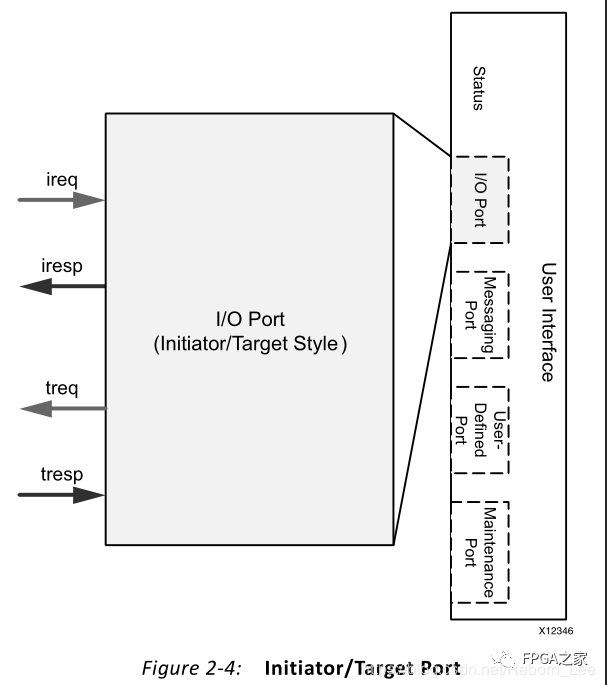

Initiator/Target

Initiator / Target端口样式允许将针对远程设备(放置在Initiator端口上)的事务与针对本地端点(放置在Target端口上)的事务分离。

由本地端点(local endpoint )生成的请求被置于要在链路上传输的启动器请求(ireq)信道上。从远程设备接收的响应在发起者响应(iresp)信道上呈现给用户设计。

这句话还是原文比较好理解:

Requests generated by the local endpoint are placed on the Initiator Request (ireq) channel to be transmitted on the link. Responses received from a remote device are presented to the user design on the Initiator Response (iresp) channel.

Requests originating from a remote device which are received by the core are presented to the user design on the Target Request (treq) channel. Responses to these requests, which are generated by the user design, are placed on the Target Response (tresp) channel.

意思是本地设备的请求信号在ireq channel上,对应的远程设备的响应在iresp channel上。

而远程设备的请求在treq上,对应的本地响应在tresp上。

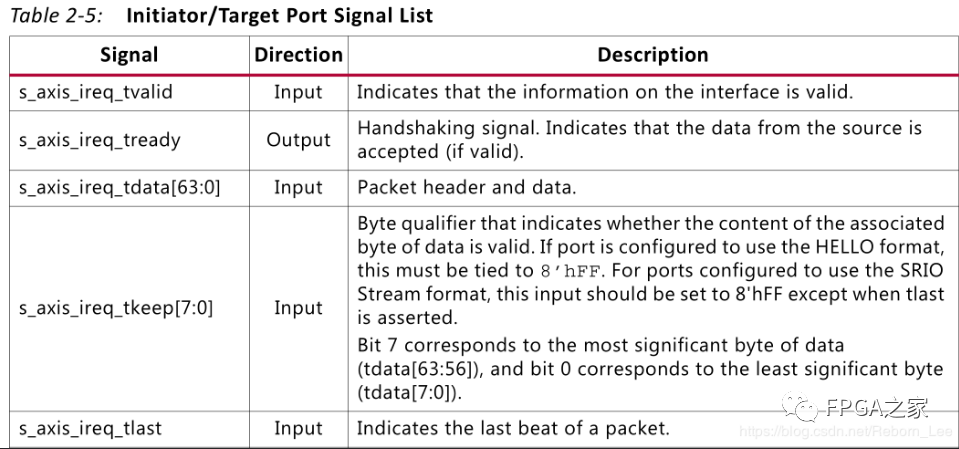

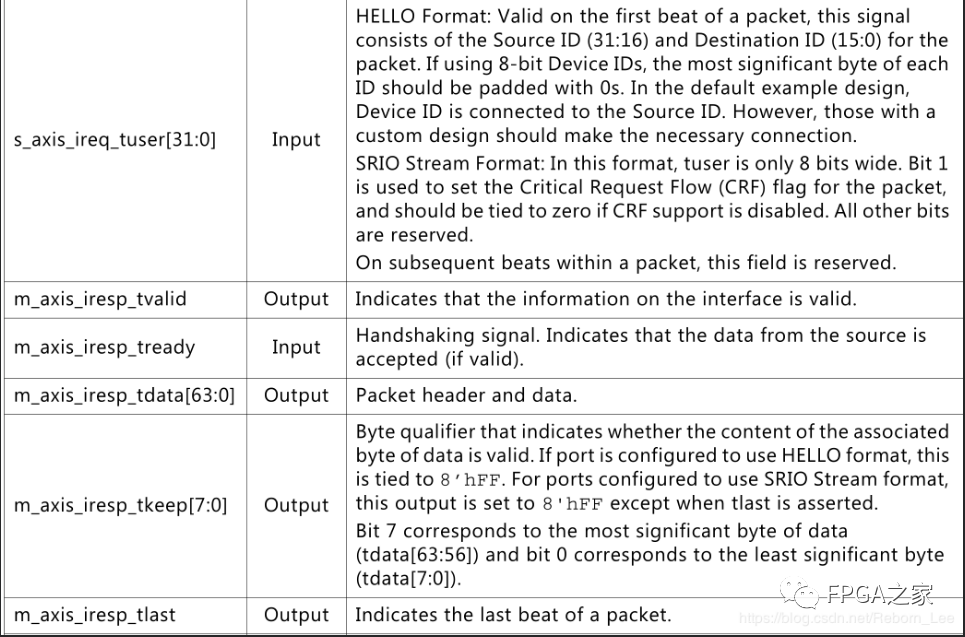

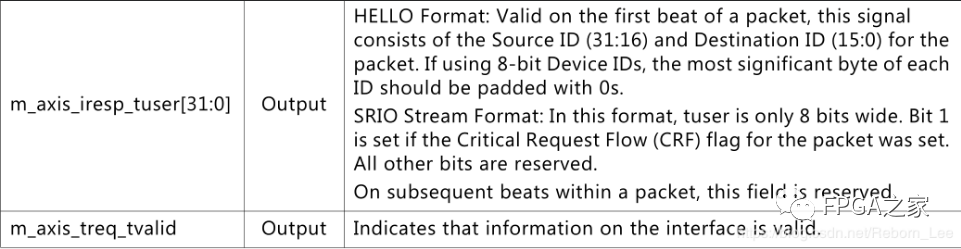

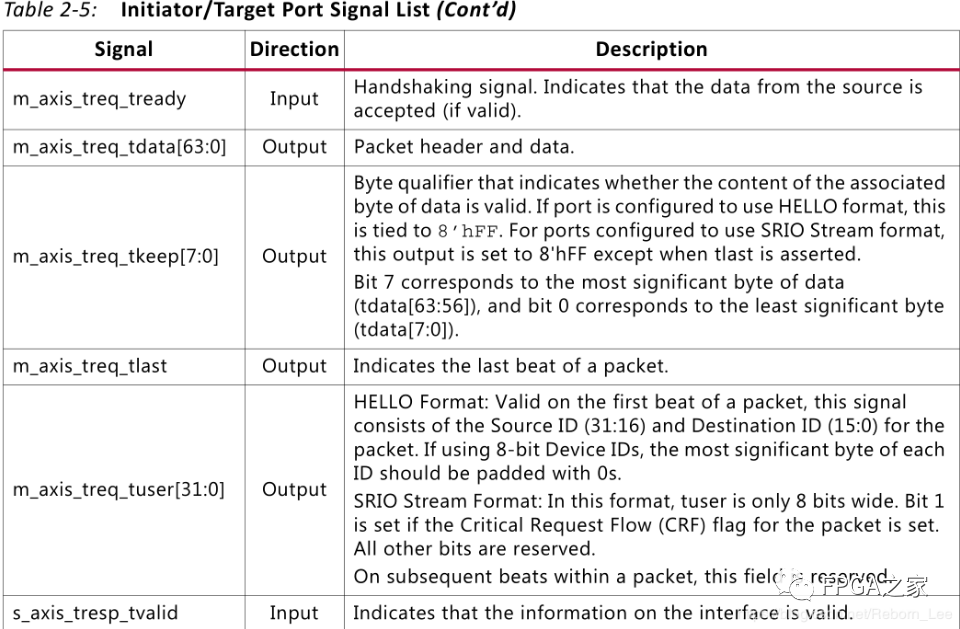

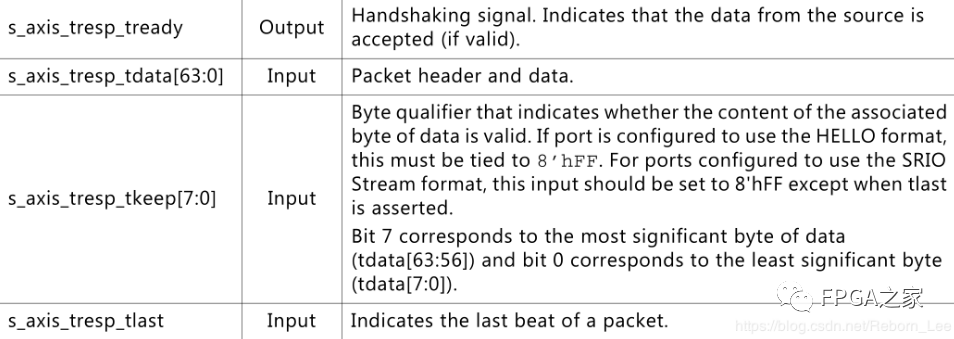

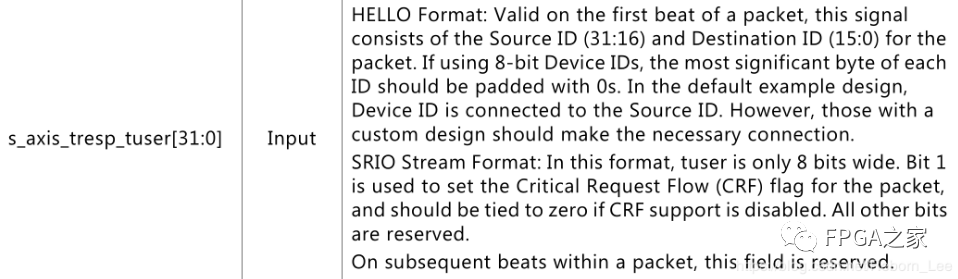

Table 2-5 shows the signals associated with the Initiator/Target port. At the level, the following signals are associated with these interfaces:

• s_axis_ireq* are associated with INITIATOR_IREQ.

• m_axis_iresp* are associated with INITIATOR_IRESP.

• m_axis_treq* are associated with TARGET_TREQ.

• s_axis_tresp* are associated with TARGET_TRESP.

好,这篇博文到这里,至于通俗的解释(说人话),我会随着我的理解不断加深而更新。

下篇博文继续讲Messaging端口等。

原文标题:【FPGA】SRIO IP核系统总览以及端口介绍(一)(User Interfaces 之 I/O Port)

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1625文章

21642浏览量

601397 -

端口

+关注

关注

4文章

951浏览量

31993 -

IP核

+关注

关注

4文章

326浏览量

49394

原文标题:【FPGA】SRIO IP核系统总览以及端口介绍(一)(User Interfaces 之 I/O Port)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA IP核的相关问题

请问用c6678 srio收发地址位数,DSP端keystone_srio的程序要做什么改进?

FPGA实现基于Vivado的BRAM IP核的使用

Xilinx SRIO IP介绍和使用经验分享

【FPGA】SRIO IP核系统总览以及端口之Messaging Port介绍

FPGA端SRIO IP核系统总览及端口介绍

FPGA端SRIO IP核系统总览及端口介绍

评论