绪论

在计算机与电子产品的世界中,我们习惯于通过两种截然不同的方法实现计算:硬件以及软件。计算机硬件,比如专用集成电路(ASIC),为关键任务提供了运算快速与资源高度优化的方案。但是 ASIC 一旦设计与加工完成,这其中需要花费数以百万美元的成本与大量努力,就只能永久性地配置为单一应用的解决方案。计算机软件可以灵活地改变应用,可以进行大量不同的计算任务。但是软件相比 ASIC 硬件实现,在性能、硅片面积效率以及功耗等方面的表现有数量级的差距。

现场可编程逻辑门阵列(FPGA)是一种真正意义上的革命性器件,融合了软件与硬件各自的优势。FPGA 所实现的电路与专用硬件相似,提供远超软件的功耗、面积以及性能。而且,能够轻易并低成本地重新编程,以适应范围广泛的、不同的计算任务。与专用计算硬件一样,FPGA 能够利用空间上分布于整个芯片的资源并行数以百万计的运算,相较于软件所基于的通用处理器,速度运算最高可以快上百倍。然而,与 ASIC 不同的是,这些运算任务是编程到 FPGA 器件中的,而不是像 ASIC 一样是在生产中固化的。这意味着基于 FPGA 的系统可以多次编程或者重编程(reprogrammed)。

有时,重编程可用于修复系统的错误行为,或者用于添加新的功能。而有时,FPGA 也可通过重编程转换为一个为新运算任务量身设计的计算引擎。利用在运行过程中的可重编程特性,单个 FPGA 芯片甚至能够实现多块专用芯片的不同功能。

但确实,FPGA 实现软硬件两者的优势并不是没有代价的。FPGA 几乎具有软件所有的灵活性优势以及可以使用软件开发模型,并且具有接近硬件的高效率优势——但无论是相比软件还是硬件,FPGA 实现还是有差距。相较于运行软件的通用微处理器,FPGA 的性能与功耗效率最高可比前者要高上几个数量级,但是高效的 FPGA 系统开发过程要复杂的多。通常来说,FPGA 只适合于处理以较长数据流为输入的运算,比如信号处理、网络以及其他数据流应用。相较于 ASIC,FPGA 在面积、延迟以及性能方面有 5-25 倍的差距。然而, 单个 ASIC 设计需要数个月到几年的时间,花费几百万美元,FPGA 开发则仅需几天,成本在几十至几百美元之间。(译注:通常这个说法适用于 FPGA 实现单一功能,而不是整个系统,后者的开销无疑会更高)对于那些不需要极高性能或者效率的系统来说,FPGA 实现是一个更吸引人的方案,因为 FPGA 方案开发更为简单,并可通过可重编程特性轻松地修复缺陷与添加功能。对于许多任务,尤其是对初学的电子开发者来说,FPGA 是一种理想的选择。

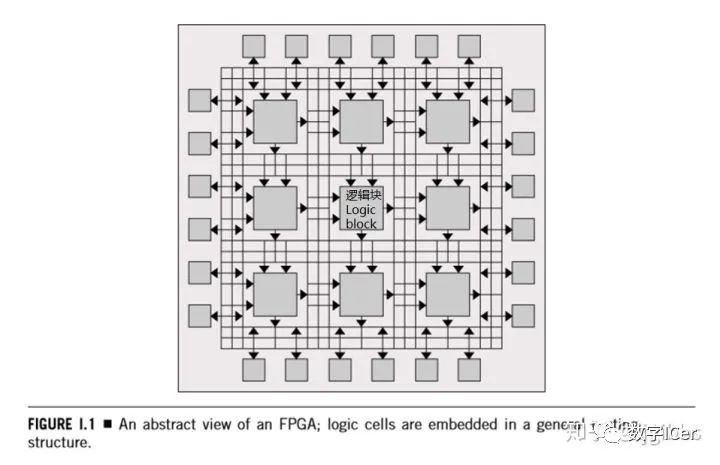

图 I.1 FPGA 内部结构抽象;逻辑块(内部大方块)嵌入在通用布线结构中

图 I.1展示了 FPGA 的内部构造。其内部由逻辑块组成,逻辑块嵌入在一个通用的布线结构中。逻辑块可实现基础逻辑门(Gate),大量逻辑块排列成阵列(Array),这就是 FPGA 中的 ‘G’ 和 ‘A’ 的由来。逻辑块由处理单元与触发器构成,分别用于实现组合逻辑与时序逻辑。处理单元是一小块存储空间,可实现任意的五输入或者六输入的布尔函数。(译注:处理单元即为查找表(LUT),输入数量取决于具体器件)通用布线结构支持逻辑块端口间任意的连线,所以各个逻辑块可以按开发者设想的顺序连接。

得益于 FPGA 的通用性与灵活性,可以实现非常复杂的电路。目前的 FPGA 器件可以实现百万门(译注:电路中的组合逻辑电路规模等效于百万个基础逻辑门,如与非门)电路,工作频率达到上百MHz(译注:一般在300MHz以下)。为了提高电路的速度以及规模,FPGA 在逻辑块阵列的基础上增加了一些特别的单元,比如大规模的存储块(BRAM)、乘法器、快速进位链(fast-carry)甚至加入整个微处理器单元。(译注:还有以太网控制器、DDR控制器以及高速总线的串行收发器,这些单元都是固化电路,不可编程的)通过这些预先定义并固化在硅片上的额外单元,单片 FPGA 便有能力构成整个完整的系统。

FPGA 中的逻辑以及布线单元的可重构由编程节点控制(programming points),基于反熔丝(antifuse)、SRAM 或者 FLASH 技术,一般来说 SRAM FPGA 对于可重构计算是一个适宜的选择,SRAM 也是目前商用 FPGA 的主流技术。在 SRAM FPGA 中,每个布线或者逻辑单元的功能都由存储于 SRAM 介质中的内容决定。整个器件中的 SRAM 内容可通过一个配置文件或者比特流(bitstream)进行配置,编程为用户定义的功能。因此,整个配置过程可以快速地进行,并且不需要一些固化步骤。(译注:SRAM 的写入擦除均十分快速且易于进行)开发者能够很方便地在自己的工作台上对器件进行编程。哪怕 FPGA 器件已经安装于终端产品中,编程也十分容易进行。这就是为什么 FPGA 会被称为现场可编程(Field programmable)的原因,并区别于那些仅在生产时可编程的掩膜可编程(mask programmable)器件,这些器件的可编程只能在产线上通过相应设备进行,无法在客户现场完成。

译注:Field programmable 指产品出了问题,带着电脑去用户现场调试,干过这事儿都懂:苦差啊。

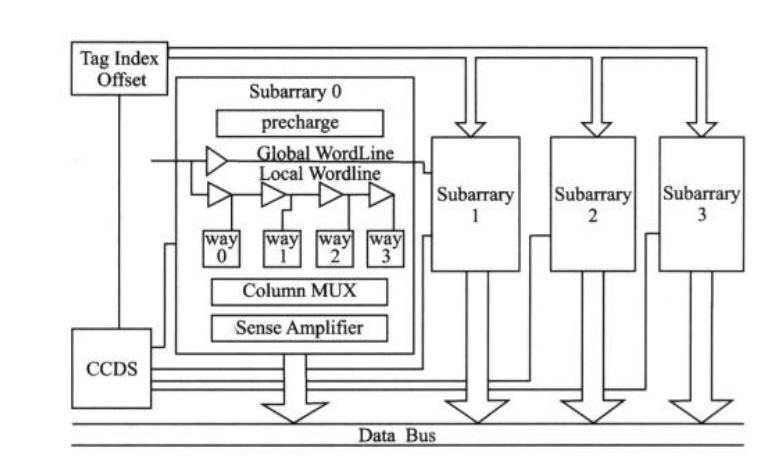

因为 FPGA 的定制只需要将相应的内容写入到片上的存储中,因此和编译、然后将程序加载到计算机中运行这一软件开发流程相似。FPGA 相对应的流程是创建与 FPGA 电路对应的比特流、然后将比特流写入到器件中(可见图 I.2)。尽管有多种建立 FPGA 电路的方法,可以借助工具将软件代码(译注:HLS)、原理图或者其他格式的数据转换为电路。FPGA 开发者一般还是通过硬件描述语言(HDL,Hardware description language)来构建一个应用,比如 Verilog 和 VHDL。由 HDL 描述的电路经过一系列步骤转换为可映射至 FPGA 器件的逻辑,这些步骤包括:

逻辑综合(logic synthesis),将高级语法以及行为级描述,转换为逻辑门网表。

工艺映射(technology mapping ),将若干逻辑门为划分至一个逻辑组,并将逻辑组高效地映射于 FPGA 的逻辑资源。

布局布线(placement & routing,P&R),将逻辑组指定至器件上某个具体的逻辑单元,并按照用户定义连接各个逻辑单元之间的端口。

生成比特流(bitstream generation),将布局布线后的信息生成为一个二进制文件,用于恰当地配置器件逻辑单元与布线资源。

在设计编译完成后,我们可以通过比特流将 FPGA 器件编程为对应于某个计算应用的平台。一般通过主机上的处理器完成比特流的下载工作。或者可以将预先编程完成的存储介质连接至 FPGA 的配置管脚。无论如何,FPGA 在每次上电之后都需要读取比特流进行配置。或者在运行时,用户可以按需控制器件重新下载比特流进行重配置。一旦 FPGA 配置完成,那么就会像一个具有特定功能的数字电路一样工作。

因为 FPGA 同时具有软件灵活性与硬件高性能两项特性,FPGA 开发者的思路需要区别于纯粹的软件或者硬件开发者。软件开发者一般开发串行执行的程序,最大化利用微处理器的性能,来执行一系列的指令

译注:假设程序员只有一个单独的处理核,并且目标运算的指令数量固定。软件程序员的目标就是降低相同数量指令的执行时间,换句话说,减少微处理器的等待时间。

但是在高质量的 FPGA 设计开发中需要考虑空间的并行性,即使用芯片上的多路资源并行计算,尽可能地减少运算整体时间。

译注:假设资源是无限的,对于目标运算,FPGA开发者的目标是尽可能实现指令的并行,将指令尽可能地分配到多个并行处理单元上。

对于 ASIC 等硬件开发人员来说,因为会从硬件电路实现出发,所以在硬件设计中具有一定优势(译注:在设计阶段实现更好的 PPA,Performance/Power/Area)。但是 FPGA 的灵活特性能够给开发者带来 ASIC 或者其他固化器件设计中不存在的新机遇。FPGA 设计可以更快地进行新功能的迭代和部署,甚至在现场重新编程。因此,FPGA 设计不需要 ASIC 开发那么大规模的设计团队,所需的验证工作也会更少 。此外,FPGA 的动态可重编程特性使一些设计成为可能。比如,在运算过程中设计可以根据当前的外部需求的动态改变重编程,动态地优化自身的结构。或者通过定时对自身功能进行重构,在小型的器件上时分复用功能,实现规模更大的设计。但是有一点,FPGA 相比 ASIC 运行速度要低得多,并且容量也小得多,设计者需要细致地对设计进行优化,以契合目标器件。

图 I.2 典型的 FPGA 开发流程示意图

FPGA 是一项拥有独立机遇以及挑战的器件,是一个非常灵活的硬件平台。本书《可重构计算:可重构计算的原理与实践》旨在介绍基于 FPGA 平台的各个方面,这些方面可能是积极的,也有可能是面临问题的,本书主要包括 6 个部分:

第一部分介绍硬件器件,包括 FPGA 以及那些为可重构专门优化的器件(章 1-4)

第二部分关注可重构计算平台的编程实现,包括编程语言以及编程模型(章 5-12)

第三部分关注 FPGA 开发流程的软件,包括图 I.2 中每个步骤的详情(章 13-20)

第四部分关注面向应用的 FPGA 设计,讨论范围包括:如何最高效地利用器件的逻辑资源(章21-26)这部分可以认为是 FPGA 开发者的最后一课了,因为学完的读者应该已经完全掌握了 FPGA 开发与软件编程、ASIC 设计之间的区别。

第五部分是一系列案例学习,阐述了可编程器件在各领域的应用(章27-35)

第六部分包括了一些进阶主题,比如可重构计算的理论模型以及衡量标准。此外还包括了可重构的缺陷、容错(fault tolerance)等主题以及可重构计算与纳米技术之间潜在的协同作用。(章36-38)

在完成了所有 38 个章节的阅读后,读者会发现 FPGA 当前存在一些重大挑战。但更重要的是,可重构器件为计算科学带来的独特机遇与收益将远超为了克服这些挑战所付出的努力。

原文标题:可重构计算:基于FPGA可重构计算的理论与实践

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1635文章

21836浏览量

608294 -

计算

+关注

关注

2文章

452浏览量

38953 -

可编程逻辑

+关注

关注

7文章

517浏览量

44299

原文标题:可重构计算:基于FPGA可重构计算的理论与实践

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA的重构方式

基于FPGA的可重构系统结构分析

【悬赏100块】如何实现FPGA可重构计算(Android平台)

可重构计算(Reconfigurable Computing)

可重构技术分析及动态可重构系统设计

基于FPGA硬件平台的可重构系统调度算法详解

可重构和自适应计算:理论与应用

可重构计算:基于FPGA可重构计算的理论与实践 1.器件架构 译文(一)

基于FPGA的可重构计算平台设计

基于FPGA的可重构计算平台设计

评论