数字硬件建模SystemVerilog(五)-文本值

System Verilog 扩展了 Verilog 的 教据类型 , 增强了指定文本值的方法。在介绍文本值之前我们先简单回忆一下HDL中的四个状态数据值。

四个状态数据值

对于RTL建模,System Verilog使用硅中可能出现的值的四值表示。

- 0表示抽象数字低电平,没有与之相关的电压或电流。

- 1表示抽象数字高电平,无电压或电流,

- Z表示抽象数字高阻抗,在多驱动器电路中,值为0或1将覆盖Z。一些编程运算符和编程语句将Z值视为无关紧要的值。

- X表示多驱动器电路中的未初始化值、不确定值或值冲突。在某些RTL模型上下文中,综合编译器将X值视为不关心值。

0、1和Z的值是实际硅中可能存在的值的抽象。

X的值不是实际的硅值。仿真器使用X来表示物理硅在特定情况下的行为的不确定性程度,例如,当仿真无法预测实际硅值是0还是1(或三态器件的Z)时,对于综合,X值还为设计工程师提供了一种方法来指定“don’t-care”条件,工程师不关心实际硅在特定条件下是否具有0值或1值。

文本值-Literal values (numbers)

System Verilog 扩 展 了 Verilog 的 教 据 类 型 , 增 强 了 指 定 文 本 值 的 方 法。这里的Literal values是直译,即字面量或常量、文本值。在我理解来看,Literal是指某一数据类型的具体值。

文本值是整数或实数(浮点数)。SystemVerilog提供了几种指定文本值的方法,还有一些文本值的语义规则,在编写RTL模型时需要理解这些规则。

文本整数值-Literal integer values

文本整数值是一个整数,没有小数点。(IEEE 1800 SystemVerilog标准使用术语“整数文本integer literal”而不是“文本整数literal integer”),文本整数可以通过多种方式指定:

- 简单的十进制整数值

- 二进制、八进制、十进制或十六进制整数值

- 大小文本整数值

- 有符号或无符号文本整数值

仿真和综合工具都需要知道或假设文本整数值的特定特征。这些特点是:

- 值的位宽度(向量大小)

- 值的有符号性(有符号或无符号)

- 值的基数(也称为基数)

- 2-state or 4-state value

这些特征影响值的操作和赋值。

简单的十进制文本整数

文本整数值可以指定为简单的数字,如数字9,如以下代码段所示:

result=d+9;

仿真和综合将简单的文本数视为:

- 32位宽的值

- 有符号

- 十进制值

- 2态值(没有位可以是Z或X)

这些特征以及 d 的特征将影响加法的执行方式以及结果赋值的执行方式。

二进制、八进制、十进制和十六进制文本整数。可以为文本整数值指定二进制、八进制、十进制或十六进制的特定基数,该基数使用撇号(’)指定(有时称为“勾号”),后跟一个字母:b或B表示二进制,o或O表示八进制,d或D表示十进制,h或H表示十六进制。一些示例包括:

result=‘d9+‘h2F+‘bl010;

仿真和综合将未指定大小的显式基本文本数视为:

- 32位宽的值

- 无符号值(注意与有符号的简单文本整数的差异)

- 规定的基准值

- 4态值(任何或所有位可以是X或Z)

二进制值的每个位可以是0、l、X或Z;八进制值的每个3位组可以是0~7、X或Z;十进制值的每个位可以是0~9、X或Z;十六进制值的每个4位组可以是0~9、a~F、X或Z。

有符号文本整数。默认情况下,具有指定基的文本值在操作和赋值中被视为无符号值。可以通过在撇号之后和基本说明符之前添加字母s或S来覆盖此默认值。

result=’sd9+‘sh2F+‘sbl0l0;

在某些操作和赋值语句中,有符号值与无符号值的处理方式不同。后面讨论了有符号和无符号值对运算符和运算的影响。

调整文本整数的大小

默认情况下,在操作、编程语句和赋值语句中,简单文本数和指定了基数的文本数被视为32位值。此默认值不能准确表示使用其他向量大小的硬件模型。

具有特定基的值也可以指定特定的位宽度。用于表示值的位数在撇号、有符号性和基本规范之前指定:

Result=16‘d9+8‘h2F+4‘bl010;

| 笔记 |

|---|

| 当文本值的大小与赋值语句左侧的变量不同时,综合编译器和lint检查器可能会生成警告消息。这些大小不匹配警告消息可能会隐藏其他需要注意的消息。使用显式大小的文本值将防止大小不匹配警告。 |

| 最佳做法准则3-1 |

|---|

| 在RTL模型中仅使用二进制和十六进制文本整数。这些数字基在数字逻辑中具有直观的意义 |

八进制值的使用已经过时几十年了。文本十进制值很容易与其他数字混淆。

有个老工程笑话适用于这里。。。

Thereare10typesofpeopleintheworld,thosethatunderstandbinary,andthosethatdon’t

世界上有10种人,懂二进制的和不懂二进制的

不匹配的大小和值检测规则

下面的规则是编写HDL代码中最难检查的,也是大部分人不注意的!

指定一个位宽不同于表示该值所需位数的文本整数是合法的。例如:

SystemVerilog始终调整该值以匹配指定的大小。这些规则是:

- 当大小小于值的位时,值的最左边位被截断。

- 当大小大于该值的位数时,该值保持扩展。使用以下规则填充附加位:

- 如果值的最左边位为0或l,则额外的高位用0填充。

- 如果该值的最左边位为Z,则附加的高位用Z填充

- 如果该值的最左侧位为X,则额外的高位用X填充。

请注意,即使将文本整数指定为有符号整数,该值也不会进行符号扩展。符号扩展发生在有符号文本值用于操作和赋值语句时,这将在后面中讨论。

前面代码段的值调整为:

4’hFACE//截断为4’hE

16’sh8//延伸至16’sh0008

32’bZ//扩展到32’bZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZ

| 最佳做法准则3-2 |

|---|

| 在综合RTL模型之前,将lint检查程序(也称为建模规则检查器)与仿真结合使用。 |

当发生截断时,仿真器可能会报告非致命警告消息,但不需要报告警告。仿真器将无声地扩展文本值以匹配大小,而不会生成任何警告。存在在仿真中验证设计功能而未意识到尺寸/值不匹配的风险。使用lint检查器时将显示文本值中的任何不匹配。

附加文本值规则

问号(?)可以用来代替Z来表示高阻抗。在大多数情况下,字母Z是表示高阻抗的更直观的方式。然而,有些运算符和编程语句使用高阻抗值来表示不关心状态。对于这些不关心的情况,使用问号表示高阻抗会更直观。

在文本值中的任何位置都可以使用分割以下的字符(_),仿真、综合编译器等都可以解析,同时SystemVerilog代码的工具会忽略下划线。在数字中添加一个下划线有助于使长数字更具可读性,尤其是二进制值-下划线也可用于显示值中的子字段,

向量填充文本值

SystemVerilog提供了一种特殊形式的无大小文本整数,它将任何大小的向量的所有位设置为0、l、X或Z。文本值的向量大小根据其上下文自动确定。

- ‘0用0填充左侧的所有位

- ‘1用1填充左侧的所有位

- ‘z或’Z用z填充左侧的所有位T

- ‘x或’X用x填充左侧的所有位

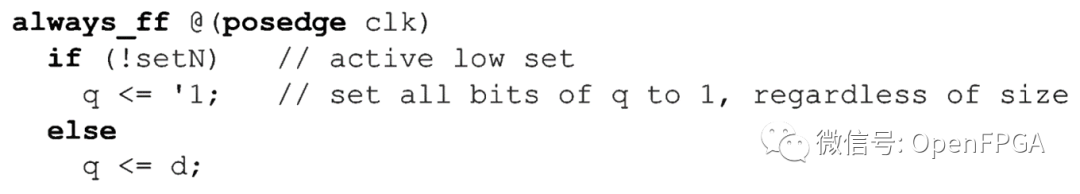

使用向量填充文本整数的示例如下:

向量填充文本整数是建模可伸缩设计的一个重要构造,对于不同的设计配置,可具有不同的向量宽度。本章后面章节讨论了可配置向量大小的建模。

这些向量填充文本整数不是传统Verilog的一部分。它们是作为原始Verilog语言的SystemVeri1og扩展的一部分添加的。

浮点文本值(实数)

SystemVerilog将浮点值称为实数。实数使用64位双精度浮点表示。文本浮点值是通过在文本数字中使用小数点来指定的。必须在小数点的两侧指定一个值。

3.1567

5.0

0.5

| 笔记 |

|---|

| RTL综合编译器通常不支持实(浮点)表达式。高级综合(HLS)工具可用于复杂的算法设计。浮点和定点设计不在本系列RTL建模的范围之内- |

审核编辑 :李倩

-

Verilog

+关注

关注

31文章

1374浏览量

114739 -

System

+关注

关注

0文章

166浏览量

38856 -

整数

+关注

关注

0文章

13浏览量

6710

原文标题:SystemVerilog(五)-文本值

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

关于OSIF_COUNTER_SYSTEM问题求解

Verilog HDL语法学习笔记

Linux Shell文本处理神器合集:15个工具+实战例子,效率直接翻倍

详解DBC的Signal与JSON文本结合

IBM Storage Scale System 6000焕新升级

使用NucleiStudio生成tb仿真需要的.verilog文件

芯来e203移植开发分享(二)——仿真文件简述与itcm固化程序

基于MCU200T的蜂鸟E203不上板跑分教程

NucleiStudio如何生成.verilog文件和.dasm文件,以及对.dasm文件中自定义指令反汇编结果分析

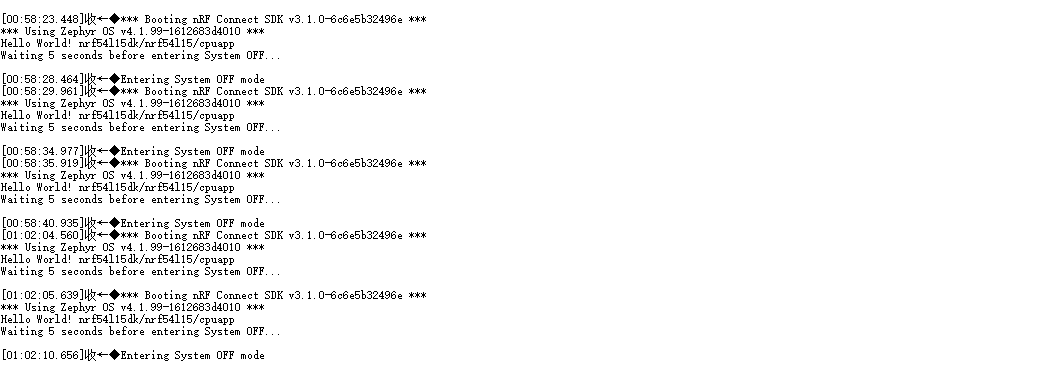

【NCS随笔】如何进入system_off深度睡眠模式以及配置GPIO中断唤醒

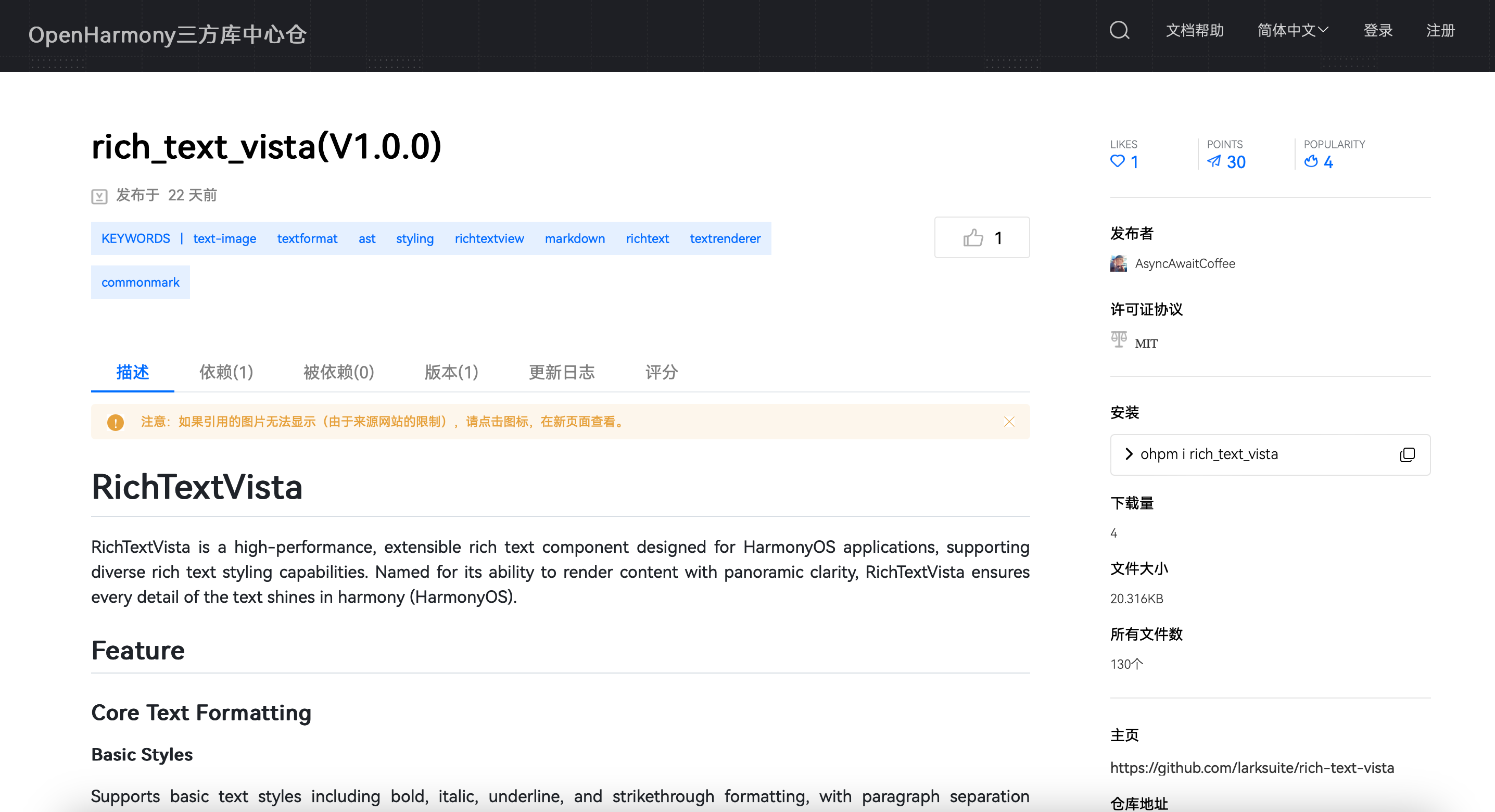

飞书富文本组件库RichTextVista开源

飞书开源“RTV”富文本组件 重塑鸿蒙应用富文本渲染体验

System Verilog-文本值

System Verilog-文本值

评论