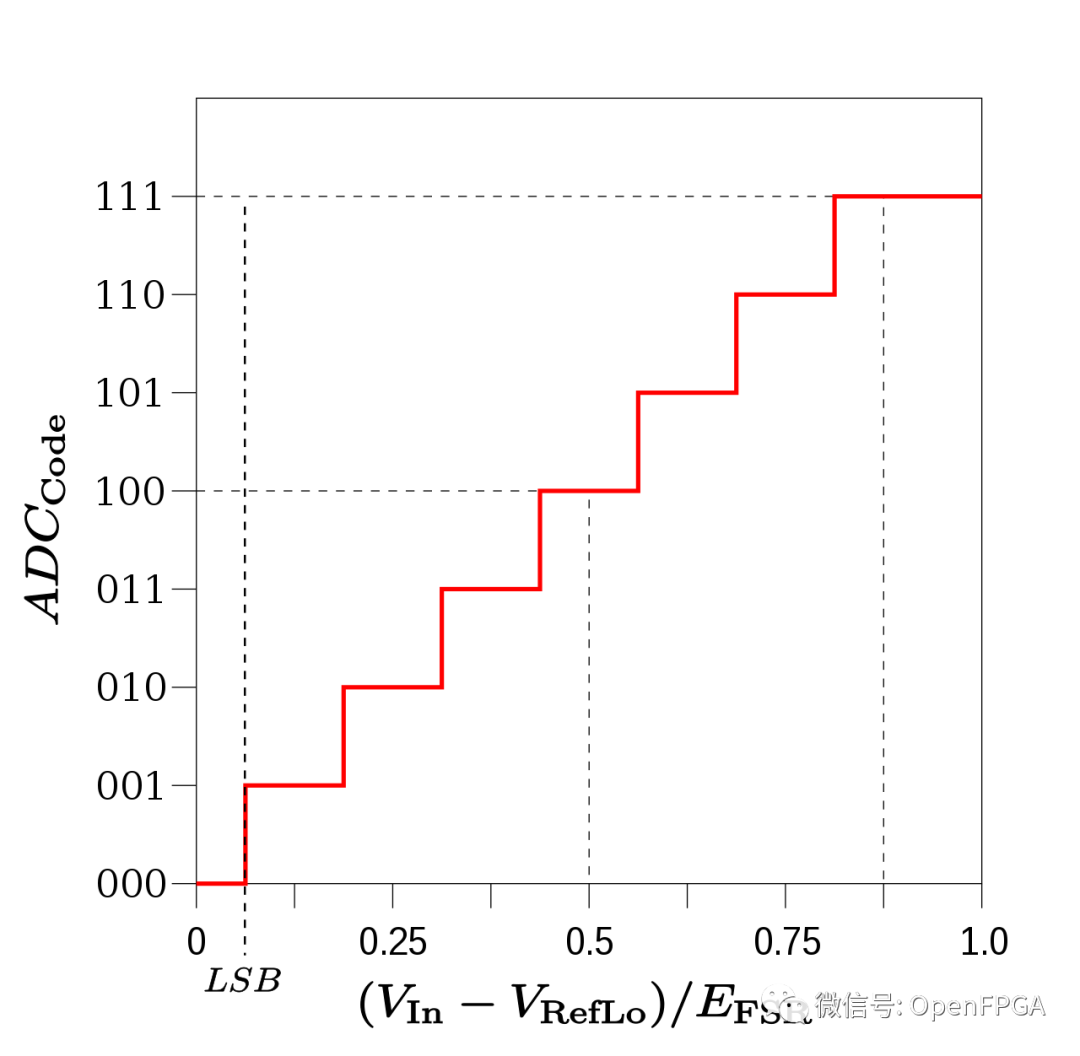

ADC: Analog to Digital Converter 模数转换器

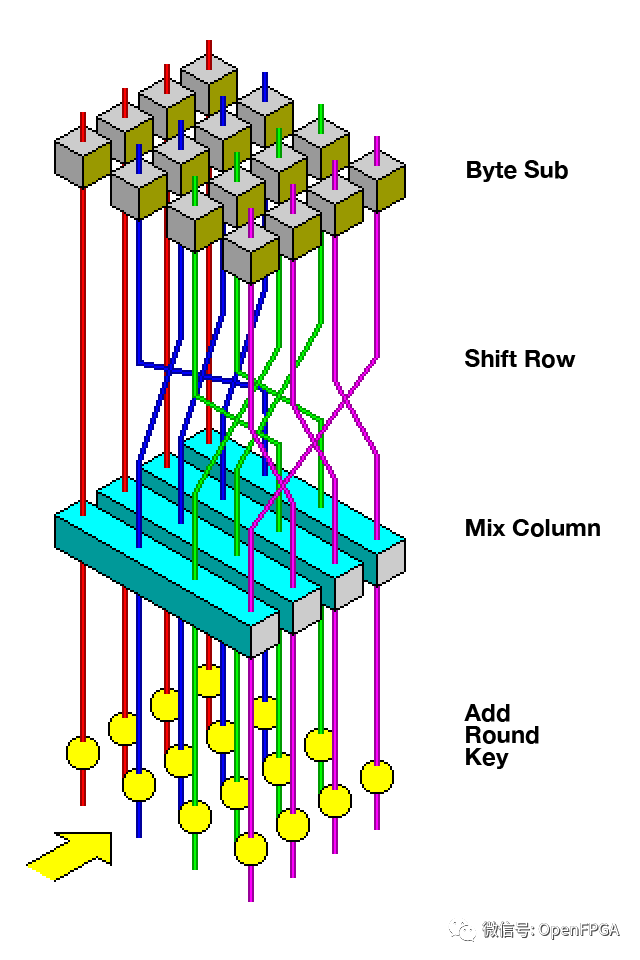

AES: Advanced encryption standard 高级加密标准

Adder: Circuit to add two numbers 将两个数字相加的电路

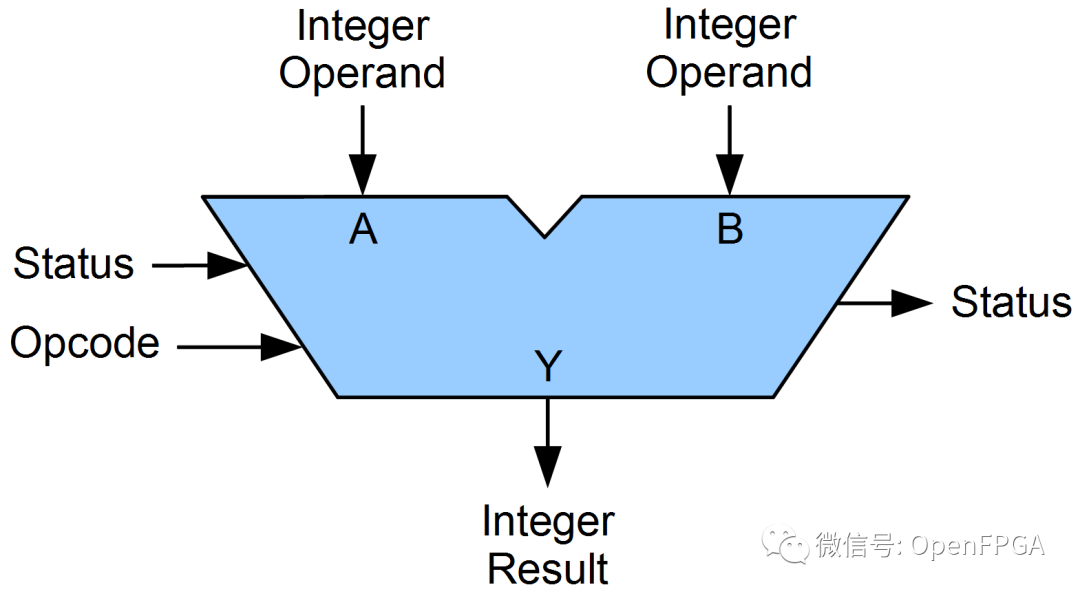

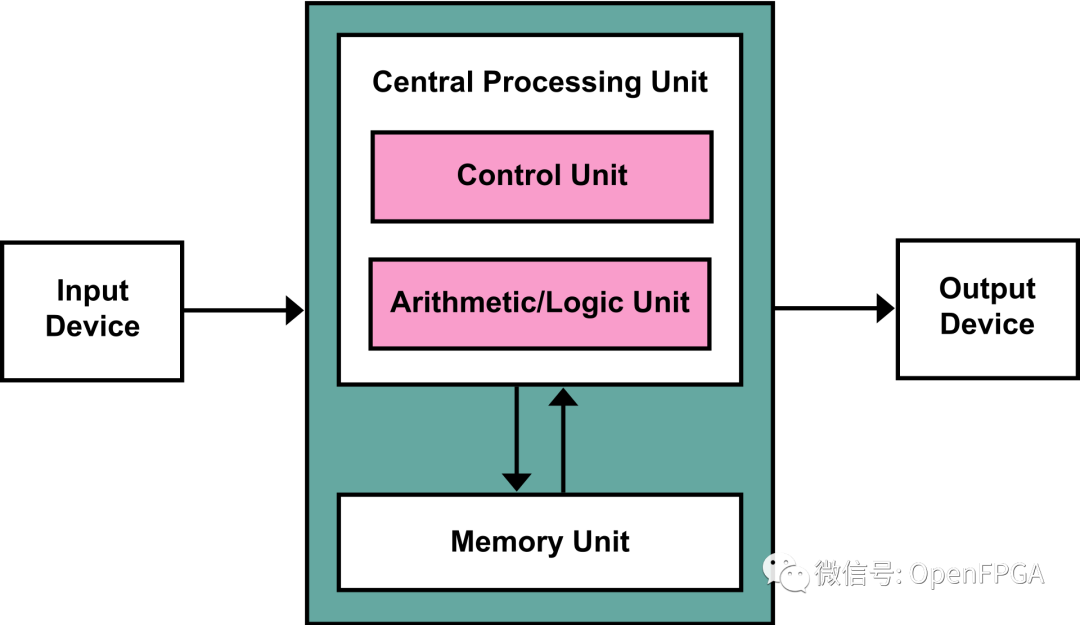

ALU: Arithmetic logic unit 算术逻辑单元

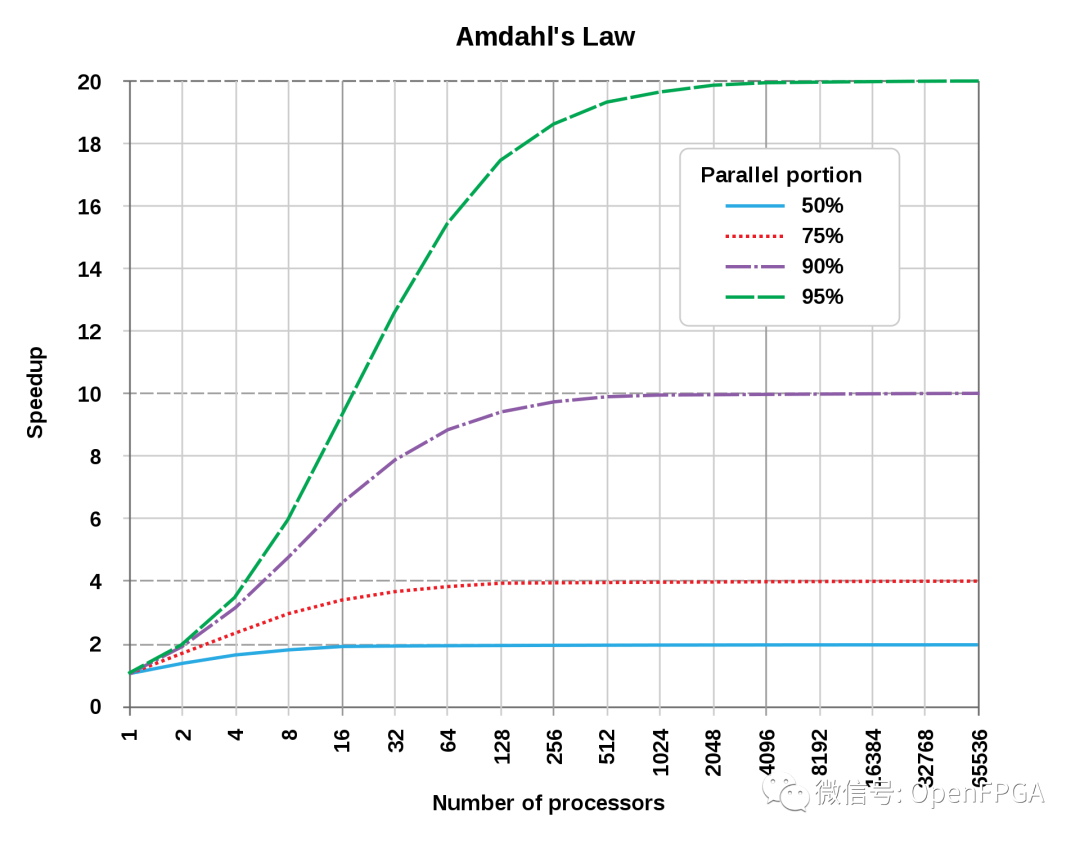

Amdahl's Law: Amdahl's law of diminishing returns for speeding up fixed workloads 阿姆达尔定律-通过优化系统的单个部分获得的整体性能改进受到实际使用改进部分的时间分数的限制

Arbiter: Arbitrates between competing requesters 仲裁器-在竞争请求者之间进行仲裁

ASIC: Application specific integrated circuit.专用集成电路。

Audio codec: Device/program that compresses/decompresses digital audio 音频编解码器-压缩/解压缩数字音频的设备/程序

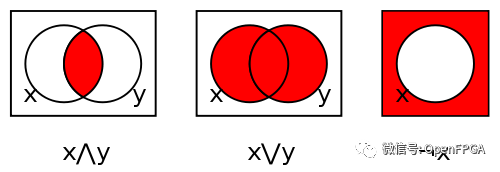

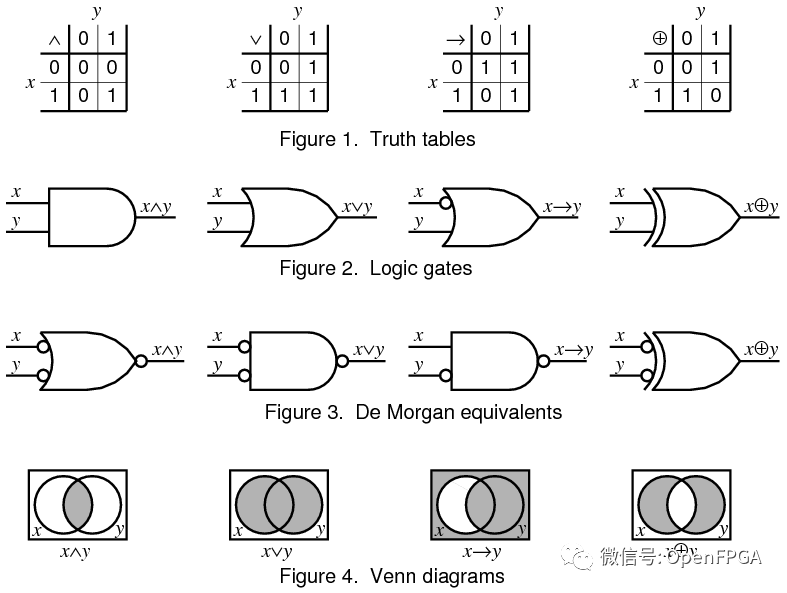

Boolean algebra: Algebra in which variables are either true or false 布尔代数-变量为真或假的代数

BTB: Branch target buffer 分支目标缓冲区

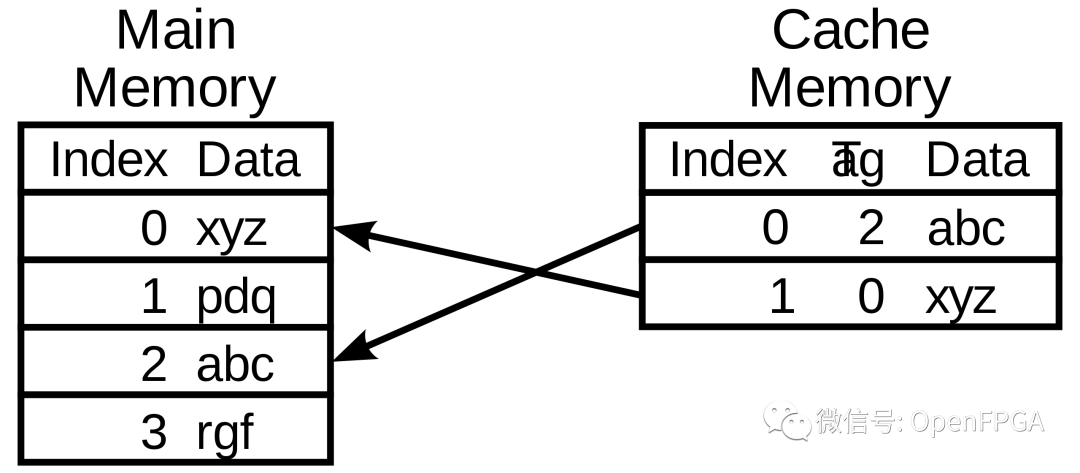

Cache: Local storage of program and/or data for future use. 程序和/或数据的本地存储以供将来使用。

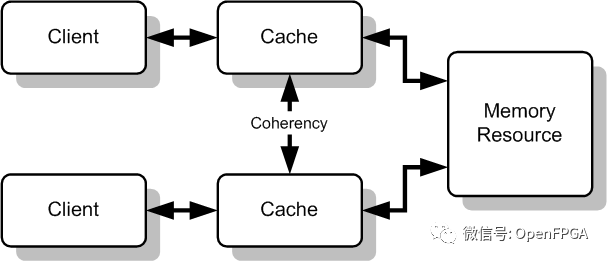

Cache coherence: Consistency of shared data that is stored in multiple local caches.存储在多个本地缓存中的共享数据的一致性。

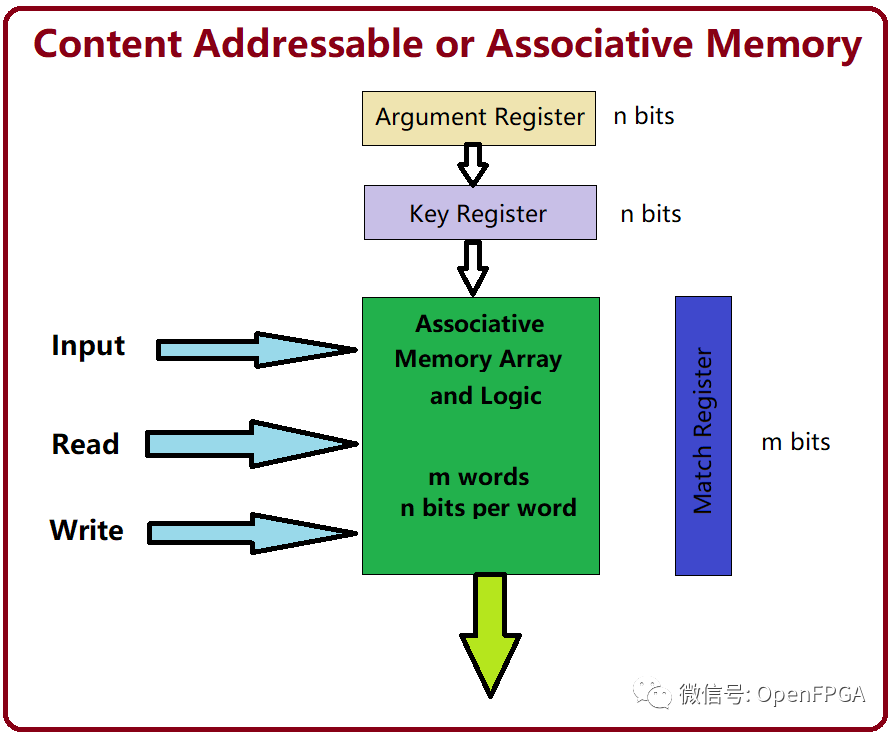

CAM: Content addressable memory 内容可寻址存储器

CISC: Complex instruction set computing 复杂指令集

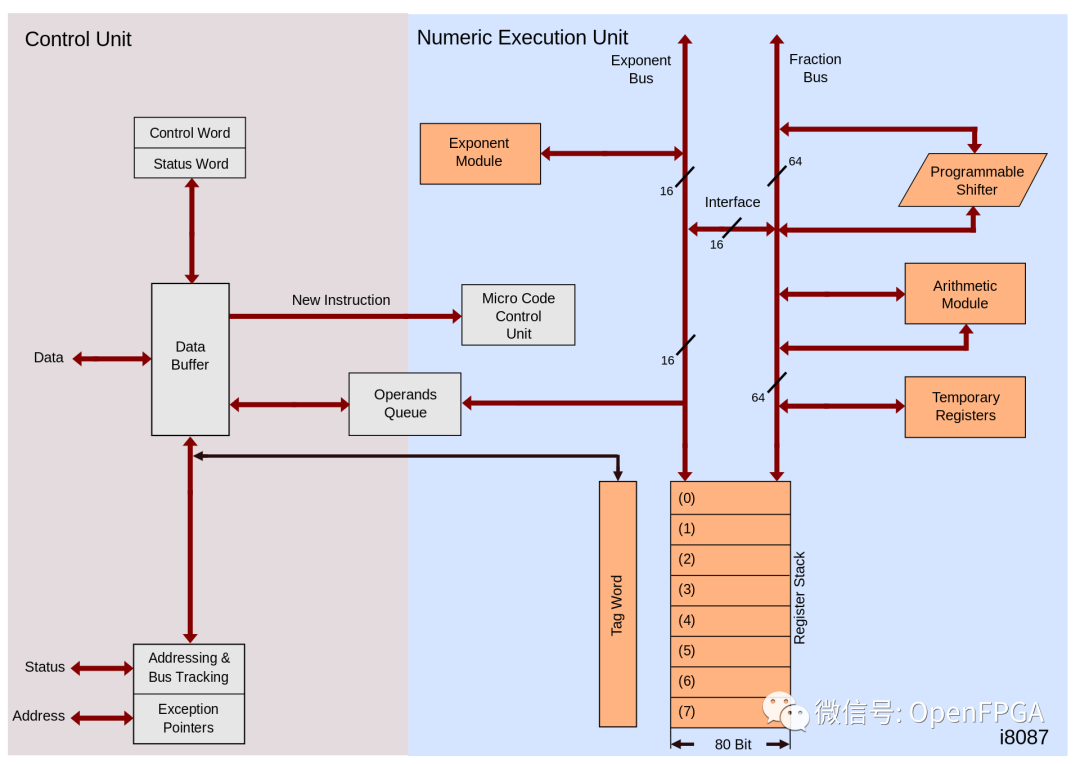

Coprocessor: A processor used to supplement operations of a primary (host) processor.协处理器-用于补充主处理器操作的处理器。

CPI: Cycles per instruction 每条指令的周期

CPU: Central processing unit 中央处理器

CRC: Cyclic redundancy check 循环冗余校验

CSA: Carry save adder 进位保存加法器

DAC: Digital to Analog Converter 数模转换器

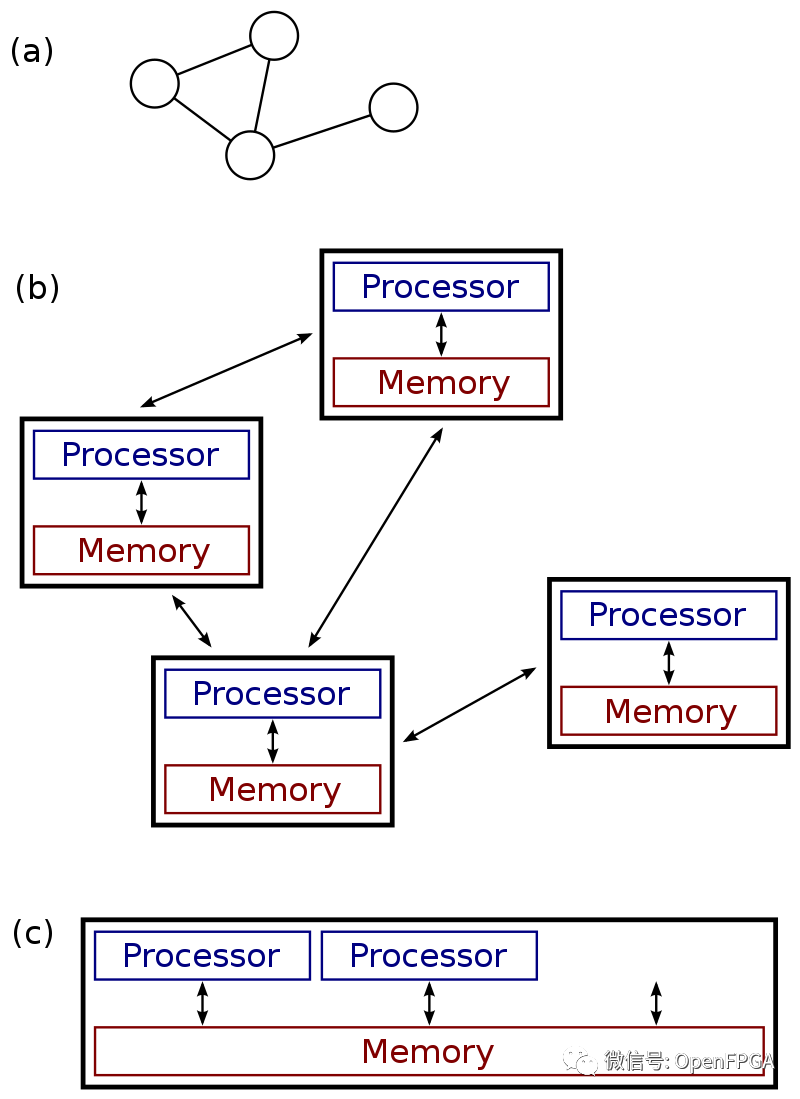

Distributed Computing: Computer with components working towards common goal with without strict coupling.分布式计算-具有朝着共同目标工作的组件的计算机,没有严格的耦合。

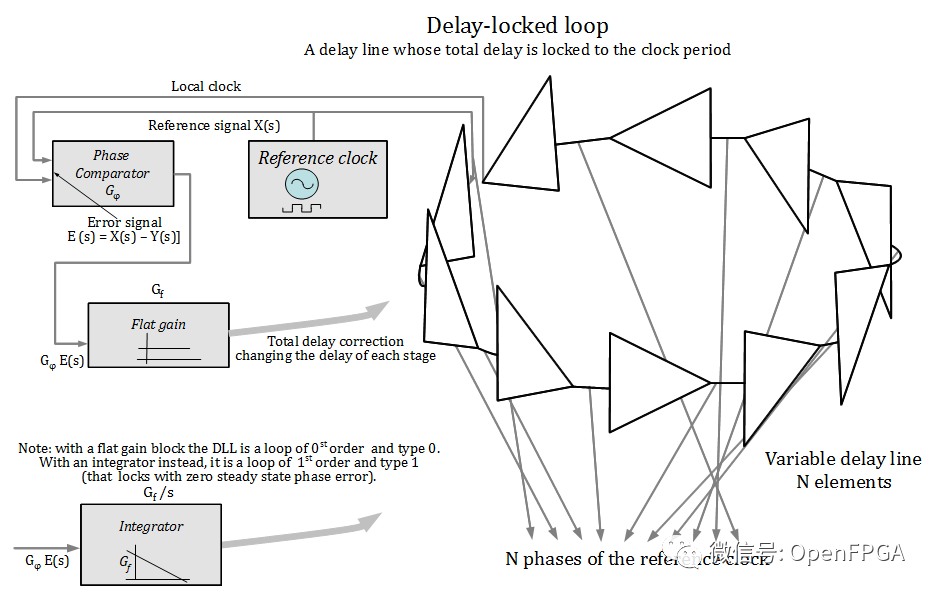

DLL: Delay locked loop 延迟锁定环(DLL) 是一种类似于锁相环(PLL) 的数字电路

DMA: Direct memory access 直接内存访问

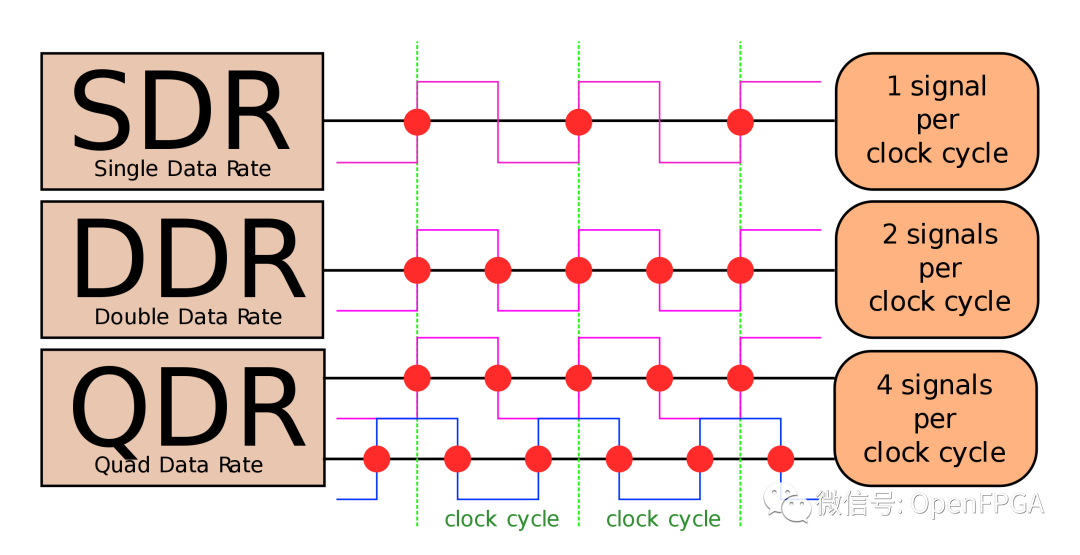

DDR Double data rate 双倍数据速率

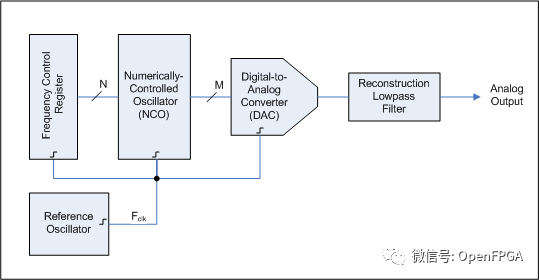

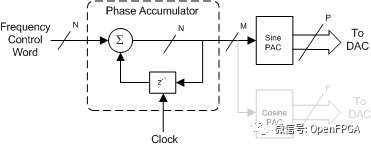

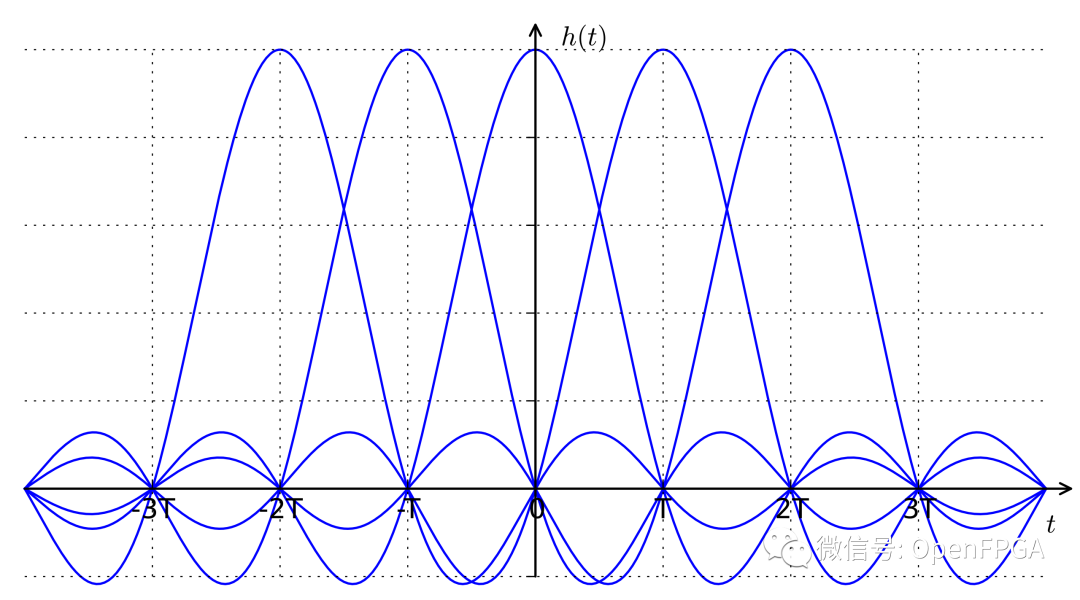

DDS: Direct digital synthesis 直接数字合成

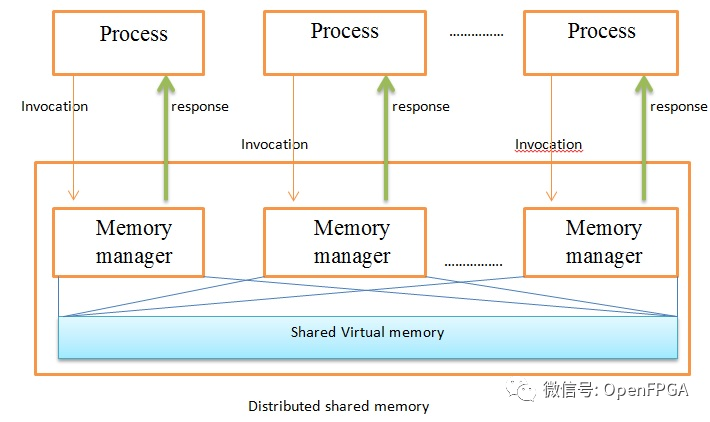

DSM: Distributed shared memory 分布式共享内存

DSP: Digital signal processor 数字信号处理器

ECC: Error correcting code 纠错码

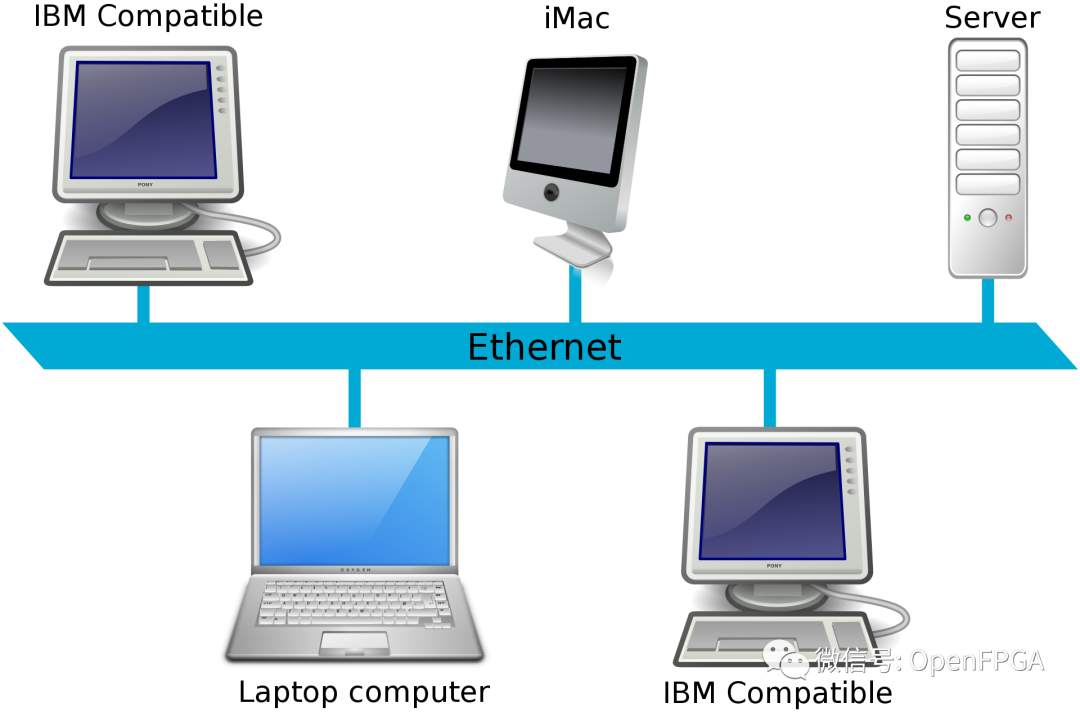

Ethernet: Family of standard network technologies 标准网络技术系列

Fault Tolerance: The ability of a system to keep operating in the event of failure of one of its components. 容错-系统在其组件之一发生故障的情况下保持运行的能力。

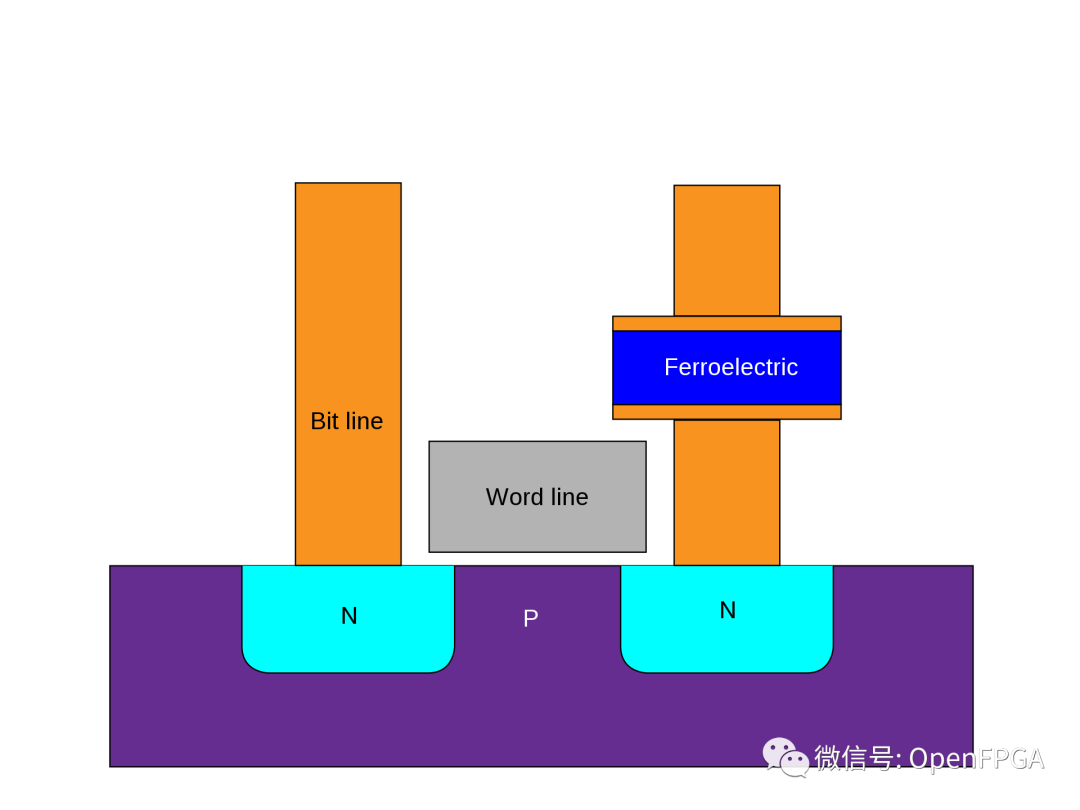

FRAM: Non-volatile RAM based on ferroelectric layer.基于铁电层的非易失性 RAM。

FPGA: Field-programmable gate array is a chip that can be reprogrammed "in the field". 现场可编程门阵列

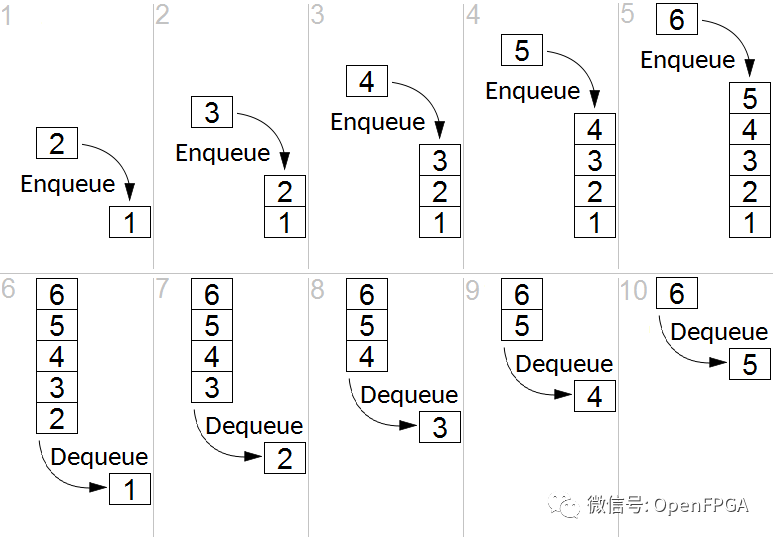

FIFO: First in first out buffer 先进先出缓冲区

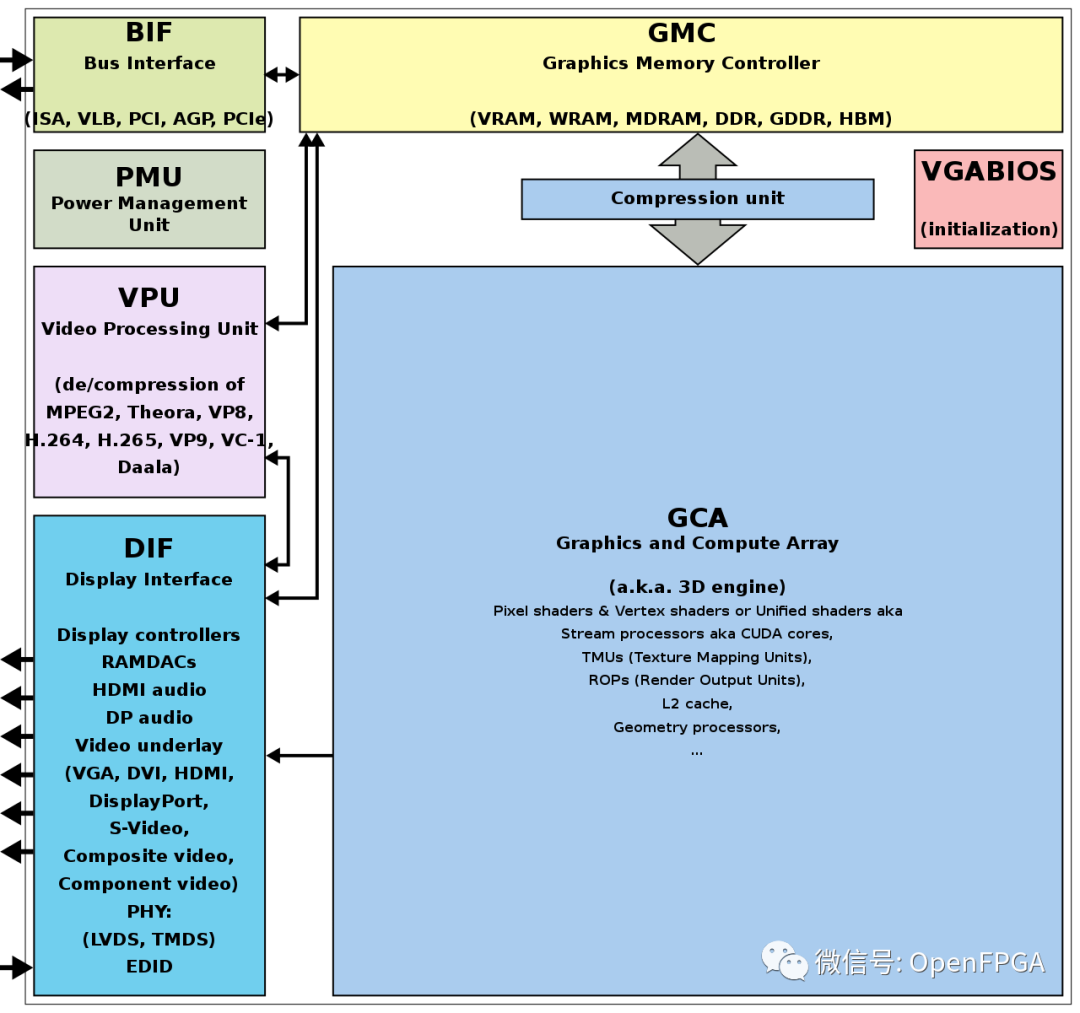

GPU: Integrated circuit for accelerating the creation of graphics on a display. 图形处理单元

DRAM: Dynamic random-access semiconductor memory 动态随机存取半导体存储器

Flash: Non-volatile semiconductor memory 非易失性半导体存储器

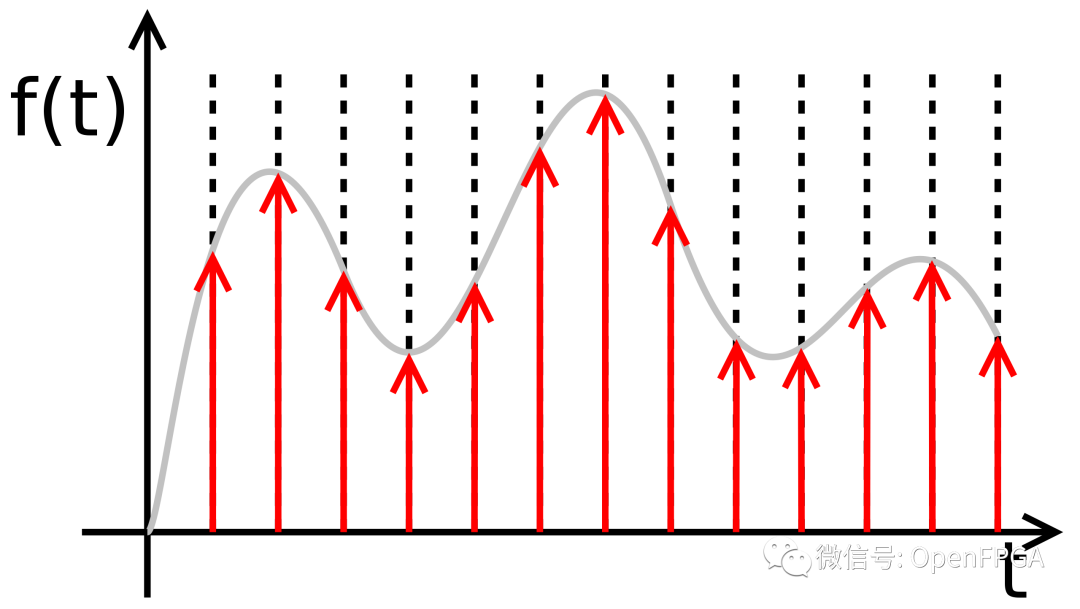

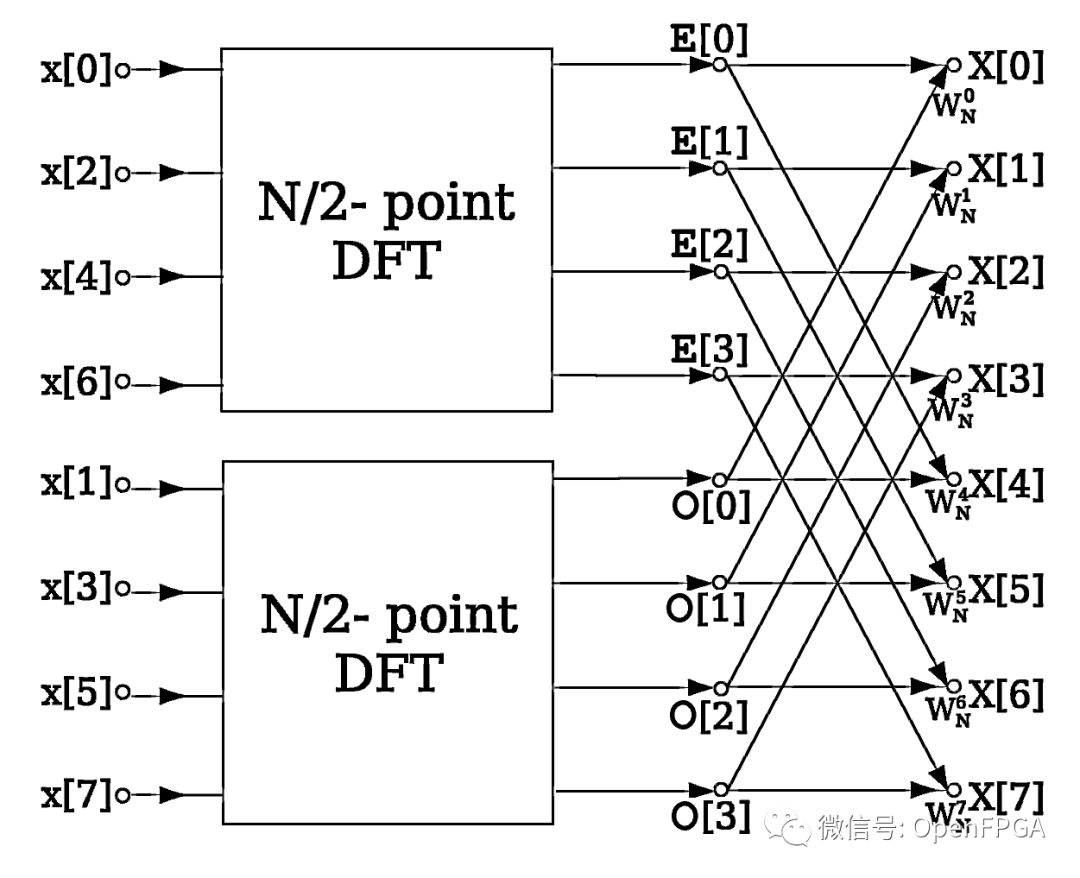

FFT: Fast Fourier transform 快速傅里叶变换

FPU: Floating point unit 浮点单元

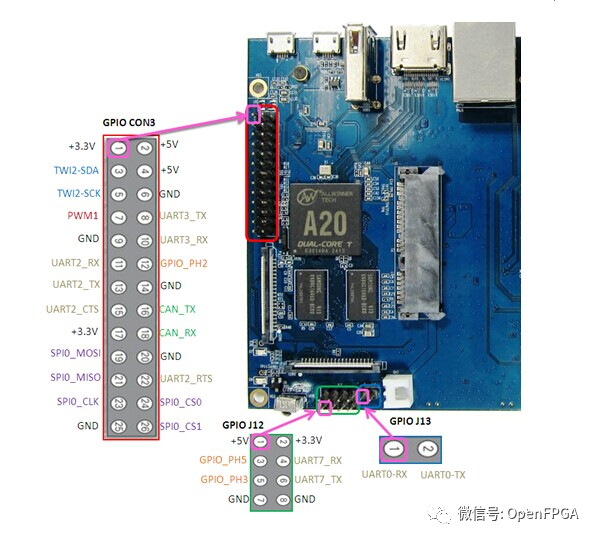

GPIO: General purpose input output, controllable at run time 通用输入输出,运行时可控

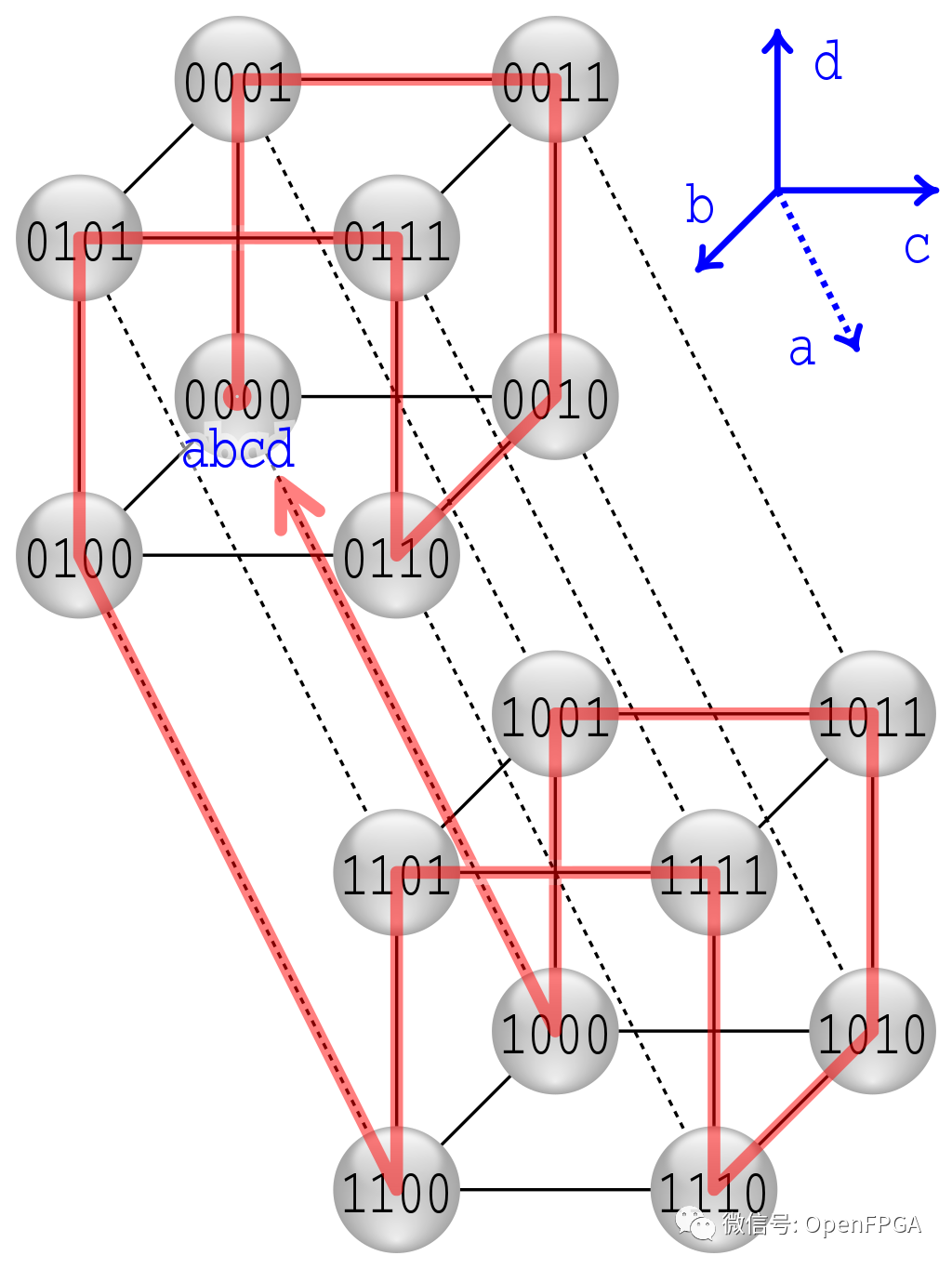

Gray code: Binary system where successive values differ by one bit 格雷码:连续值相差一位的二进制系统

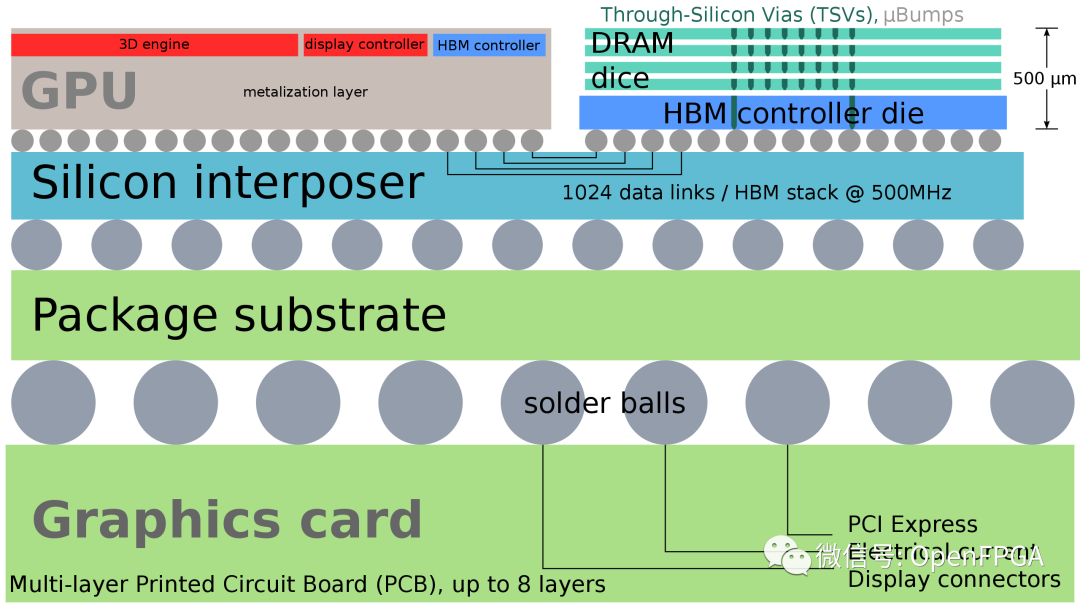

HBM: High bandwidth memory 高带宽内存

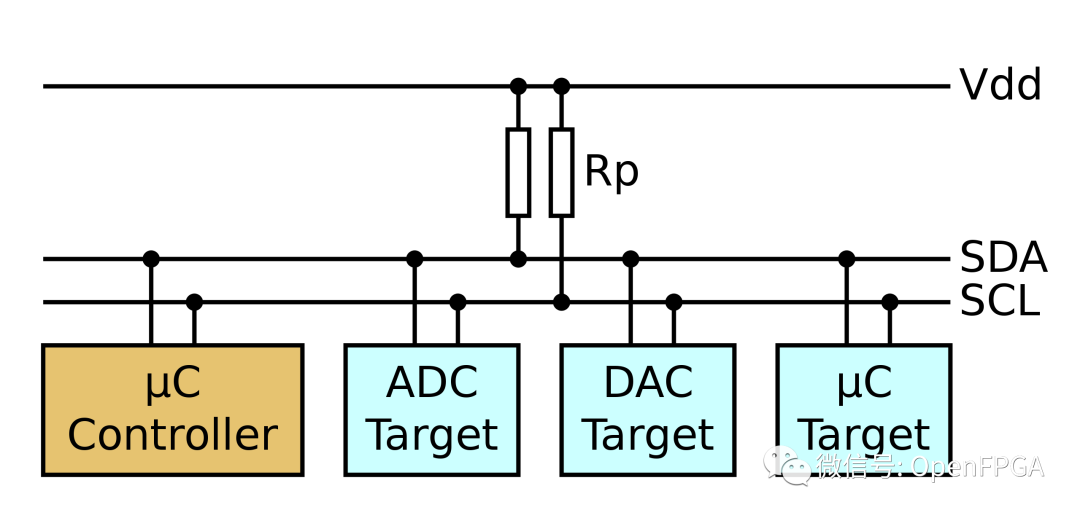

I2C: Multi-master 2 wire bus 多主机 2 线总线

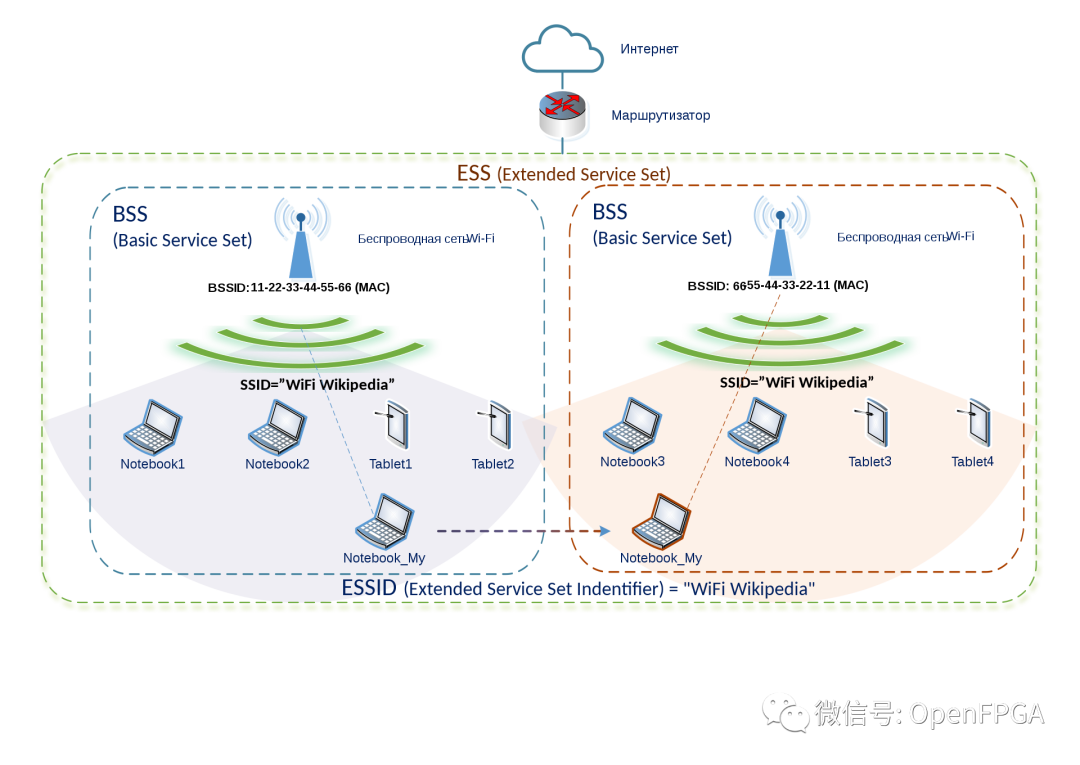

LAN: Local area network 局域网

LFSR: Linear feedback shift register 线性反馈移位寄存器

LSB: Least significant bit 最低有效位

[LUT] (https://en.wikipedia.org/wiki/Lookup_table): An array that replaces runtime computation with a simpler array indexing operation 查找表(LUT) 是一个数组,它用更简单的数组索引操作代替运行时计算。

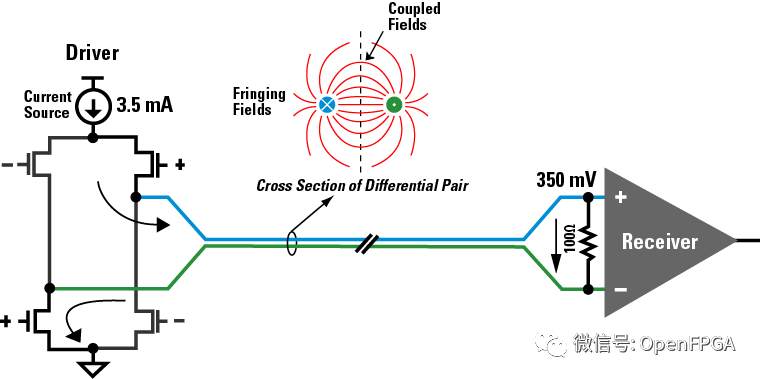

LVDS: Low-voltage differential signaling (also TIA/EIA-644) 低压差分信号(也是 TIA/EIA-644)

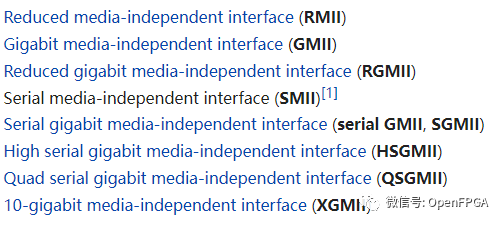

MII: Media independent interface for PHY chips PHY芯片的媒体独立接口

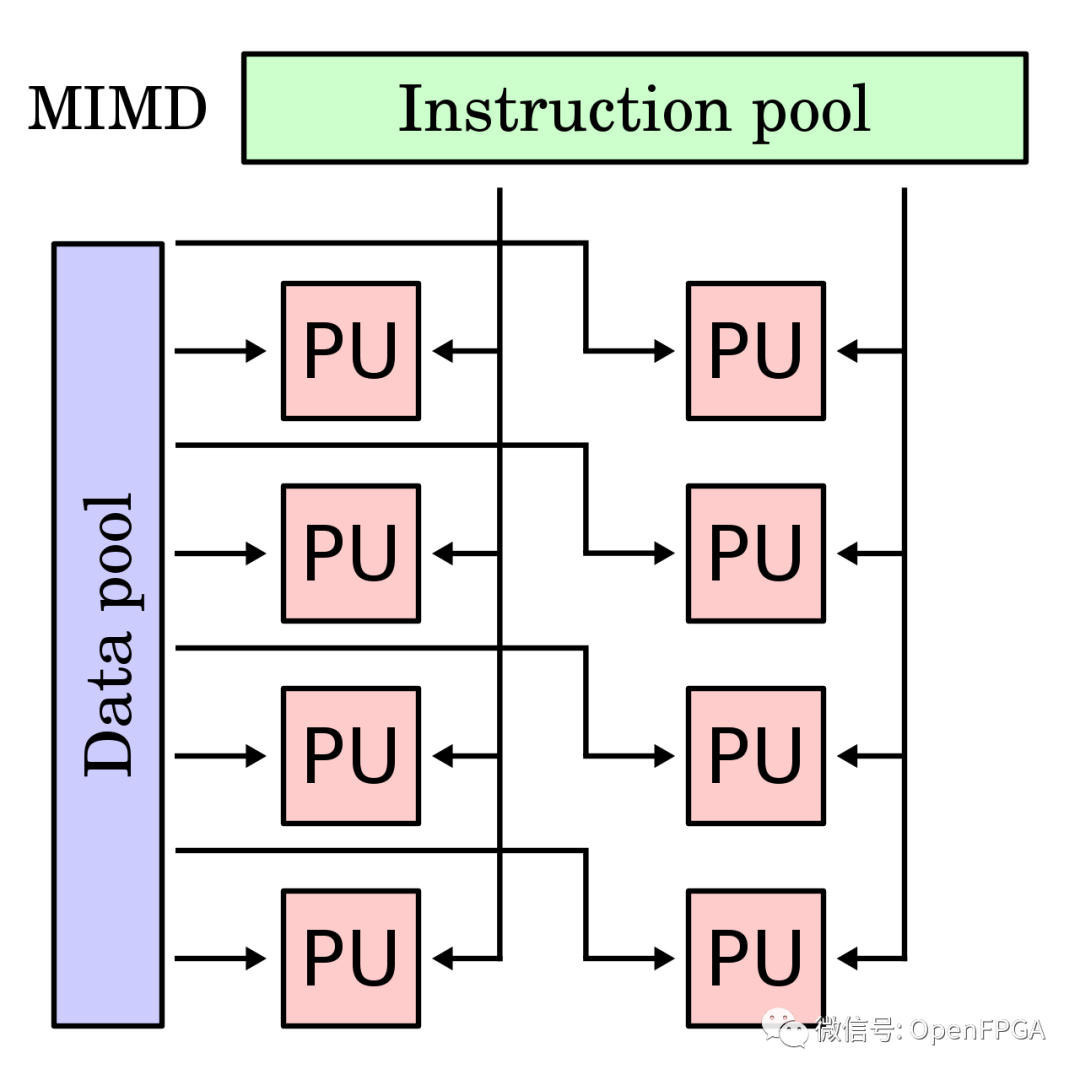

MIMD: Multiple instructions multiple data architecture 多指令多数据架构

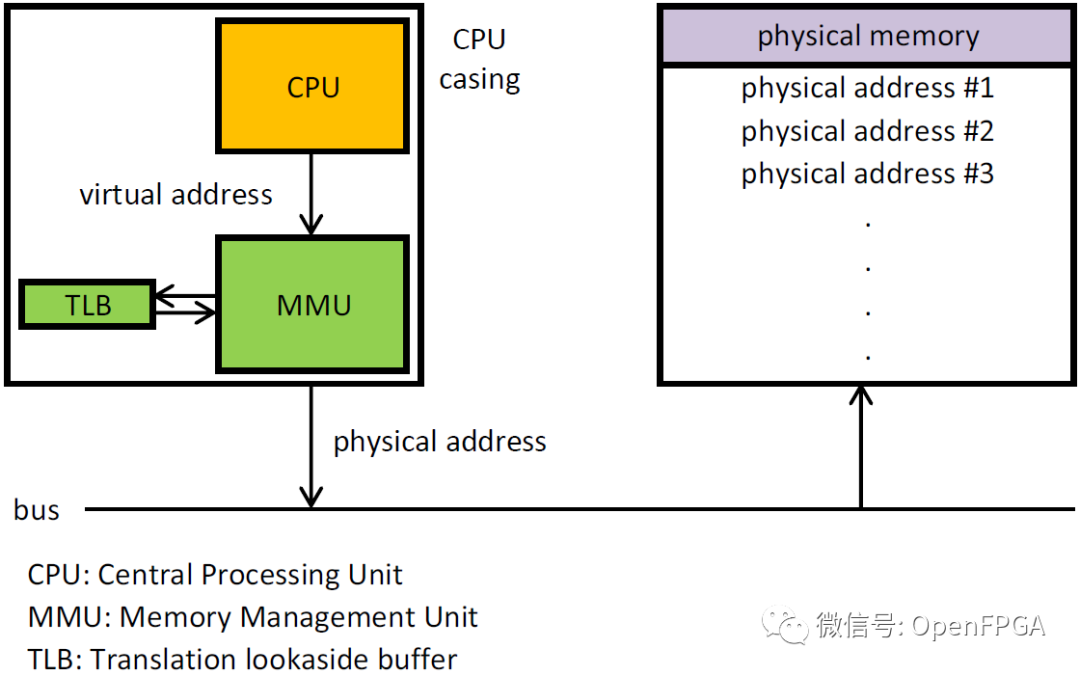

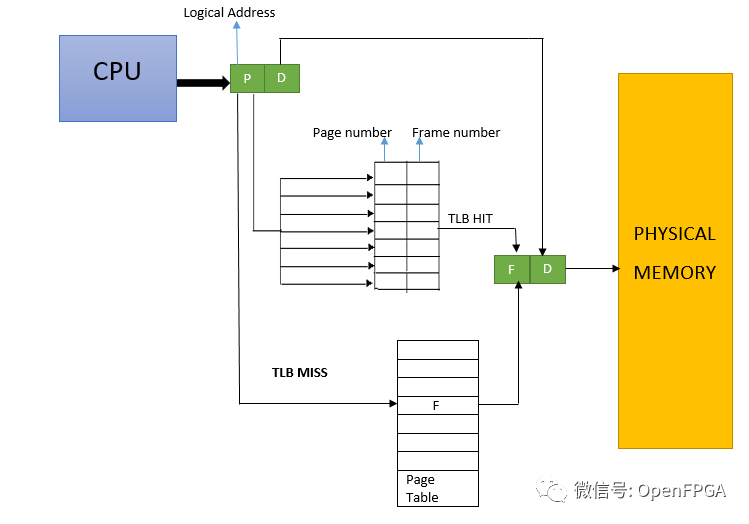

MMU: Memory management unit 内存管理单元

MSB: Most significant bit 最高有效位

MUX: Multiplexer 多路复用器

Multiplier: Binary multiplier 二进制乘数

NCO: Numerically controlled oscillator 数控振荡器

NOC: Network on a chip 片上网络

Parallel Computing: A type of computation where many operations are carried out simultaneously. 并行计算

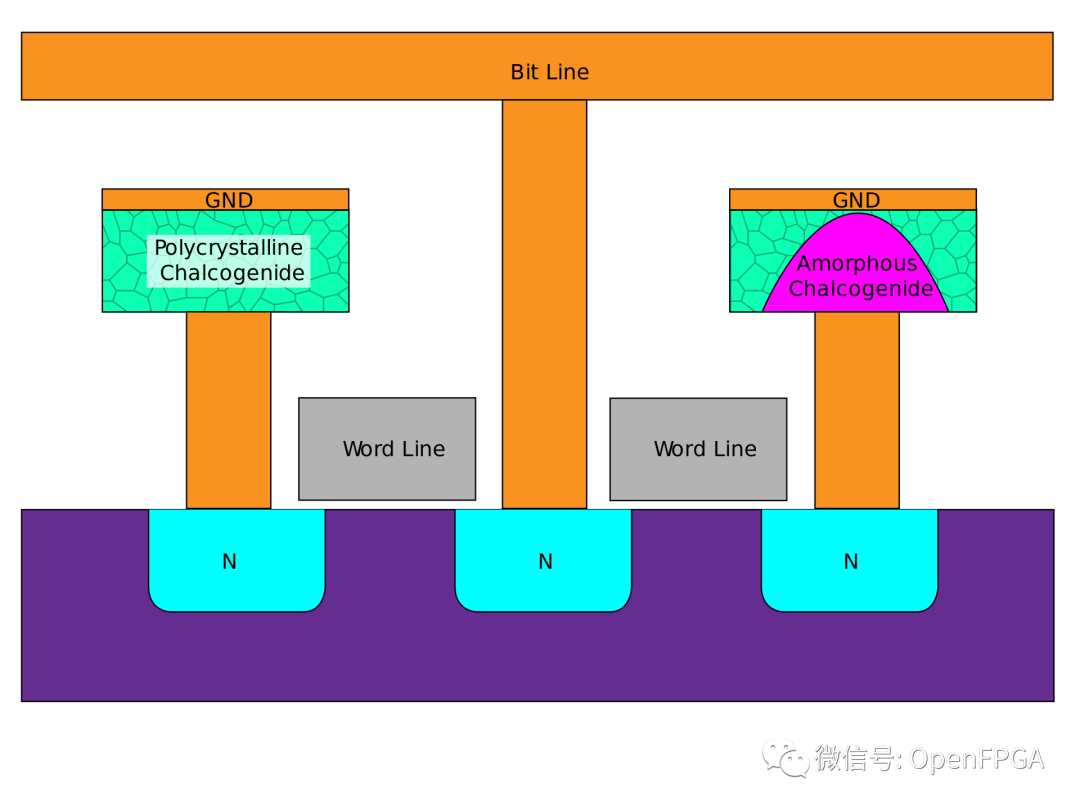

PCM: Phase change memory 相变存储器

PCIe: High Speed serial computer expansion bus 高速串行计算机扩展总线

PIC: Programmable interrupt controller 可编程中断控制器

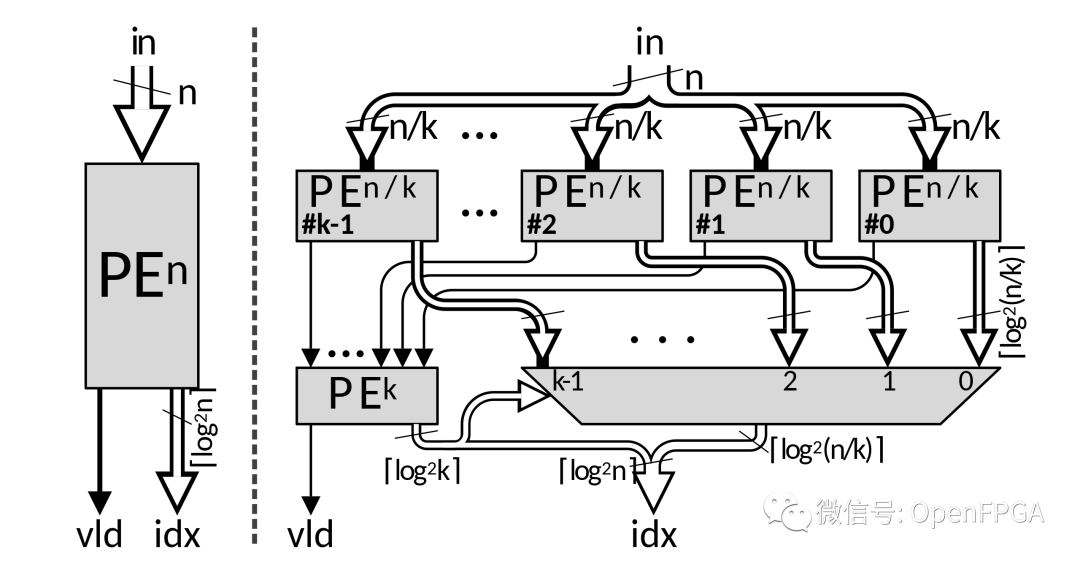

Priority Encoder: A circuit or algorithm that compresses multiple binary inputs into a smaller number of outputs 优先级编码器-将多个二进制输入压缩成较少数量输出的电路或算法

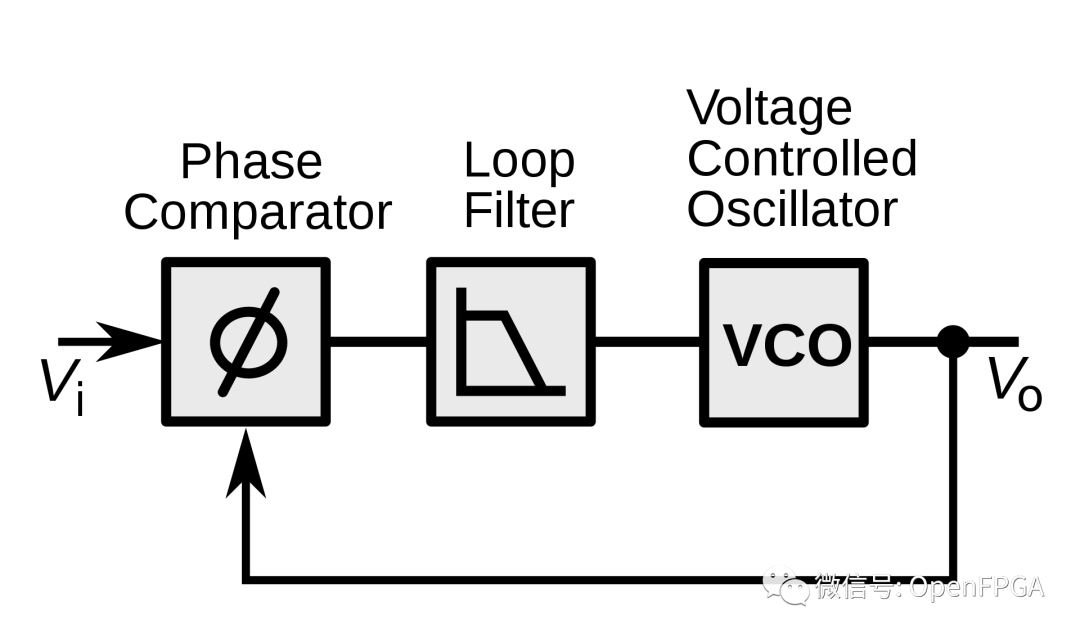

PLL: Phase locked loop 锁相环

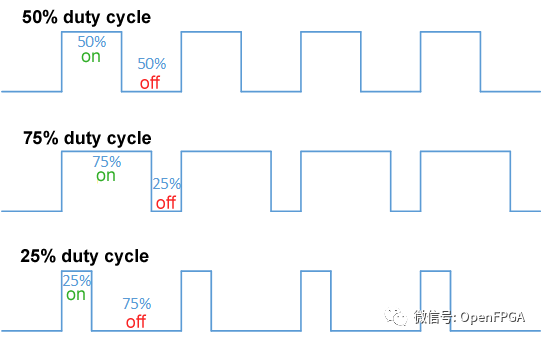

PWM: Pulse width modulation脉冲宽度调制

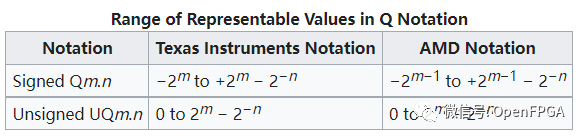

Q: Q fixed point number formatQ 定点数格式

RAID: Redundant array of disks 冗余磁盘阵列

Reconfigurable Computing: Collection of customizable datapaths connected together by a fabric 可重构计算-通过结构连接在一起的可定制数据路径的集合

RISC: Reduced instruction set computing 精简指令集计算

ROM: Read only memory (denser than RAM) 只读存储器(比 RAM 更密集)

SBC: Single board computers 单板计算机

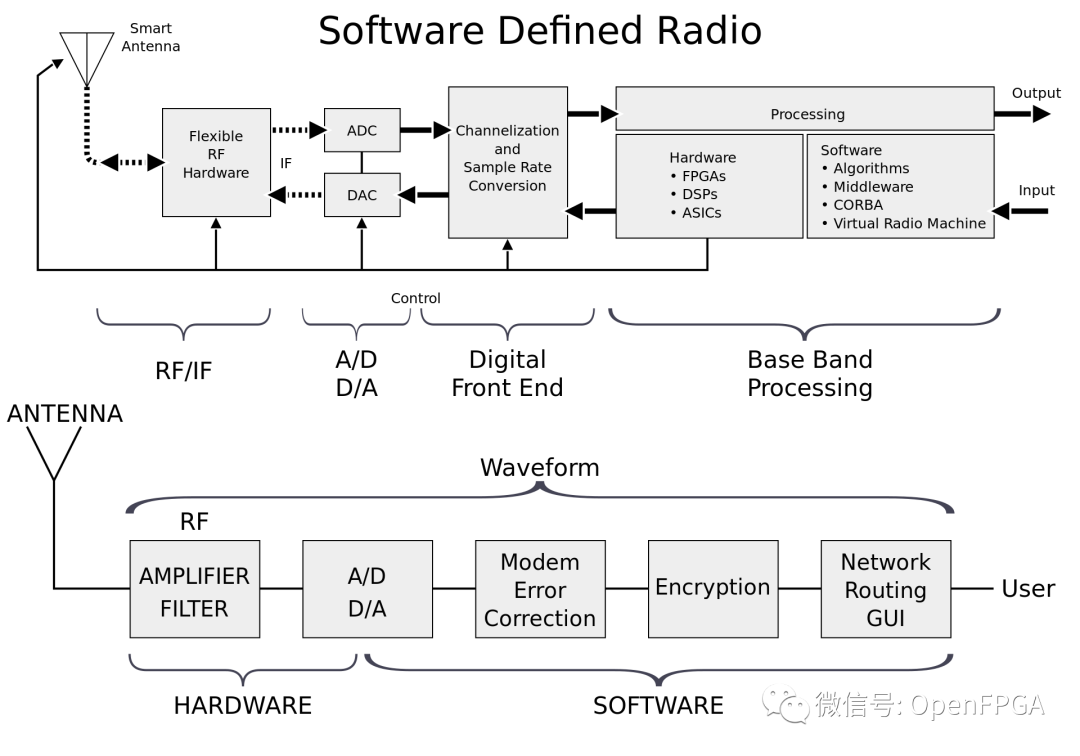

SDR: Software defined radio 软件定义无线电

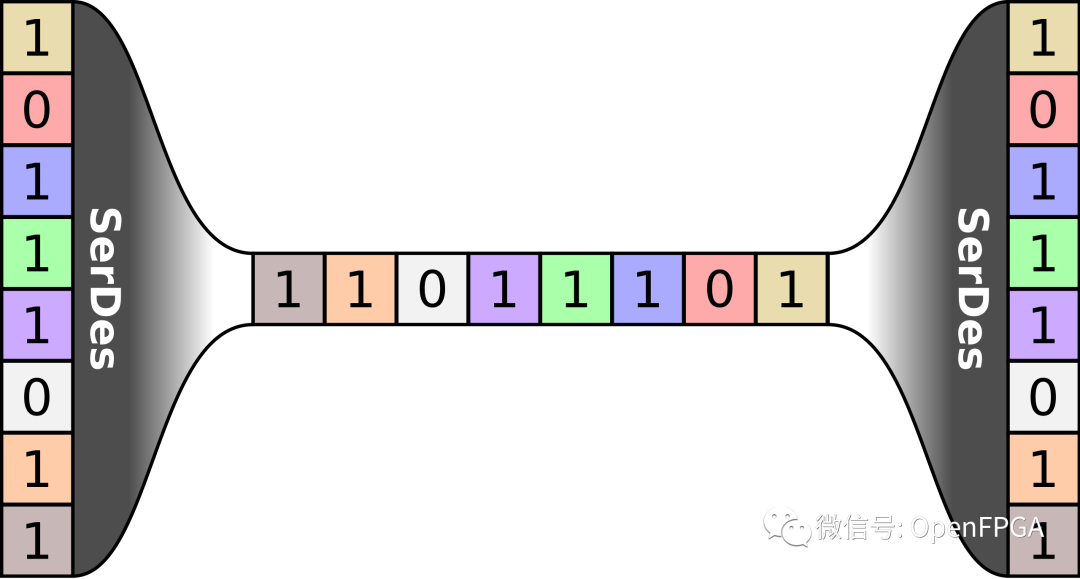

SERDES: Serializer/deserializer 串行器/解串器

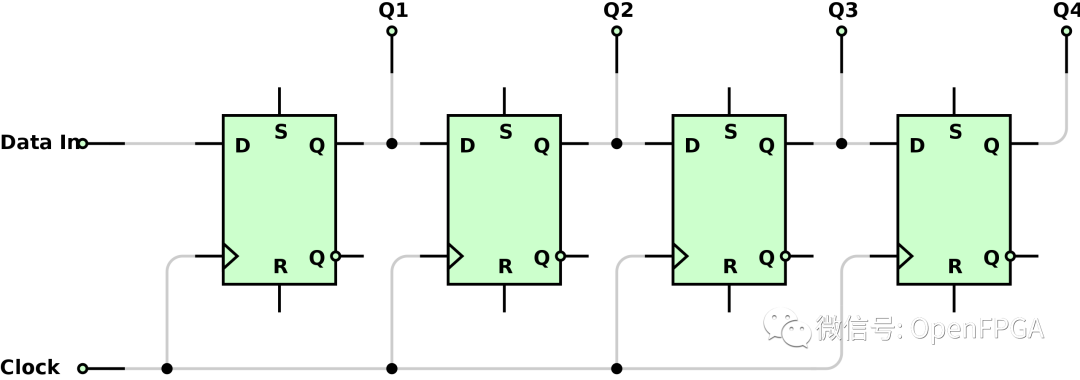

Shift Register: Set of registers that shifts bits one position at a time 一次移位一个位置的一组寄存器

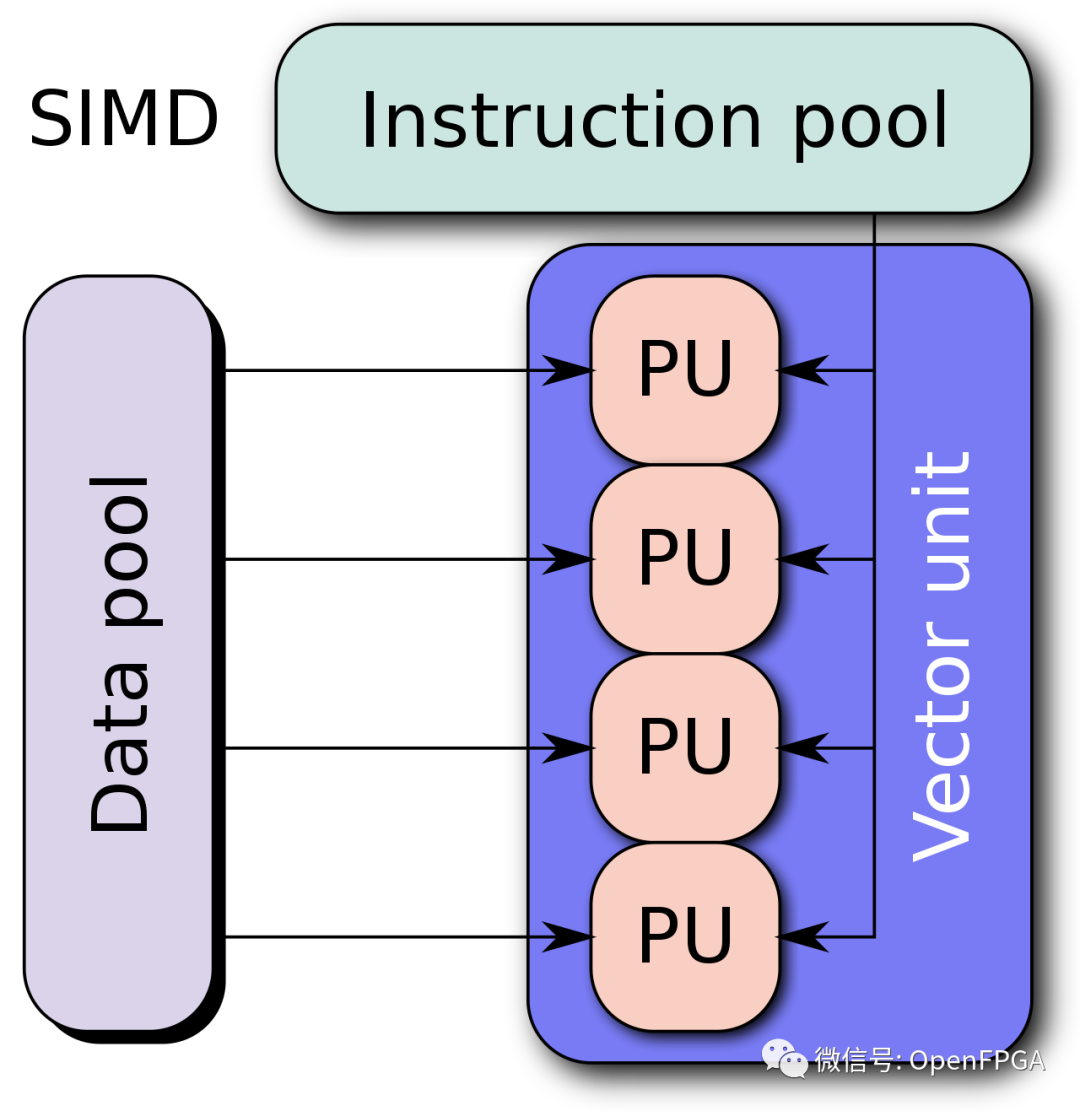

SIMD: Single instruction multiple data 单指令多数据

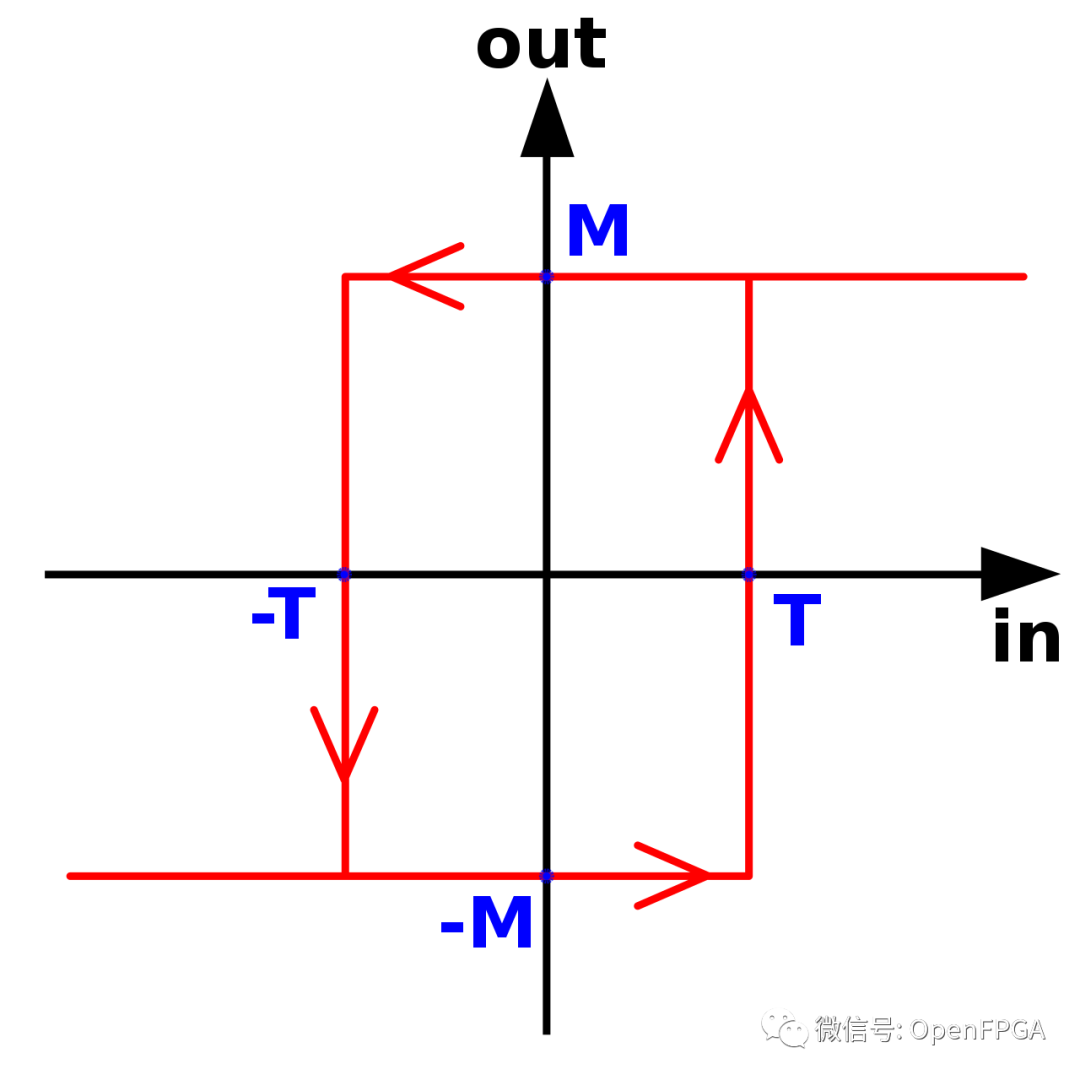

Schmitt Trigger: Comparator circuit with hysteresis 施密特触发器-具有迟滞的比较器电路

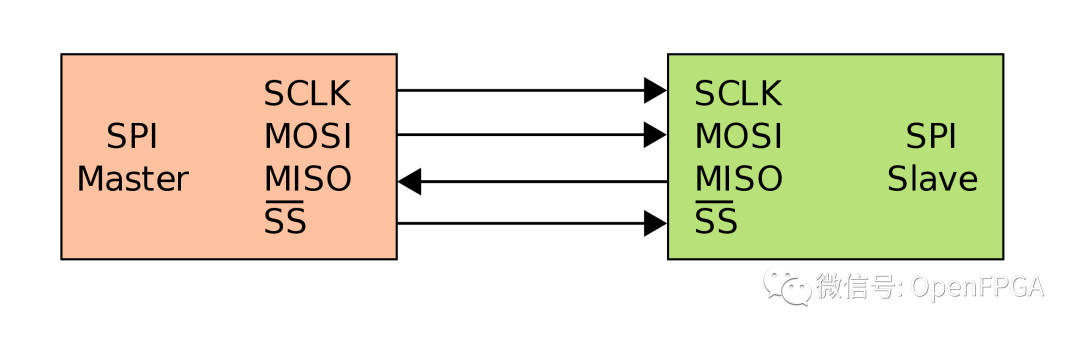

SPI: Synchronous 4 wire master/slave interface 同步4线主/从接口

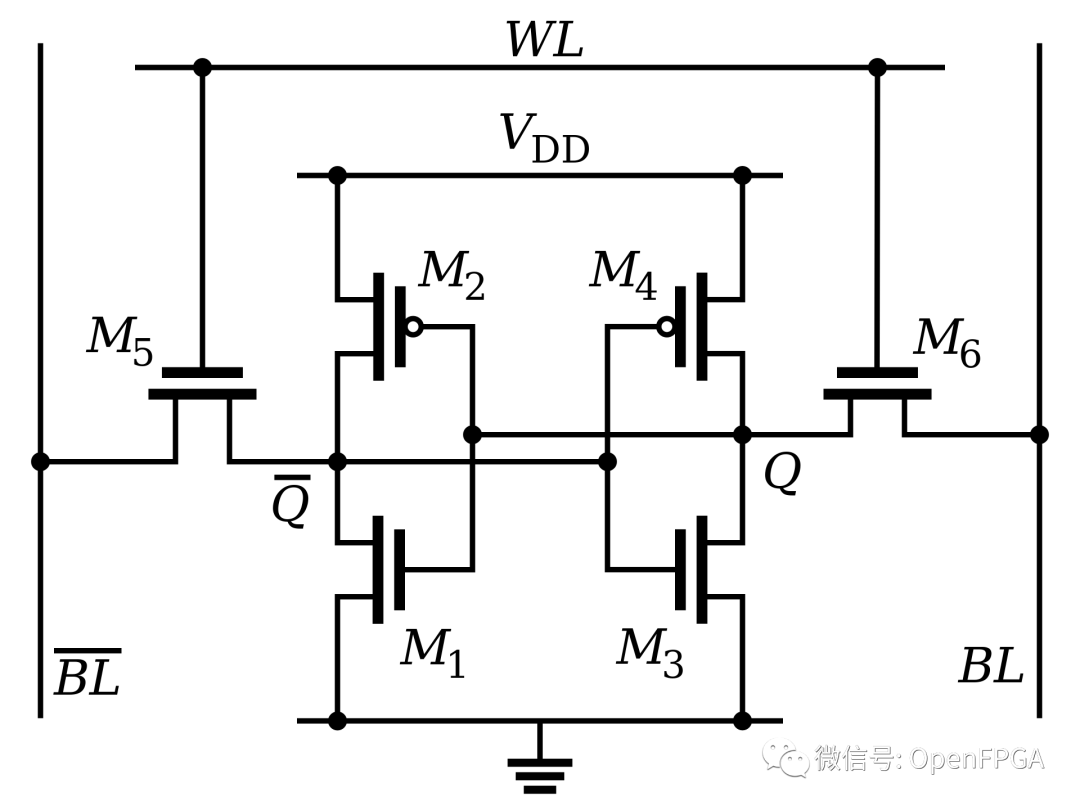

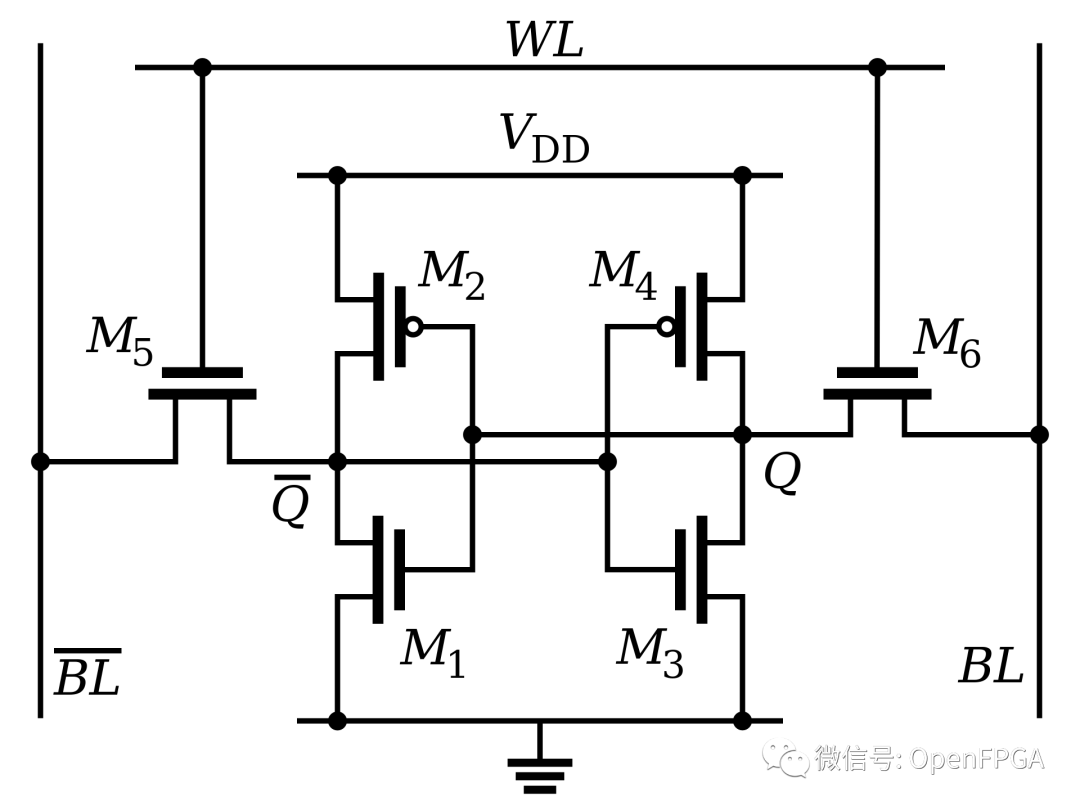

SRAM: Static random access semiconductor memory 静态随机存取半导体存储器

TLB: Translation lookaside buffer 翻译后备缓冲区

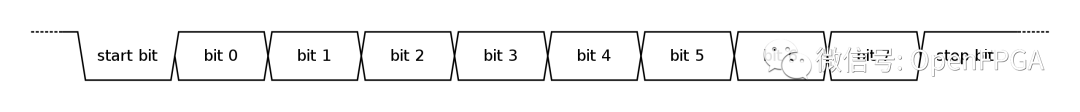

UART: Asynchronous 2 wire point to point interface 异步2线点对点接口

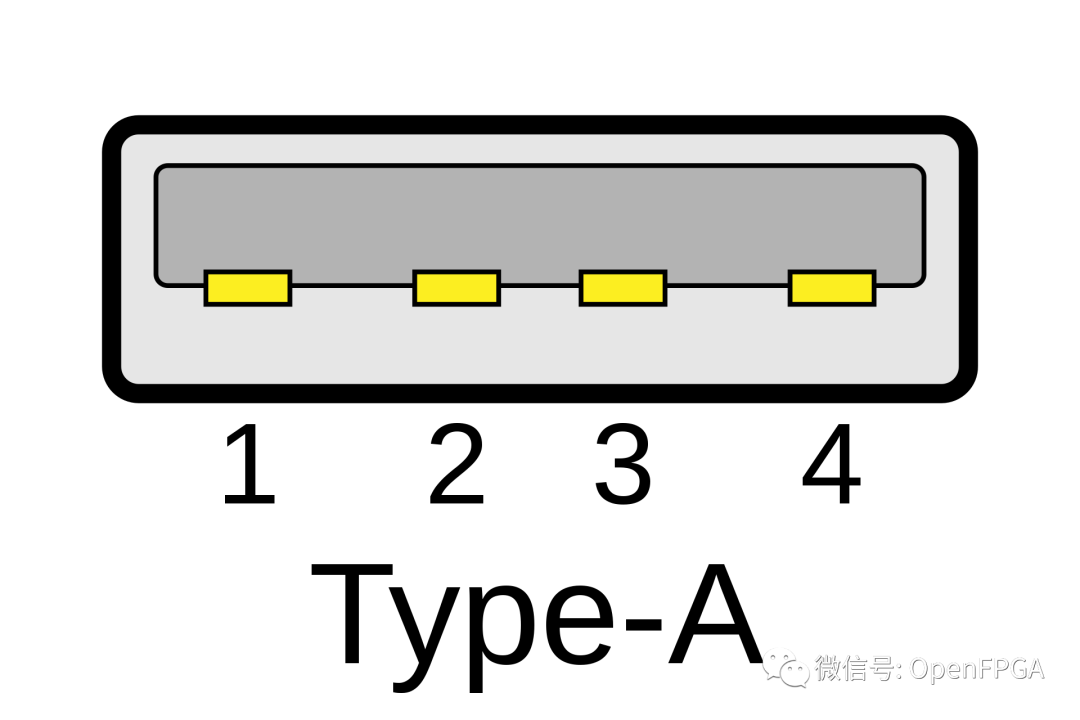

USB: 2 wire point to point 5 V interface 2线点对点5V接口

Video codec: Device/program that compresses/decompresses digital video 视频编解码器-压缩/解压缩数字视频的设备/程序

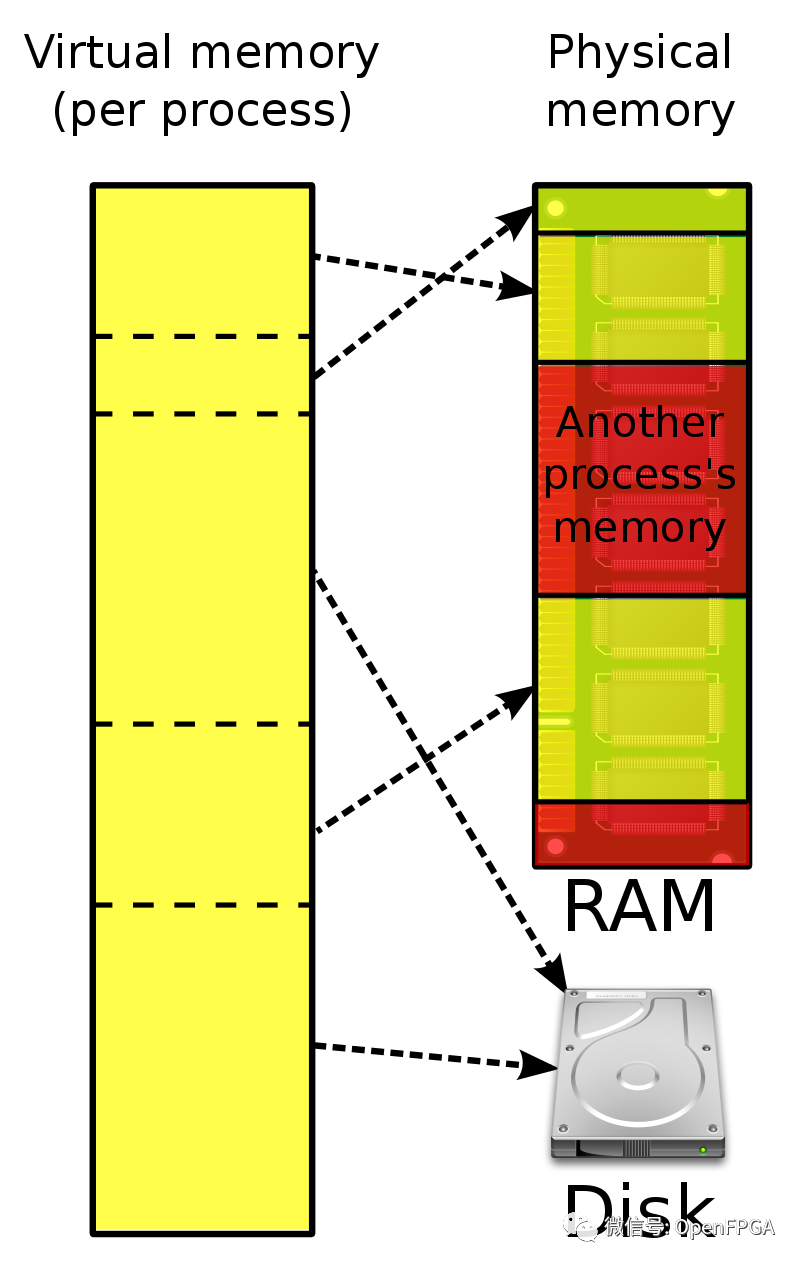

Virtual Memory: The automatic mapping of virtual program addresses to physical addresses 虚拟内存-虚拟程序地址到物理地址的自动映射

VLIW: Very long instruction level parallelism 长的指令级并行性

WAN: Wide area network 广域网

WIFI: Wireless local area network 无线局域网

8b10b: Code that maps 8-bits to 10bit DC balanced symbols 将 8 位映射到 10 位 DC 平衡符号的代码

Chip Design芯片设计

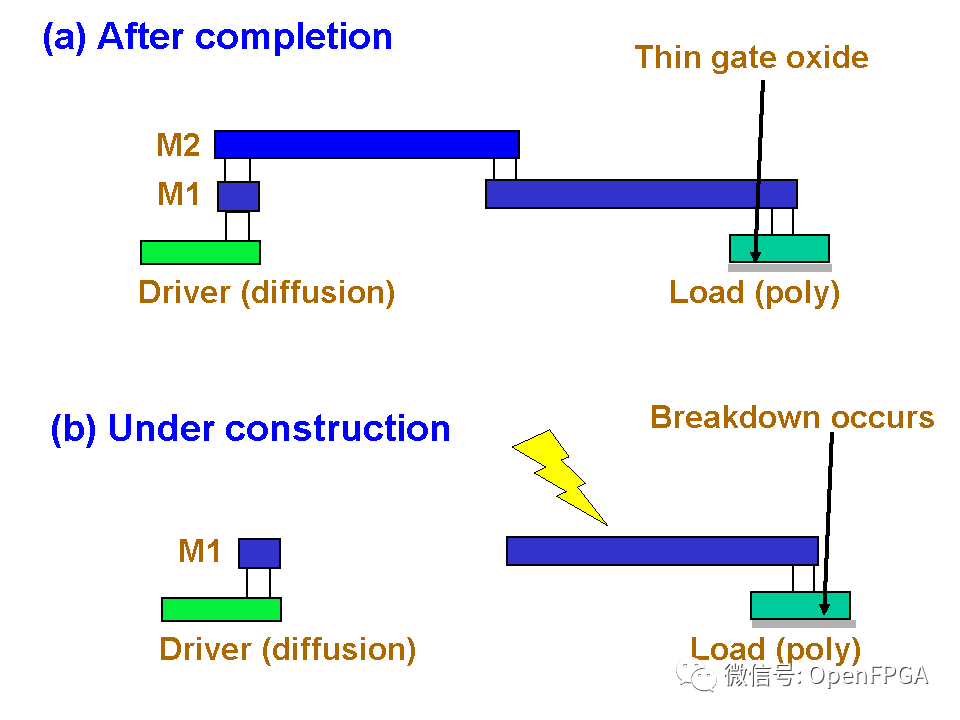

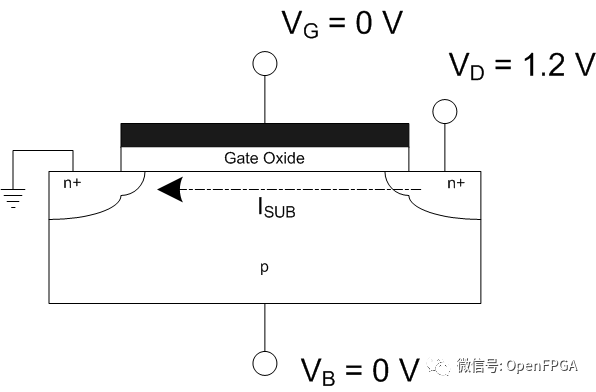

Antenna effect: Plasma induced gate oxide damage that can occur during semiconductor processing. 天线效应-在半导体加工过程中可能发生的等离子引起的栅极氧化物损坏。

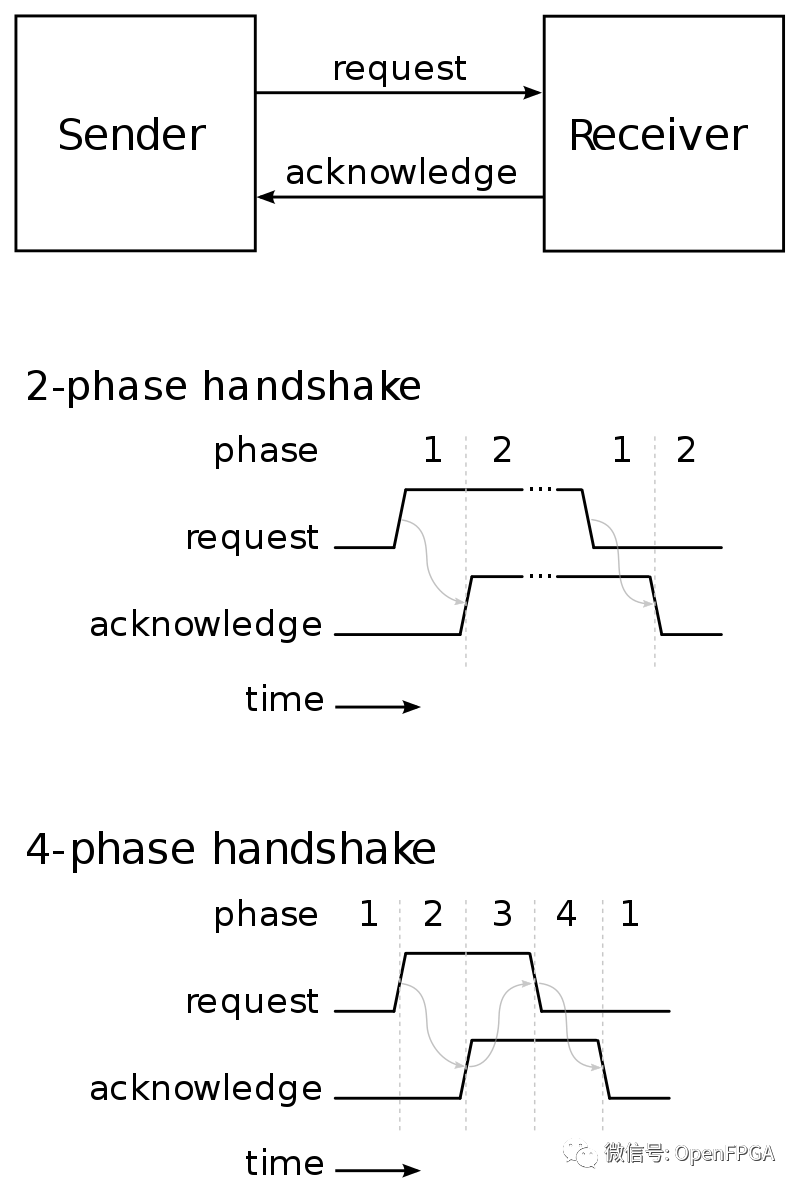

Asynchronous logic: Logic not governed by a clock circuit or global clock. 异步逻辑-不受时钟电路或全局时钟控制的逻辑。

ATPG: Automatic test pattern generation 自动测试模式生成

BIST: Built in Self Test 内置自检

Chip: A set of electronic circuits on one small plate ("chip") of semiconductor material, normally silicon. 芯片

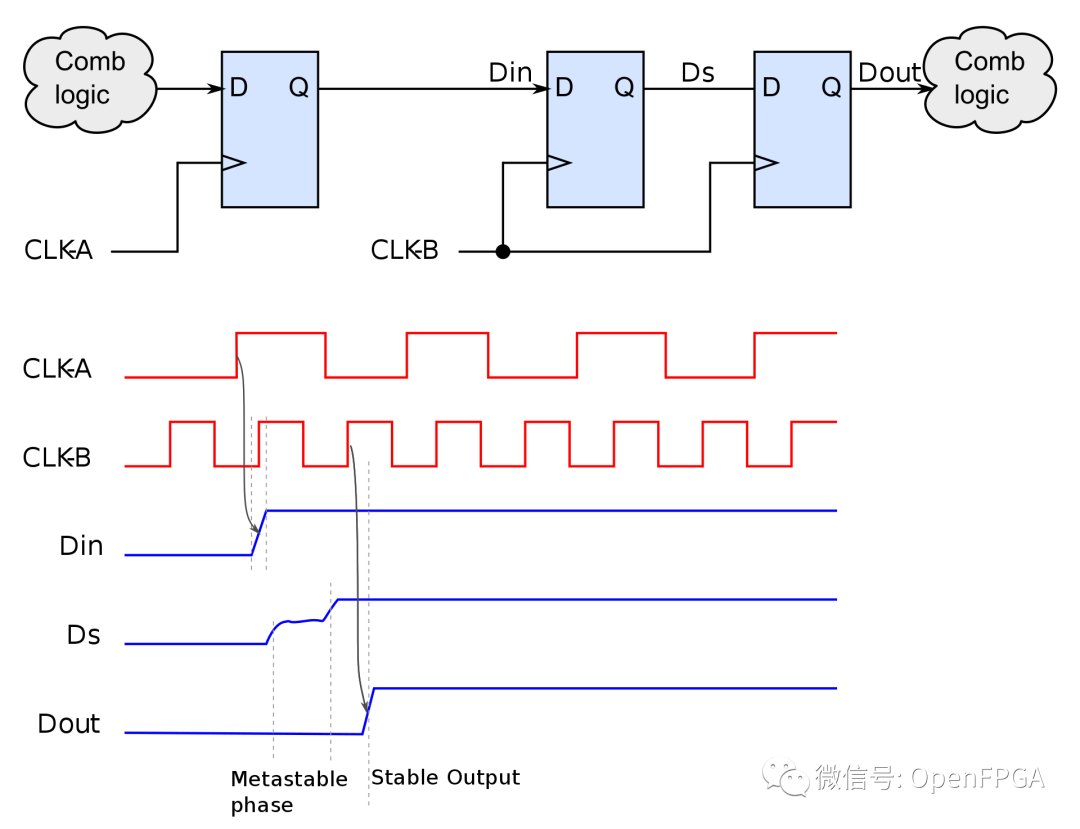

Clock domain crossing: Traversal of signal in synchronous digital ssytem from one clock domain to another.时钟域交叉-同步数字系统中的信号从一个时钟域到另一个时钟域的遍历。

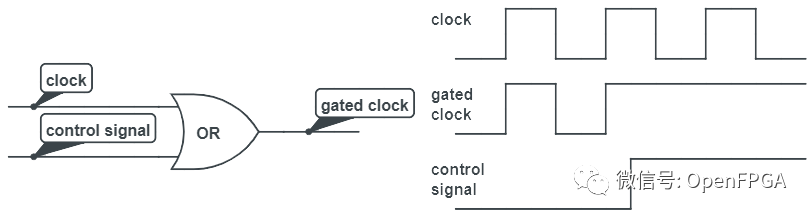

Clock gating: Technique whereby clock in synchronous logic is shut off when idle.门控时钟-同步逻辑中的时钟在空闲时关闭的技术。

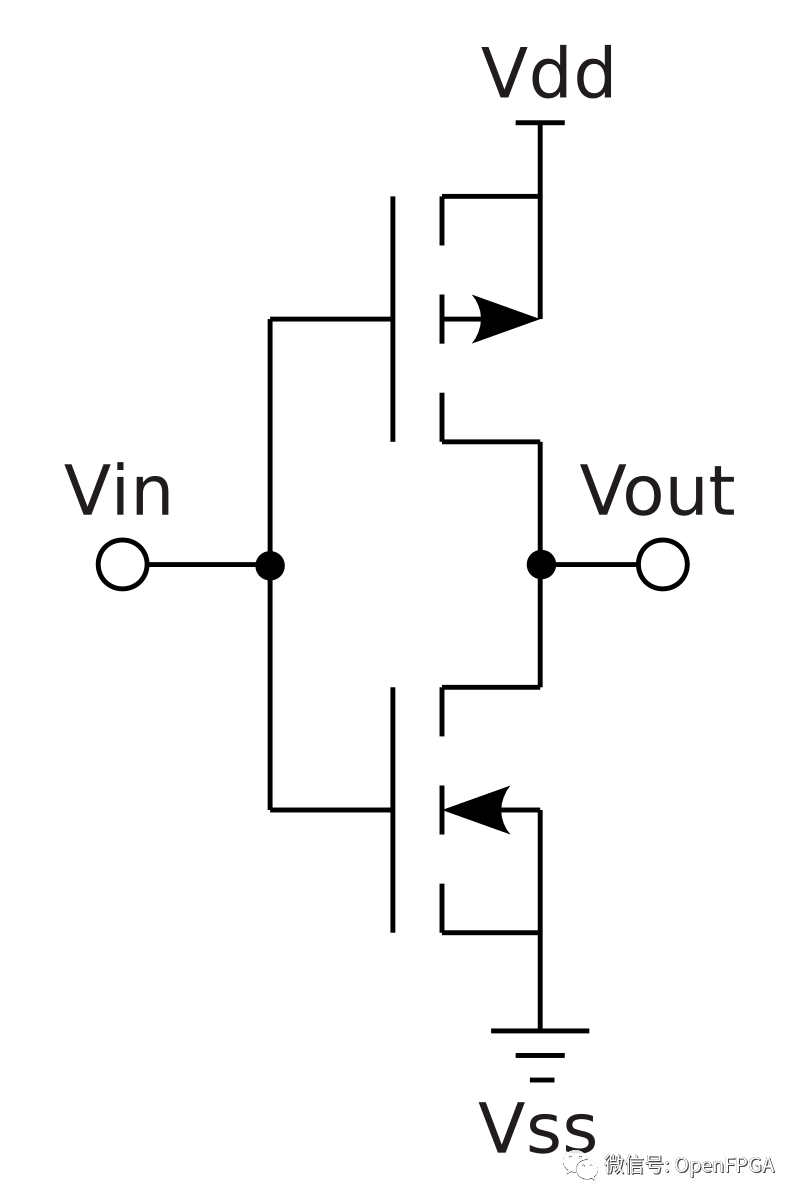

CMOS: Complimentary metal-oxide semiconductor 互补金属氧化物半导体

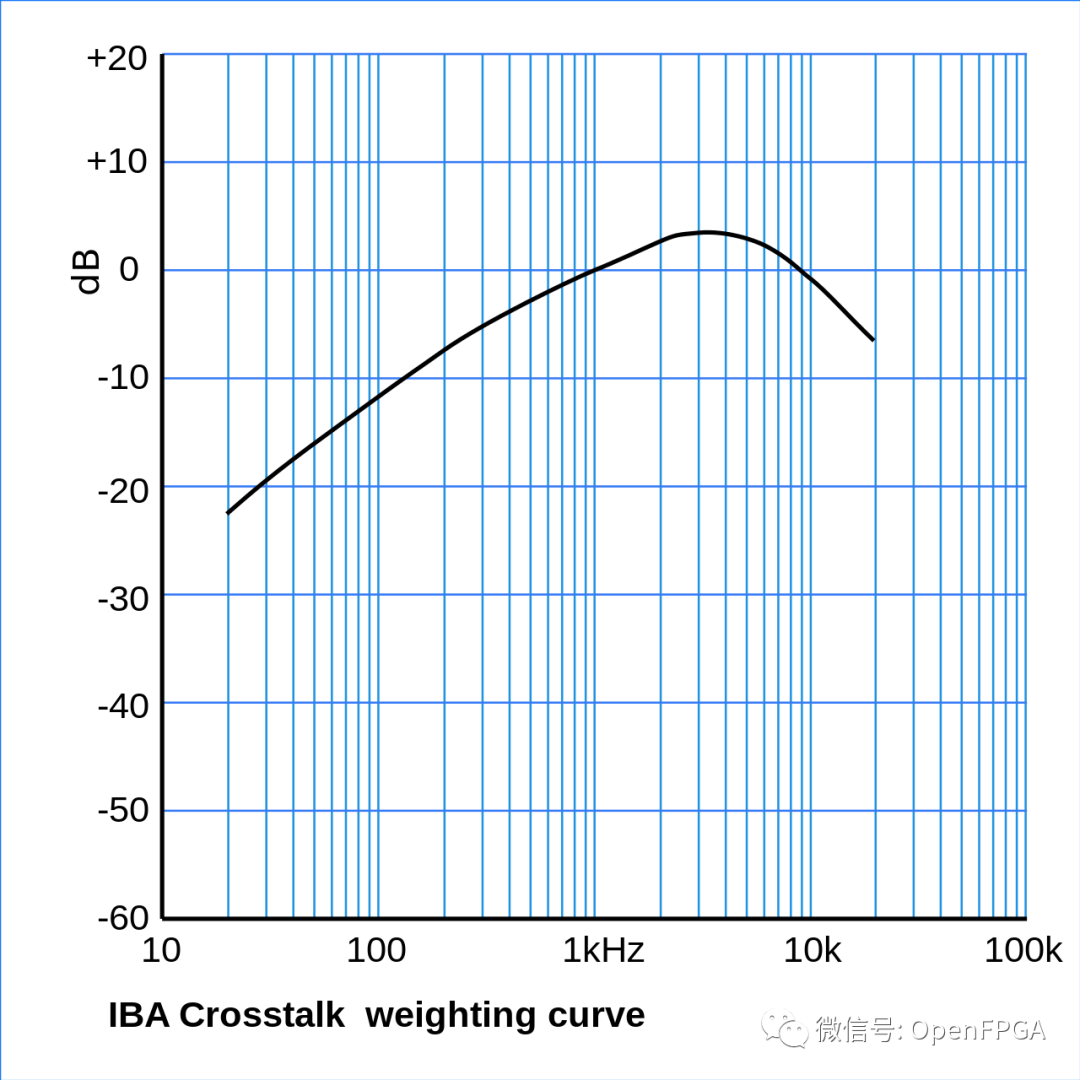

Cross talk: The coupling of nearby signals on a chip, usually through capacitive coupling. 串扰

CTS: Clock tree synthesis 时钟树合成

Domino logic: Fast clocked logic with reduced capacitive load 具有减少容性负载的快速时钟逻辑

DEF: Design Exchange Format for layout 布局的设计交换格式

DFM: Extended DRC rules specifying how to make a high yielding design. 扩展的 DRC 规则,指定如何进行高产量设计。

DFT: Design for test可测试性设计或可测试性设计

Die: Small block of semiconductor material that can be cut ("diced") from a silicon wafer.可以从硅晶片上切割(“切块”)的小块半导体材料

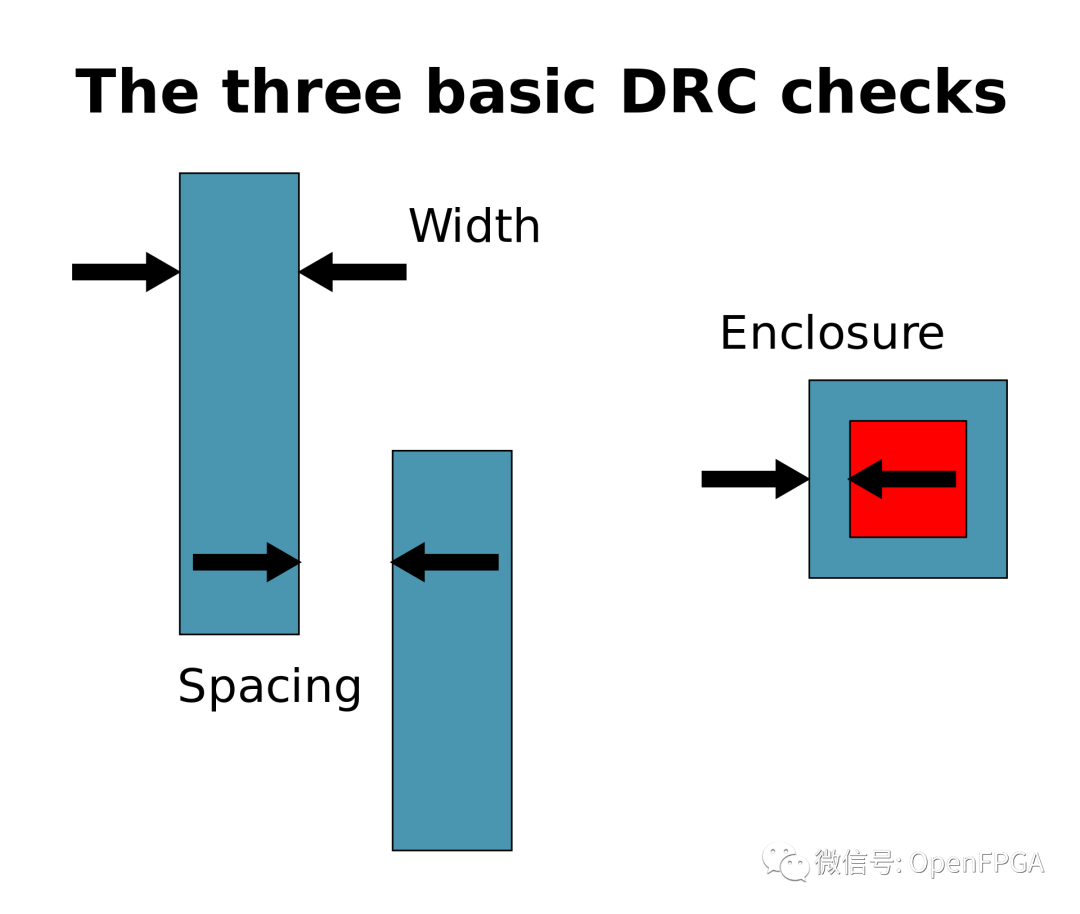

DRC: Design Rule Constraints specifying manufacturing constraints. 指定制造约束的设计规则约束

DV: Design verification is the process of verifying that the logic design conforms to specification. 设计验证是验证逻辑设计是否符合规范的过程

ECO: Engineering change order 工程变更单

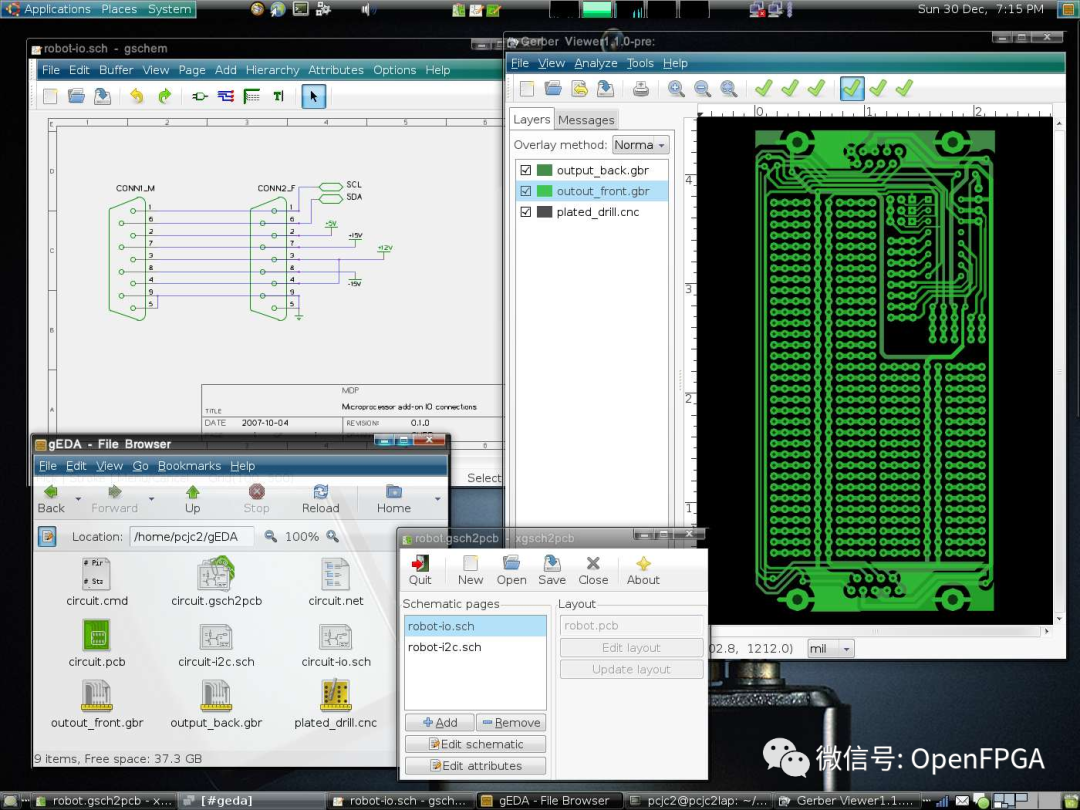

EDA: Electronic Design Automation tools used to enhance chip design productivity. 用于提高芯片设计生产力的电子设计自动化工具

EDA companies: List of EDA companies EDA 公司

Electromigration: Transport of material caused by the gradual movement of the ions in a conductor. 由导体中的离子逐渐运动引起的物质传输。

EMI: Electromagnetic interference. 电磁干扰

ESD: Electrostatic discharge is the sudden flow of electricity between two electrically charged objects. 静电放电是两个带电物体之间的突然电流流动

Fabless: The design and sale of semiconductor devices while outsourcing the manufacturing to 3rd party. 半导体设备的设计和销售,同时将制造外包给第三方-无晶圆制造是硬件设备和半导体芯片的设计和销售,同时将其制造(或晶圆厂)外包给称为半导体代工厂的专业制造商.

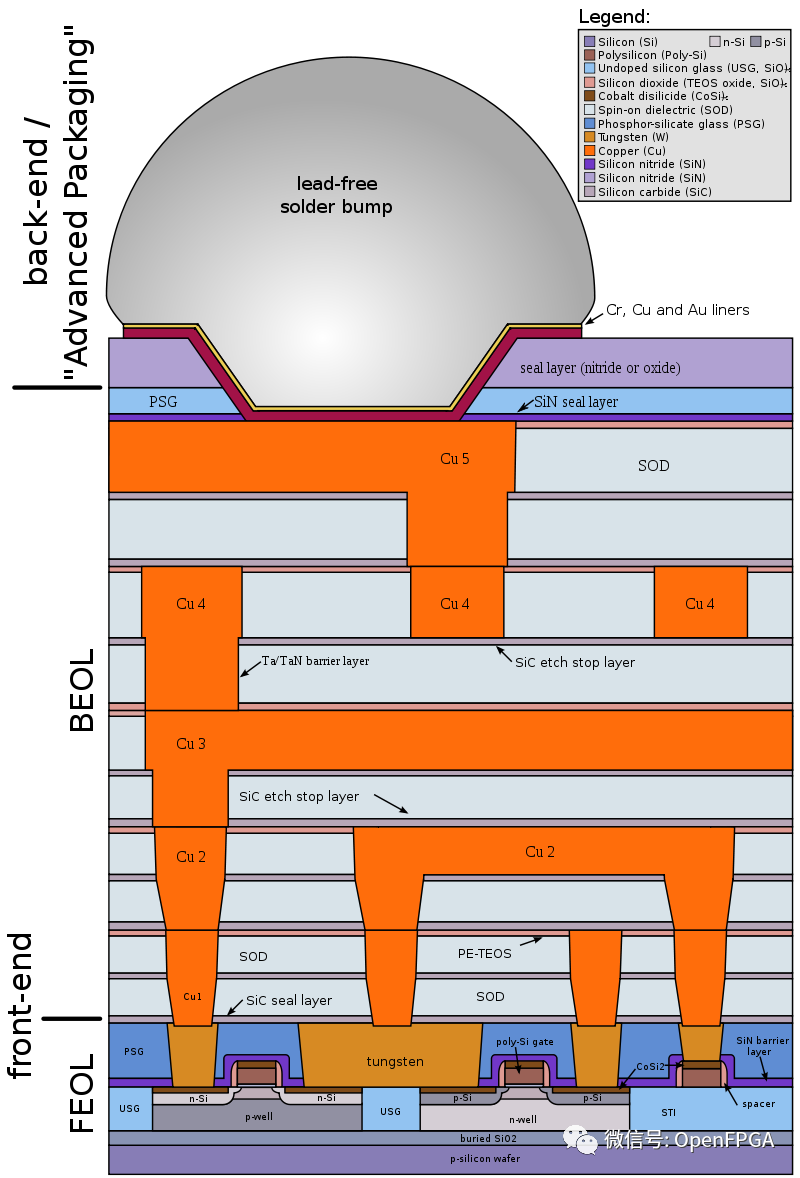

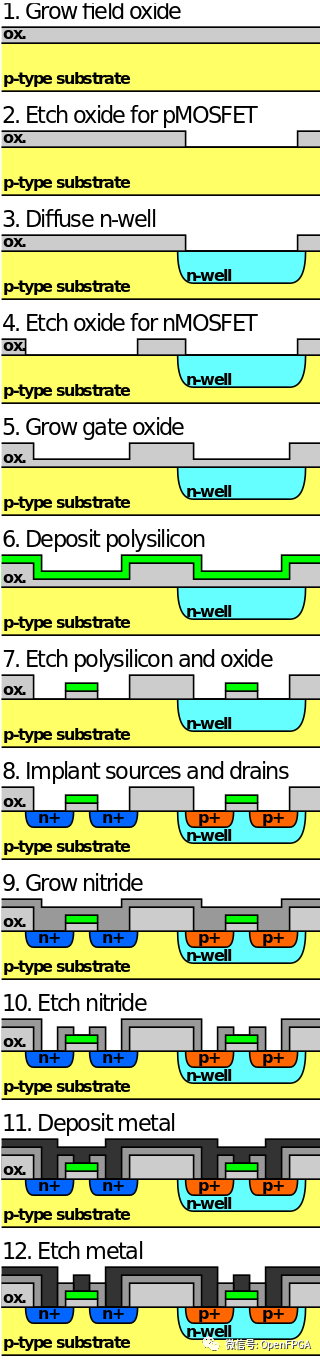

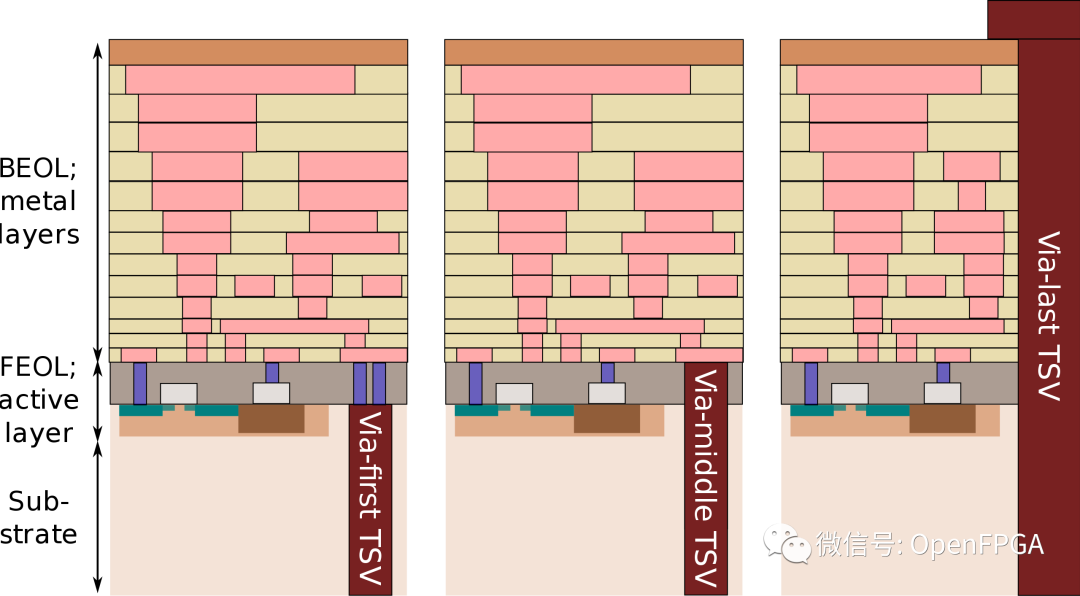

FEOL: Front end of line processing. Includes all chip processing up to but not including metal interconnect layers. 生产线前端处理。包括所有芯片处理,但不包括金属互连层。

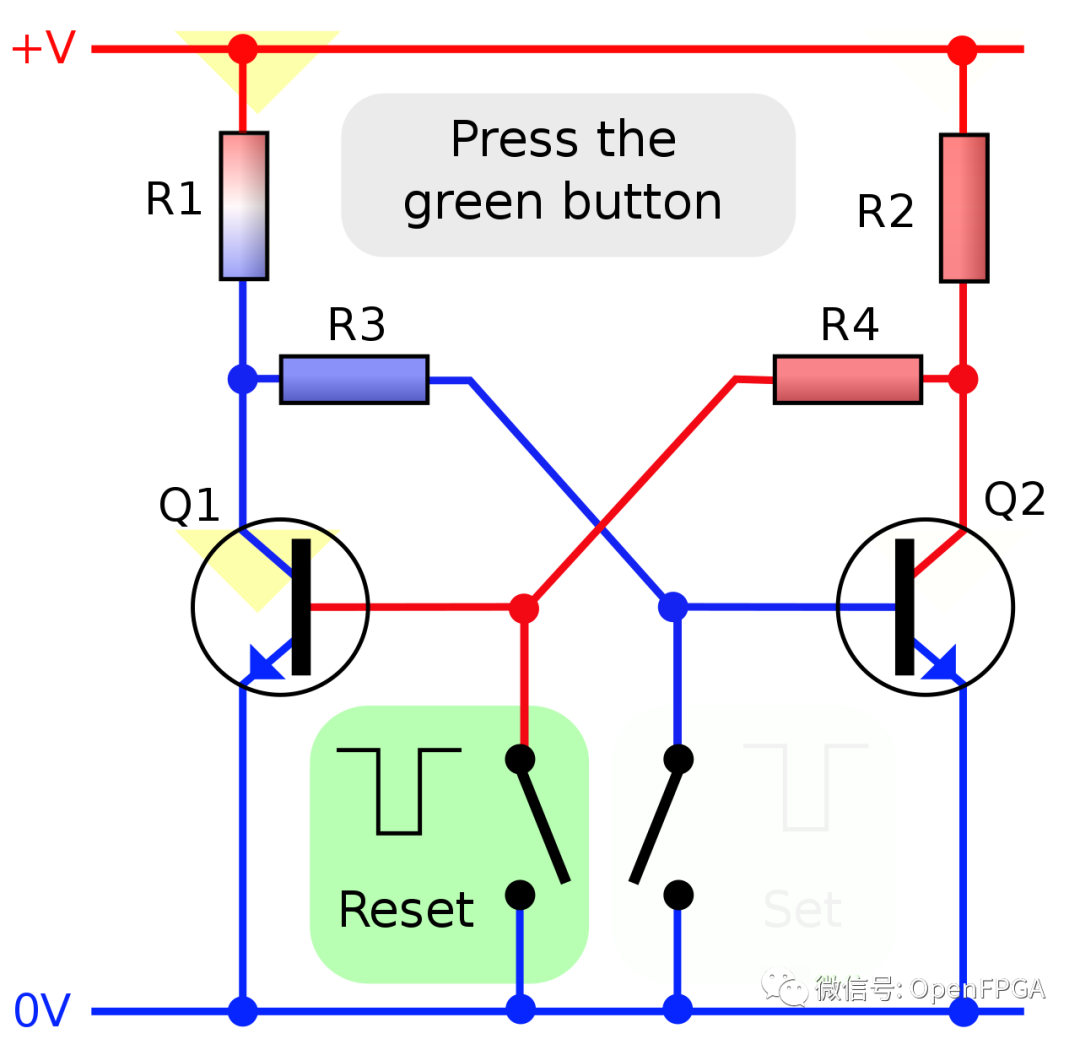

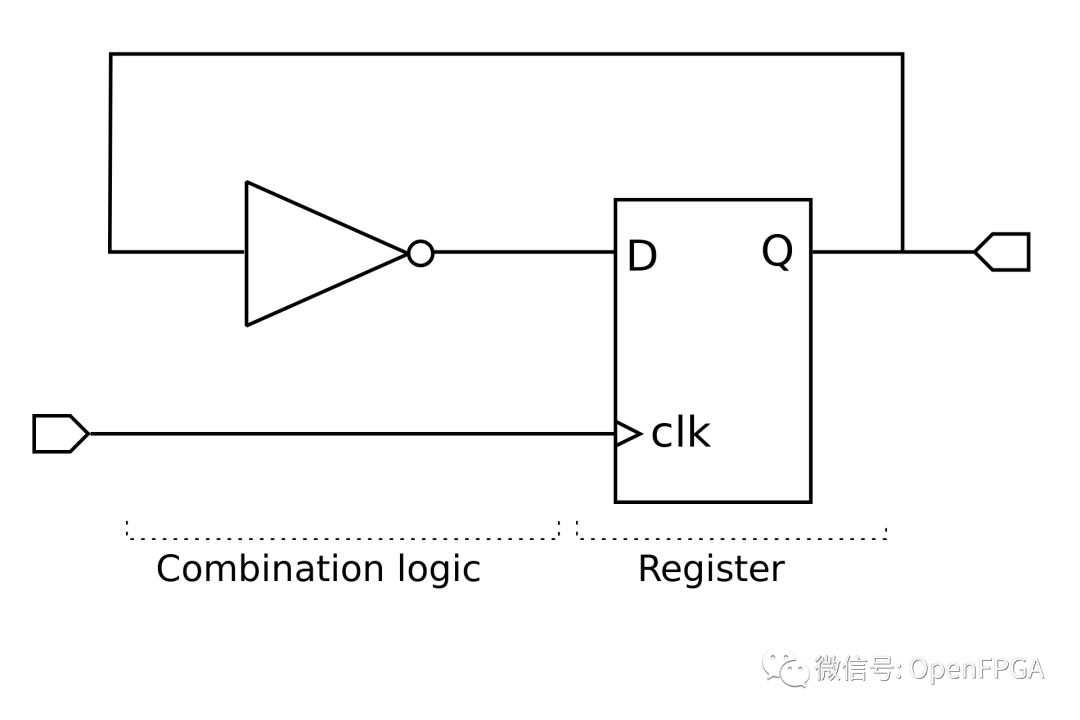

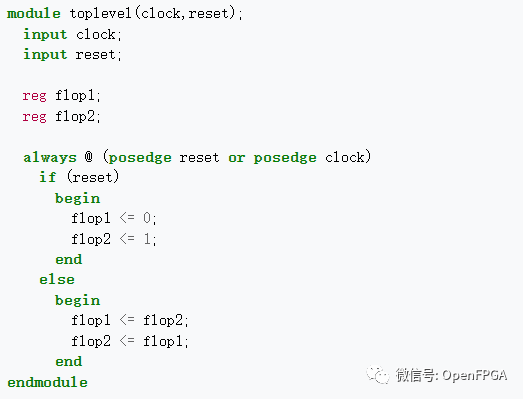

Flip-flop: A clocked circuit that has two stable states and can be used to store state information. 触发器

Foundry: Semiconductor company offering manufacturing services. 提供制造服务的半导体公司

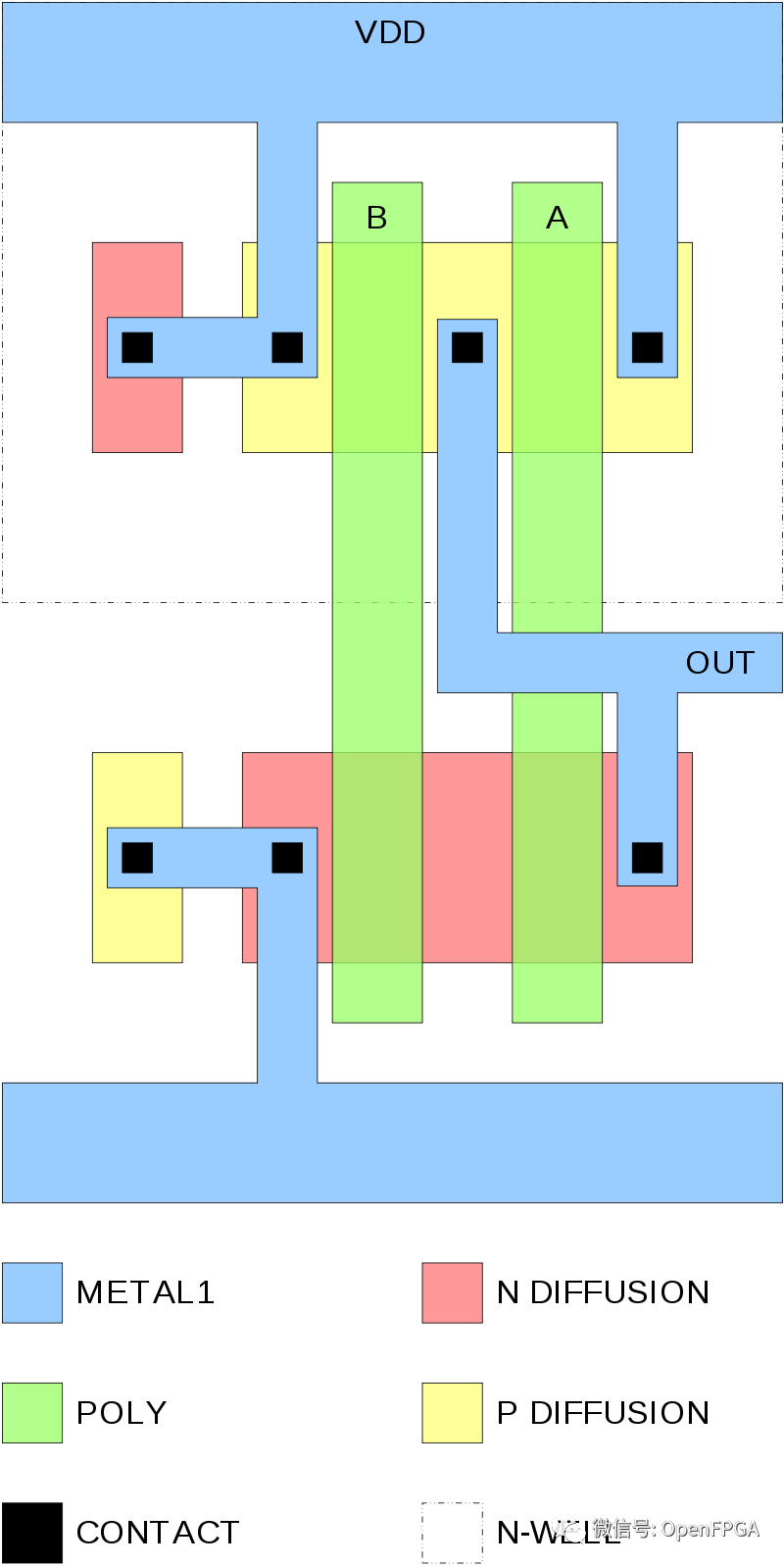

Full custom design: Design methodology involving layout and interconnection of individual transistors. 完全定制设计-涉及各个晶体管的布局和互连的设计方法

GDSII: Binary format of design database sent to foundry. 发送制造厂的设计数据库的二进制格式

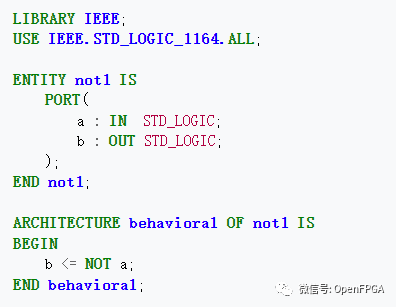

HDL: Specialized hardware description lanaguage for describing electronic circuits. 用于描述电子电路的专用硬件描述语言

Hold time: Minimum time synchronous input should hold steady after clock event. 时钟事件后同步输入应保持稳定的最短时间

IP: Semiconductor reusable design blocks containing author's Intellectual Property. 含作者知识产权的半导体可重复使用设计块

IP Vendors: List of commercial semiconductor IP vendors. IP 供应商

ISI: Intersymbol interference 符号间干扰( ISI ) 是一种信号失真形式,其中一个符号会干扰后续符号

Jitter: Deviation from perfect periodicity. 偏离完美的周期性

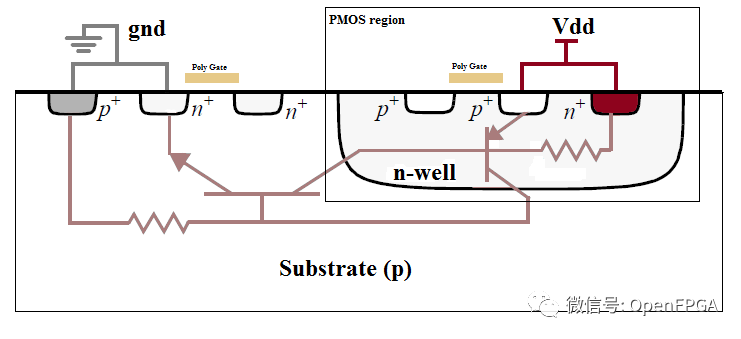

Latchup: Short circuit due to creation of a low-impedance path between the power supply rails of a circuit. 闩锁-由于在电路的电源轨之间创建低阻抗路径而引起的短路

Layout: Physical representation of an integrated circuit. 布局-集成电路的物理表示

LEF: Standard Cell Library Exchange Format layout.标准单元库交换格式布局。

Logical Effort: Technique used to normalize (and optimize) digital circuits speed paths. Logical Effort是Ivan Sutherland和Bob Sproull在 1991 年创造的一个术语,是一种用于估计CMOS电路延迟的简单技术

LVS: Layout Versus Schematic software checks that the layout is identical to the netlist.LVS : Layout Versus Schematic 软件检查布局是否与网表相同。

Mask Works: Copyright law dedicated to 2D and 3D integrated circuit "layouts". “掩模工作”-专门针对 2D 和 3D 集成电路“布局”的版权法。

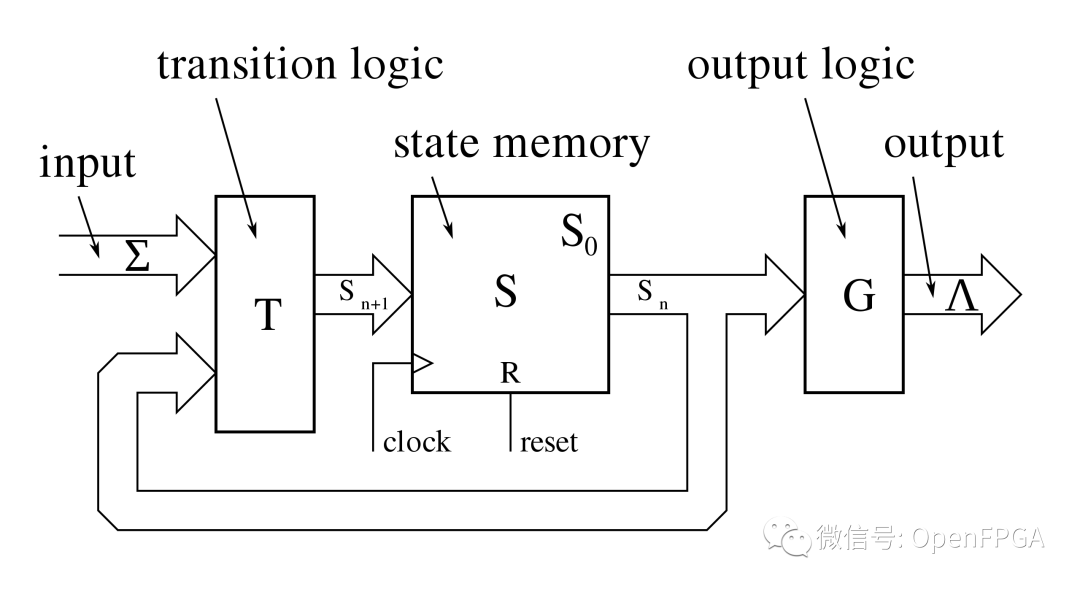

Mealy machine: A finite state machine whose outputs depend on current state and the current inputs. 一种有限状态机,其输出取决于当前状态和当前输入。

Metastability: Ability of a digital electronic system to persist for an unbounded time in an unstable equilibrium. 数字电子系统在不稳定平衡中持续无限时间的能力。

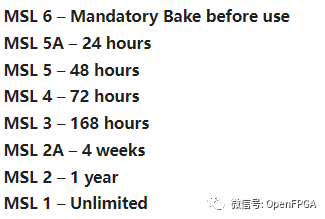

MLS: Packaging and handling precautions for some semiconductors. 湿气敏感度级别与某些半导体的包装和处理注意事项有关。MSL 是针对湿度敏感设备可暴露于室内环境条件(1 级为 30 °C/85%RH;所有其他级别为 30 °C/60%RH)的时间段 的电子标准。

Moore Machine: Finite state machine whose outputs depend only on its current state.Moore型有限状态机,其输出仅取决于其当前状态。

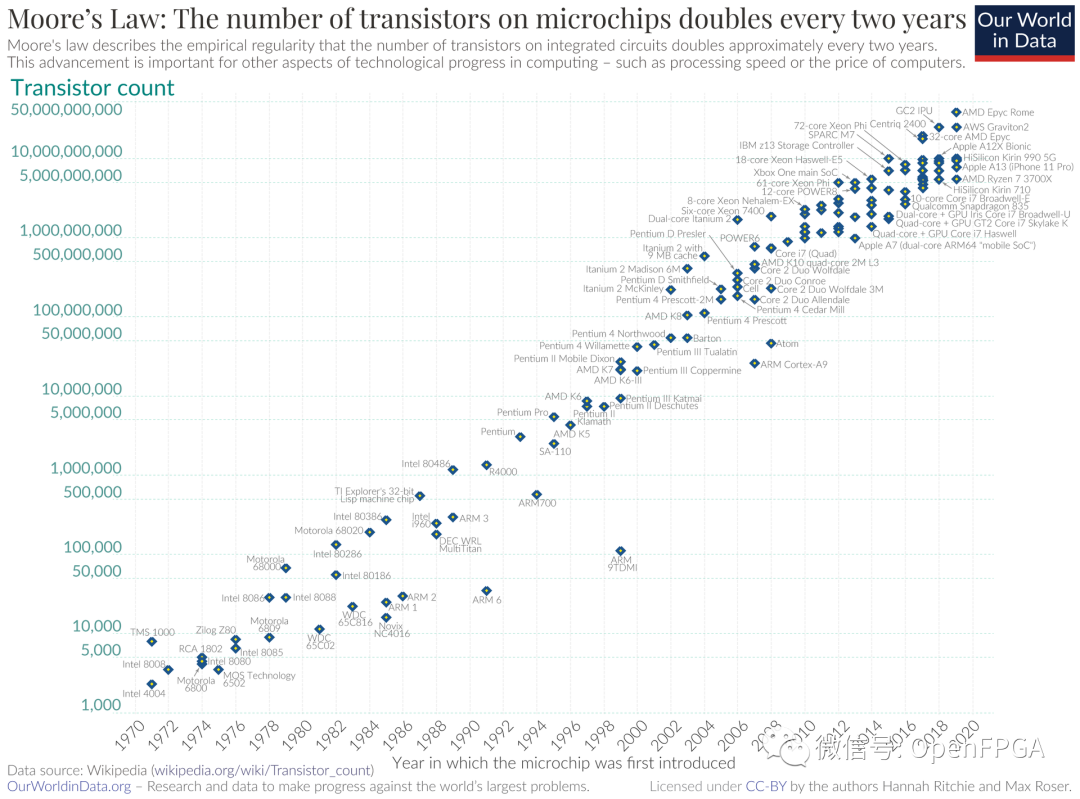

Moore's Law: Observation by Moore that the number of transistors in an IC doubles approximately every two years. 摩尔定律-摩尔观察到,IC 中的晶体管数量大约每两年翻一番。

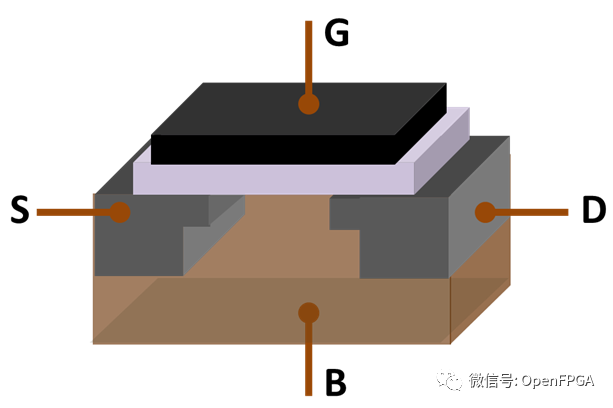

MOSFET: Metal oxide field effect transistor. 金属氧化物场效应晶体管。

MOSIS: Foundry service project offering MPWs and low volume manufacturing. 提供MPW和小批量制造的铸造服务项目。

MPW: Multi-project wafer service that integrates multiple designs on one reticle (aka "shuttle"). 多项目芯片( MPC ) 和多项目晶圆( MPW ) 半导体制造安排允许客户在多个设计或项目之间共享掩模和微电子 晶圆制造成本

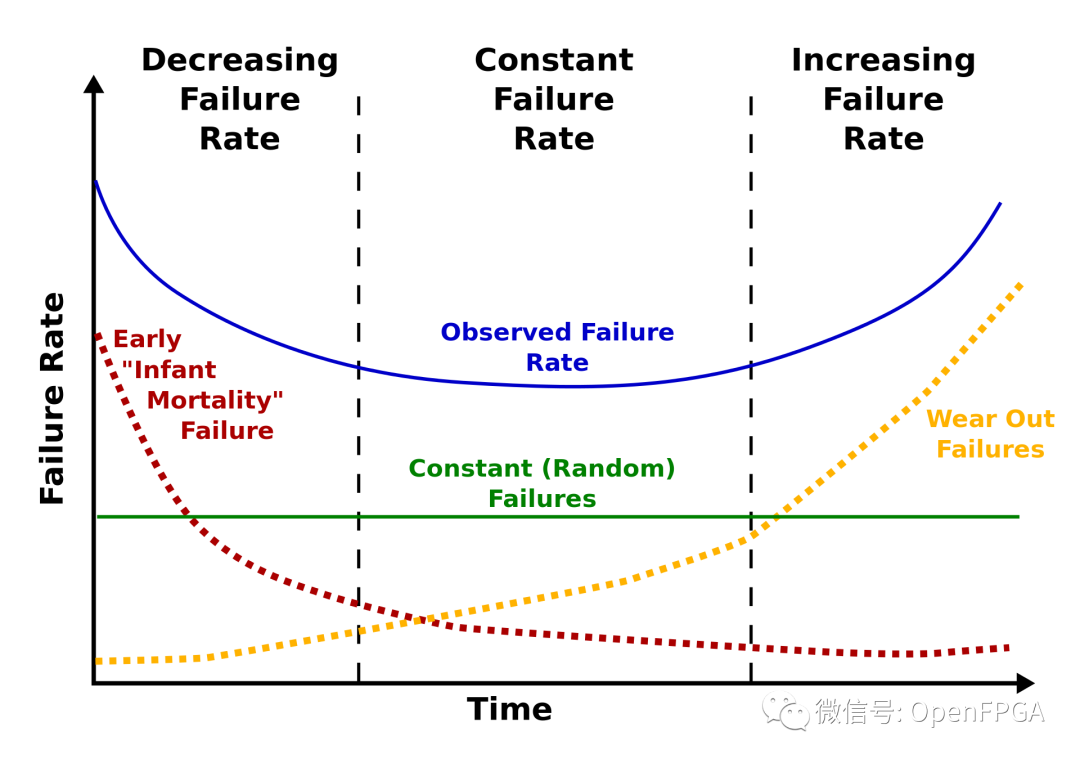

MTBF: Mean time between failures. 平均故障间隔时间。

Multi-threshold CMOS: CMOS technology with multiple transistor types with different threshold voltages. 多阈值 CMOS:具有不同阈值电压的多种晶体管类型的 CMOS 技术。

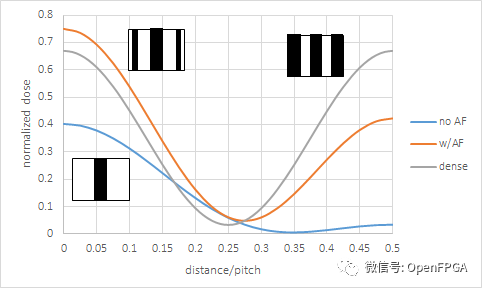

Optical proximity correction: Technique used to compensate for semiconductor diffraction/process effects. 光学邻近校正-用于补偿半导体衍射/工艺效应的技术。

Pass Transistor Logic: Logic that connects input to non-gate terminal of mosfet transistor. 将输入连接到mosfet晶体管的非栅极端子的逻辑

Physical design: Physical design flow ("layout").物理设计流程(“布局”)。

PDK: Process design kits consisting of a minimum set of files needed to design in a specific process. 流程设计工具包,包含在特定流程中进行设计所需的最少文件集

Power gating: Technique used to reduce leakage/standby power by shutting of the supply to the circuit. 电源门控:用于通过关闭电路电源来减少泄漏/待机功率的技术

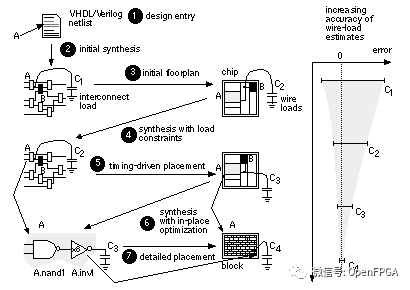

P&R: Automated Place and Route of a circuit using an EDA tool. 使用 EDA 工具自动布局和布线电路

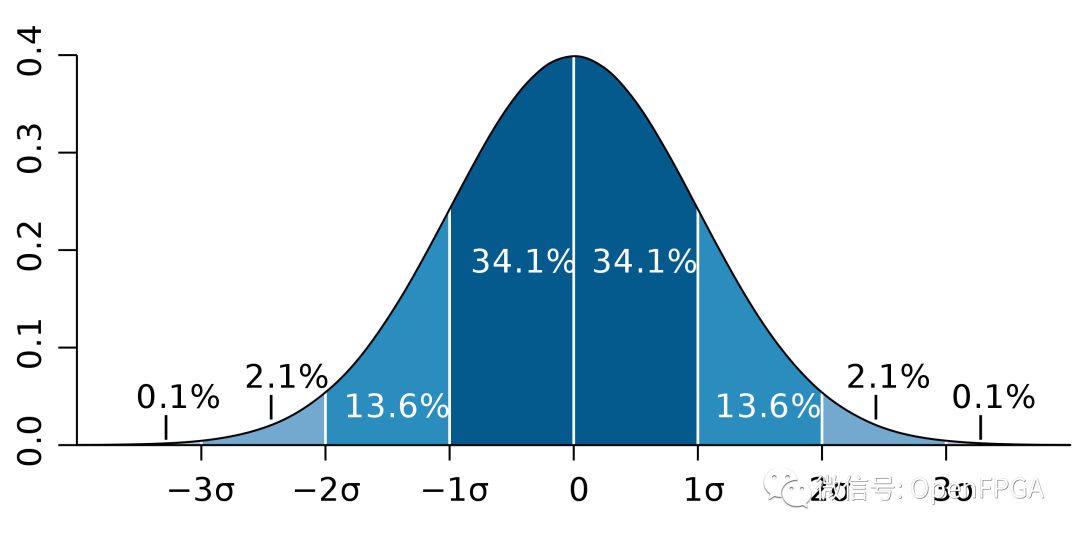

PVT Corners: Represents the extreme process, voltage, temperature that could occur in a given semiconductor process. 表示给定半导体工艺中可能出现的极端工艺、电压、温度

Radiation Hardening: Act of making devices resistant to damage caused by ionizing radiation. 辐射硬化是使电子元件和电路能够抵抗由高水平电离辐射(粒子辐射和高能电磁辐射)引起的损坏或故障的过程

RTL: Design abstraction for digital circuit design. 寄存器传输级( RTL ) 是一种设计抽象,它根据硬件寄存器之间的数字信号(数据)流以及对这些信号执行 的逻辑操作对同步 数字电路进行建模

Setup time: Minimum time synchronous input should be ready before clock event. 建立时间-最小时间同步输入应在时钟事件之前准备好

SEU: Change of state caused by one single ionizing particle (ions, electrons, photons...). 由单个电离粒子(离子、电子、光子......)引起的状态变化

Signoff: The final approval that the design is ready to be sent to foundry for manufacturing. signoff(也写为sign-off )检查是设计在流片之前必须通过的一系列验证步骤的总称

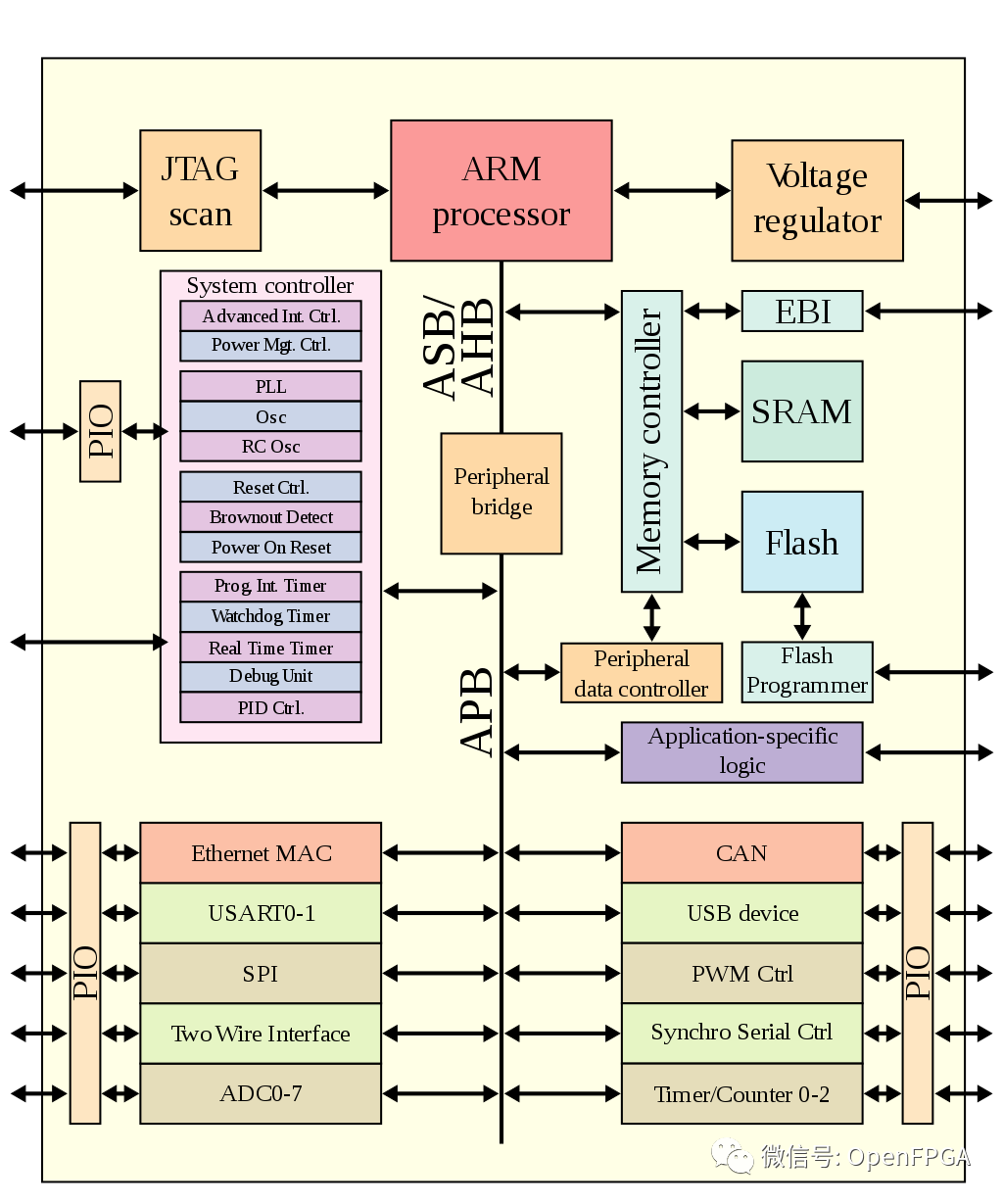

SOC: System On Chip 片上系统

Spice: Open source analog electronic circuit simulator. 开源模拟电子电路模拟器

STA: Method of computing the expected timing of a digital circuit without requiring full circuit simulation. 静态时序分析(STA)

Standard Cell Design: Design process relying on a fixed set of standard cells. 标准单元设计-设计过程依赖于一组固定的标准单元

Subthreshold Leakage: Current between source and drain in MOSFET when transistor is "off". 亚阈值泄漏-晶体管“关闭”时 MOSFET 源极和漏极之间的电流

Synchronous logic: Logic whose state is controlled by a synchronous clock. 同步逻辑

Synthesis: Translation of high level design description (e.g. Verilog) to a netlist format (e.g. standard cell gate level). 综合-将高级设计描述(例如 Verilog)转换为网表格式(例如标准单元门级)

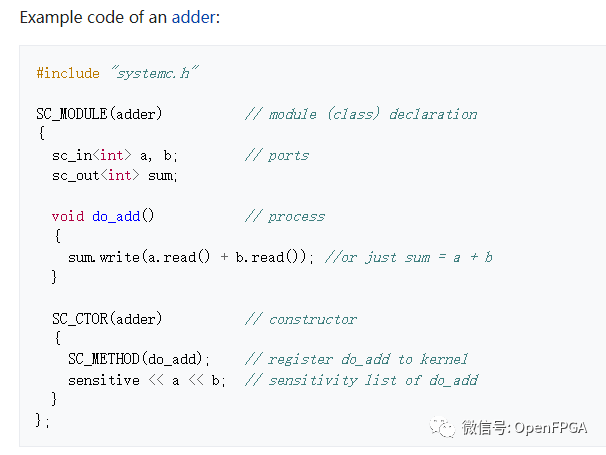

SystemC: Set of C++ classes and macros for simulation. Commonly used for high level modeling and testing. 一组用于模拟的 C++ 类和宏。常用于高级建模和测试

Tape-out: Act of sending photomask chip database ("layout") to the manufacturer. 流片:将光掩模芯片数据库(“布局”)发送给制造商的行为。

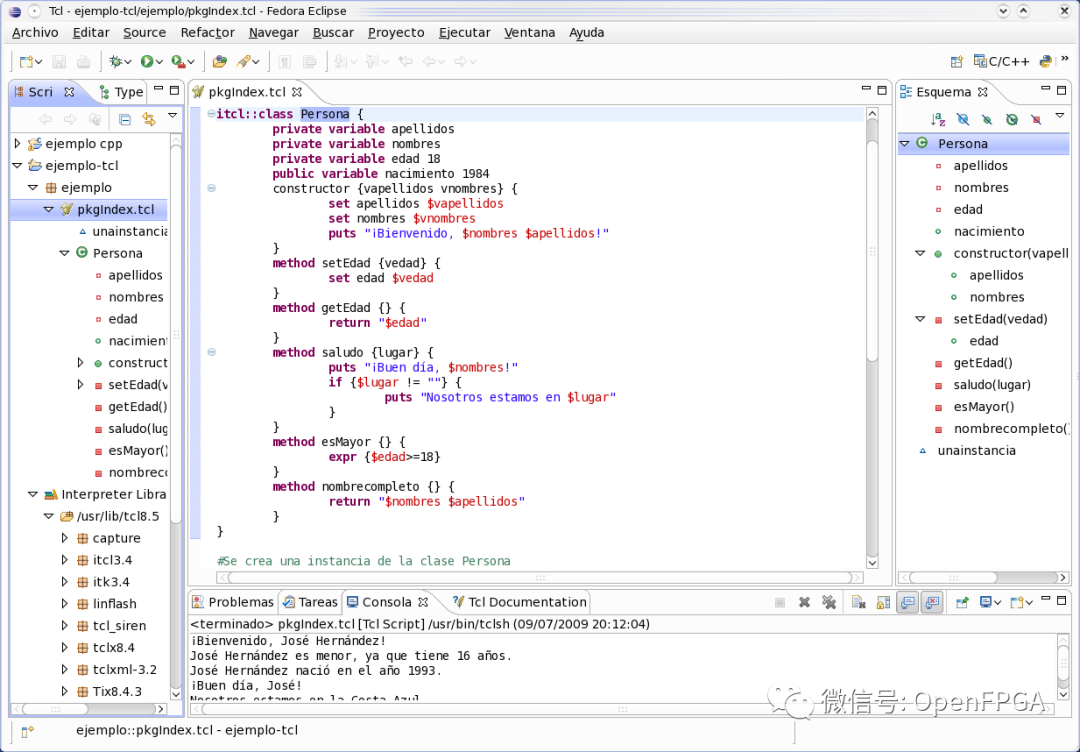

TCL: Scripting language used by most of the leading EDA chip design tools. 大多数领先的 EDA 芯片设计工具使用的脚本语言。

Transistor: A semiconductor device used to amplify/switch electronic signals. 晶体管

Verilog: The dominant hardware description language (HDL) for chip design. 用于芯片设计的主要硬件描述语言 (HDL)

VLSI: Very large Integrated Circuit (somewhat outdated term, everything is VLSI today). 大的集成电路(有点过时的术语,今天一切都是 VLSI)

Von Neumann architecture: Computer architecture in which instructions and data are stored in the same memory. 冯诺依曼架构:指令和数据存储在同一内存中的计算机架构。

Manufacturing制造业

BEOL: Back end of line processing for connecting together devices using metal interconnects. 使用金属互连将设备连接在一起的生产线后端处理。

Dicing: Act of cutting up wafer into individual dies. 切割-将晶圆切割成单个裸片的行为

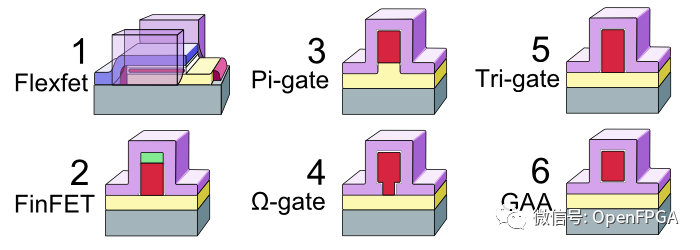

FinFet: Non planar, double-gate transistor. 非平面双栅晶体管

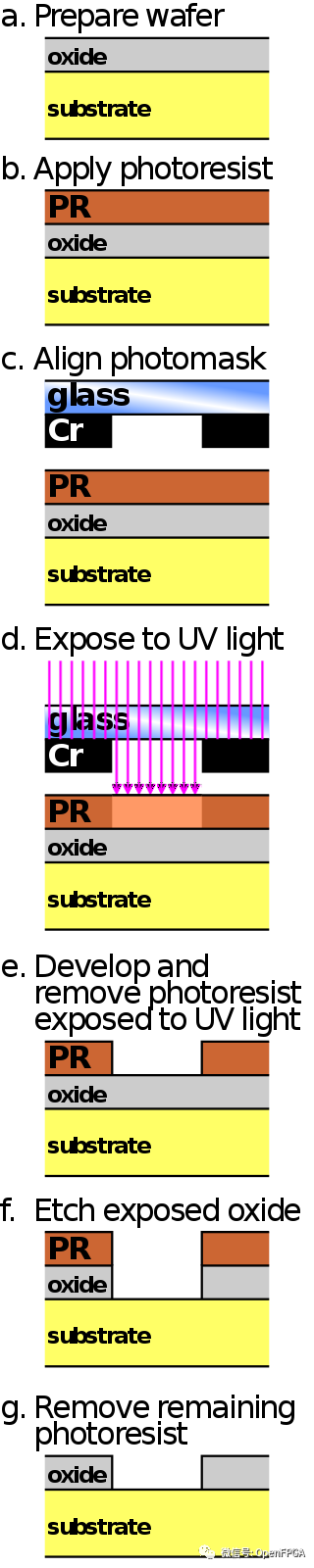

Photo-lithography: Process used in micro-fabrication to pattern parts of a thin film or the bulk of a substrate. 光刻:用于微制造的工艺,用于对薄膜的部分或基板的主体进行图案化。

Photomasks: Opaque plates with holes or transparencies that allow light to shine through in a defined pattern. 光掩模:带有孔或透明胶片的不透明板,可让光线以规定的图案透过。

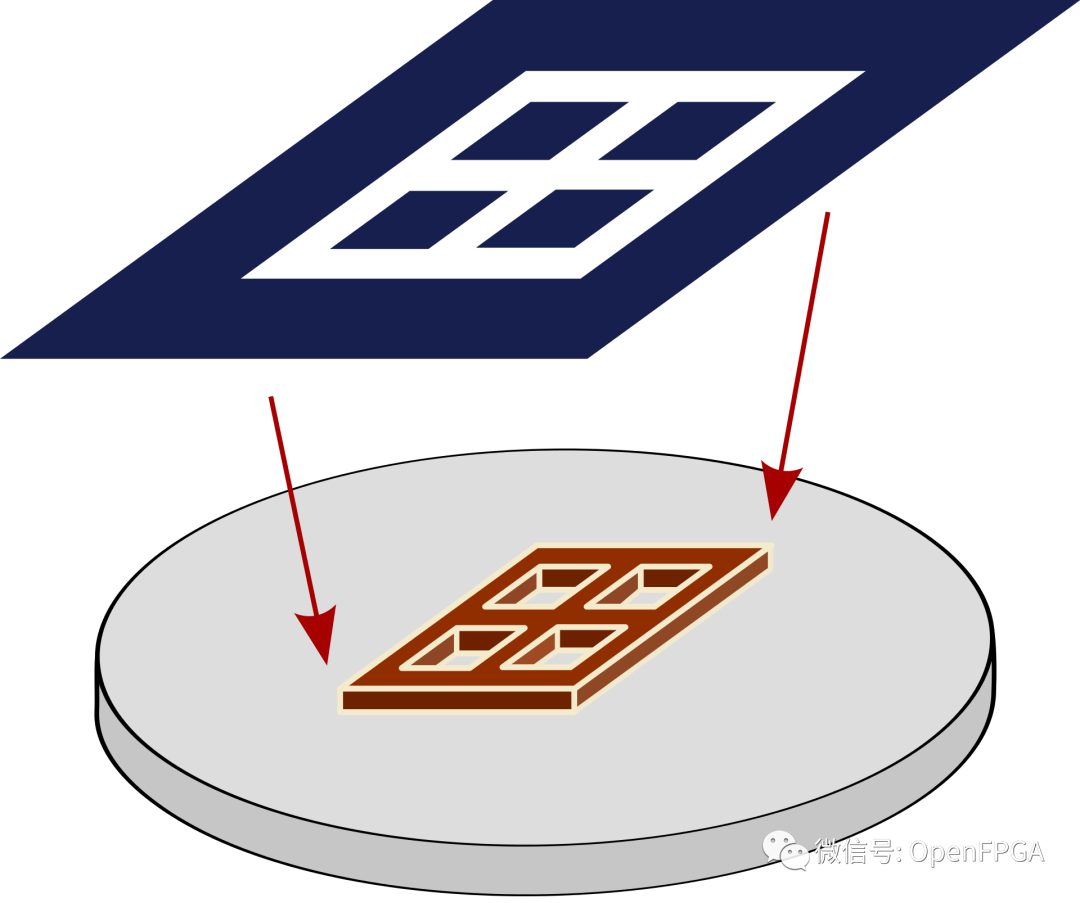

Reticle: A set of photomasks used by a stepper to step and print patterns onto a silicon wafer.标线:步进机使用的一组光掩模,用于在硅晶片上步进和打印图案。

Semiconductor Fabrication: Process used to create the integrated circuits. 半导体制造:用于制造集成电路的工艺。

Silicon: Element (Si), forms the basis of the electronic revolution. 硅:元素 (Si),构成电子革命的基础。

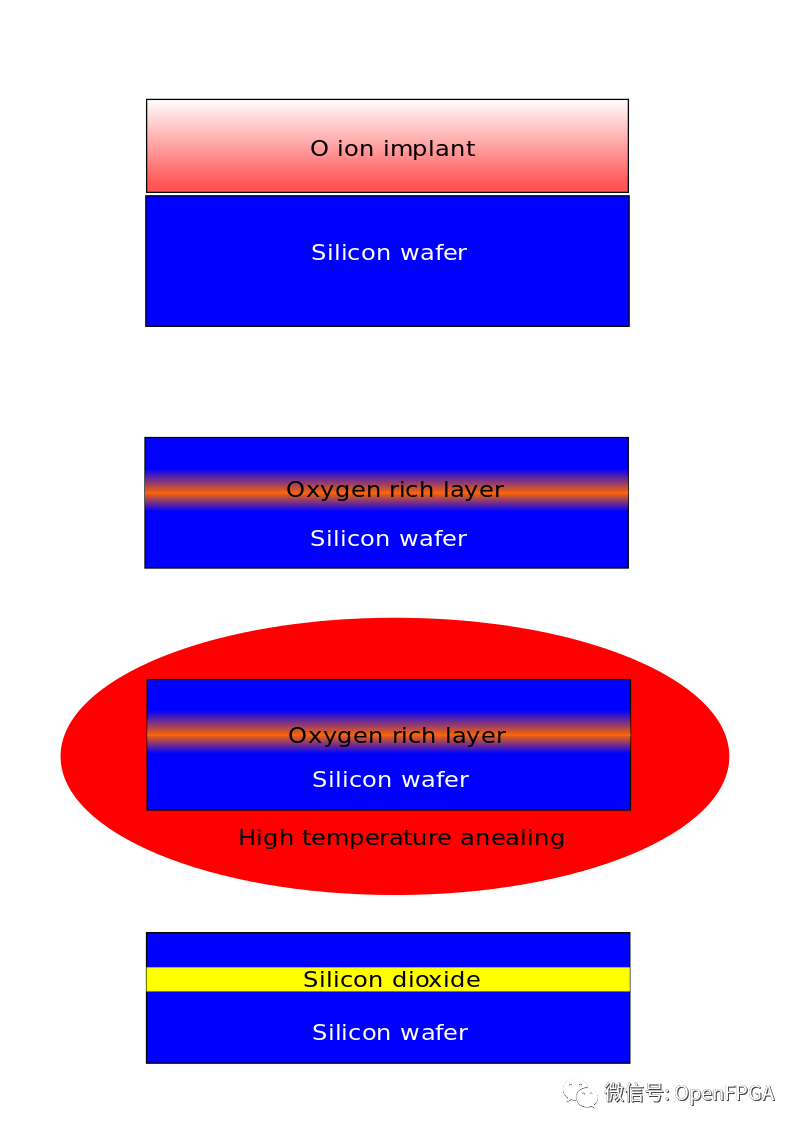

Silicon on insulator: Layered silicon–insulator–silicon with reduced parasitic capacitance. 绝缘体上硅:具有降低寄生电容的层状硅-绝缘体-硅。

Stepper: Machine that passes light through reticle onto the silicon wafer being processed. 步进器:将光通过标线板传递到正在处理的硅晶片上的机器。

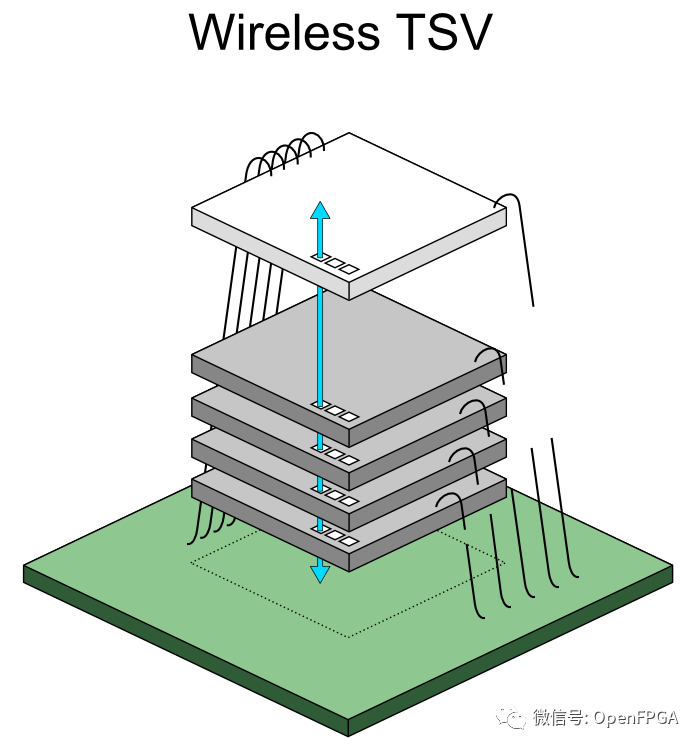

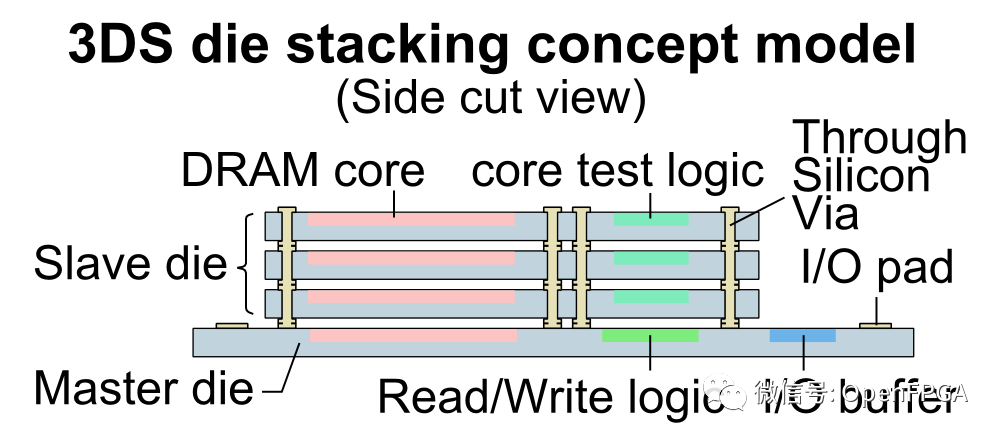

TSV: Vertical electrical connection (via) passing completely through a silicon wafer or die. 硅通孔( TSV ) 或芯片通孔是完全穿过硅晶片或芯片的垂直电连接(通孔)。

Wafer: Thin slice of semiconductor material used in electronics for the fabrication of integrated circuits. 晶片:用于制造集成电路的电子器件中的半导体材料薄片。

Wafer thinning: Wafer thickness reduction to allow for stacking and high density packaging. 晶圆减薄:晶圆厚度减小以允许堆叠和高密度封装。

Packaging封装

3D IC's: The process of stacking integrated circuits and connecting them through TSVs. 通过堆叠硅晶片或裸片并使用例如硅通孔(TSV) 或 Cu-垂直互连

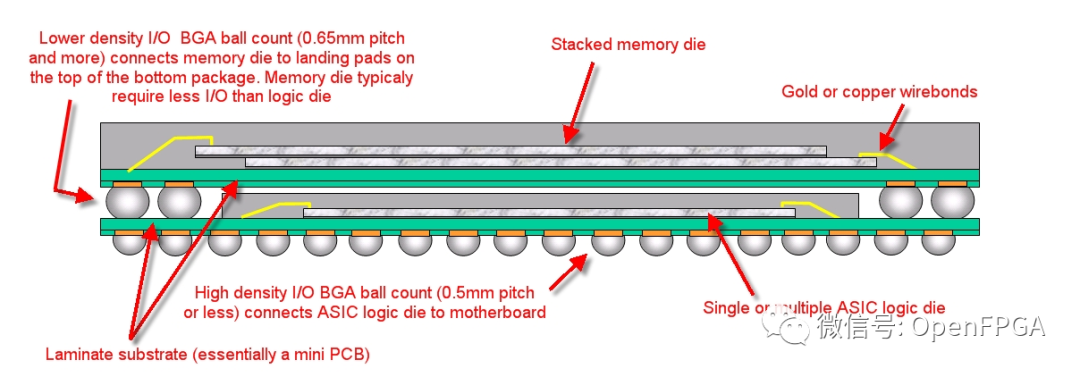

BGA: Ball grid array is a type of surface-mount packaging (a chip carrier) used for integrated circuits. 球栅阵列是一种用于集成电路的表面贴装封装(芯片载体)

BGA substrate: A miniaturized PCB that mates the silicon die to BGA pins. 将硅芯片与 BGA 引脚配对的小型化 PCB

Bumping: Placing of bumps on wafer/dies in preparation for package assembly. 凸块:在晶圆/裸片上放置凸块,为封装组装做准备。

DIMM: Dual in line memory module. 双列直插内存模块。

Flip-chip: Method of bonding a silicon die to package using solder bumps. 使用焊料凸点将硅芯片键合到封装上的方法。

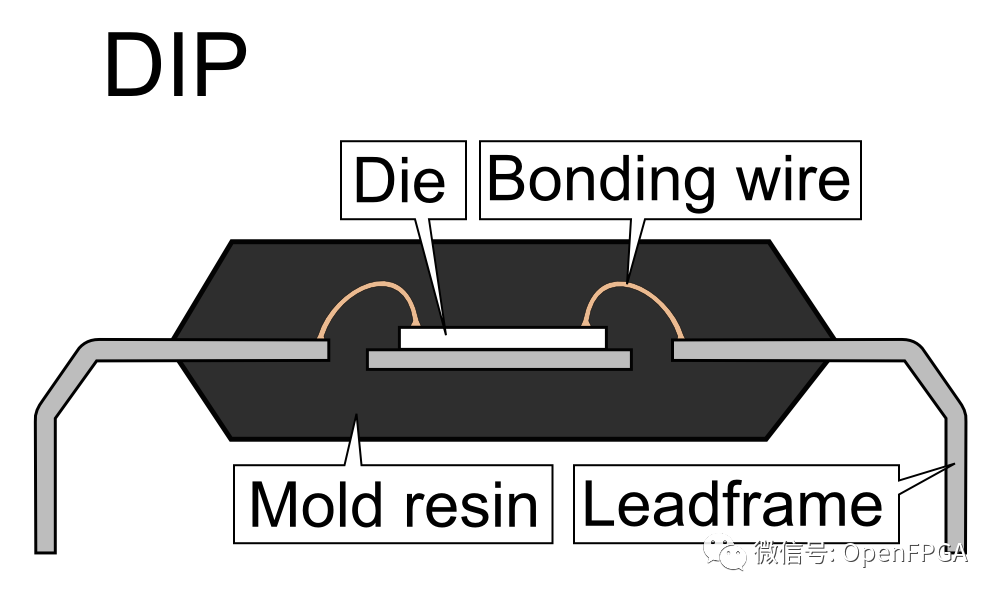

IC Assembly: Semiconductor die is encased in a supporting case "package". IC 组装

Interposer: Electrical interface used to spread a connection to a wider pitch. 用于将连接扩展到更宽间距的电气接口

Heat sink: A passive heat exchanger. 散热器-被动式热交换器。

Heat pipe: Device for efficiently transferring heat between two solid interfaces . 热管-在两个固体界面之间有效传递热量的装置。

KGD: Known Good Die. Dies that have been completely tested at wafer probe. 晶圆测试是半导体器件制造过程中执行的一个步骤。在此步骤中,在将晶圆发送到芯片准备之前执行,晶圆上存在的所有单个集成电路都通过对其应用特殊的测试模式来测试功能缺陷。

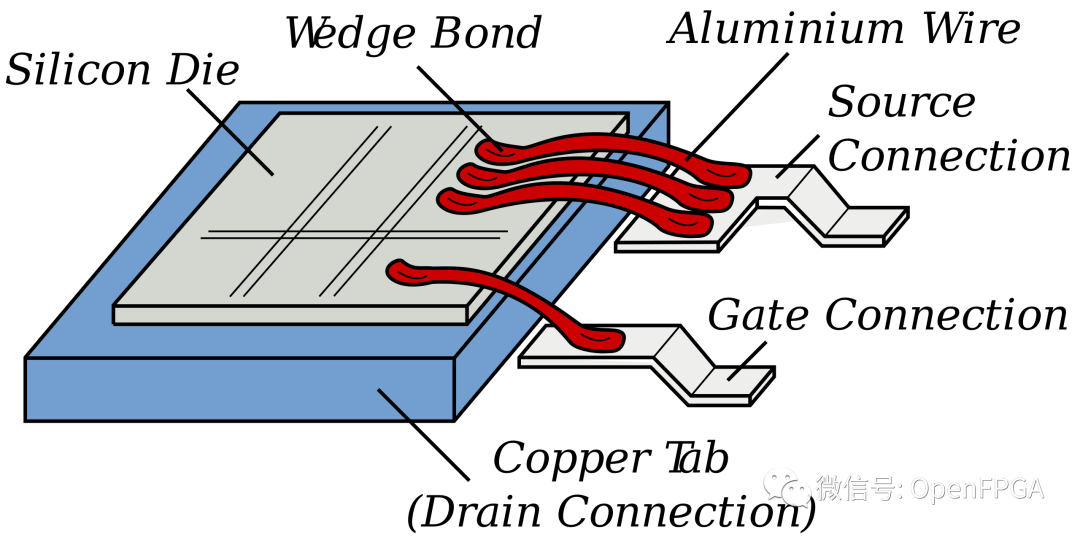

Leadframe: Metal structure inside a chip package that carry signals from the die to the outside. 引线框架:芯片封装内的金属结构,可将信号从芯片传送到外部。

POP: Package on Package

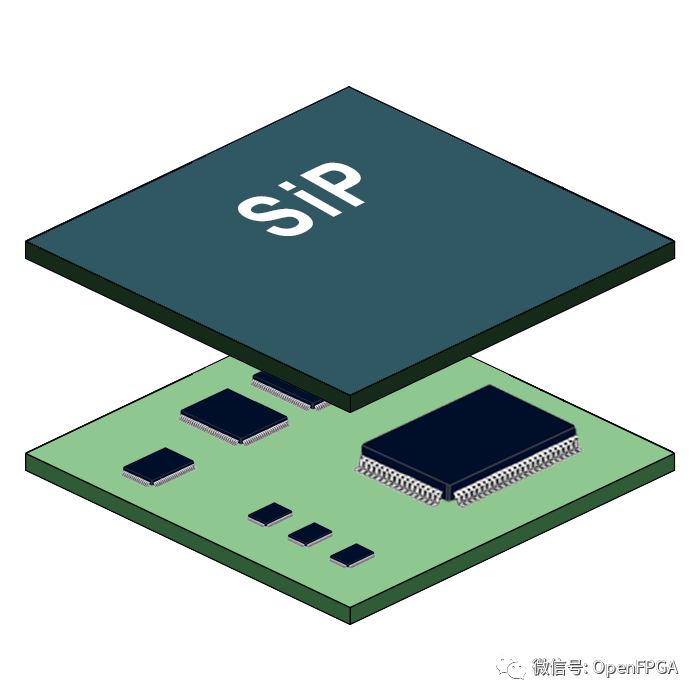

SIP: System In Package 系统封装

SMT: Technique whereby packaged chips are mounted directly onto the PCB surface. 封装芯片安装在 PCB 表面上的技术。

Through-hole: TPackage pins inserted in drilled holes and soldered on opposite side of the board. 通孔

Wirebond: Method of bonding a silicon die to a package using wires. 使用导线将硅芯片与封装结合的方法

WSI: Wafer scale integration 晶圆级集成

Test测试

Arbitrary Waveform Generator: Electronic instrument used to generate arbitrary signal waveforms. 任意波形发生器:用于产生任意信号波形的电子仪器。

ATE: Automatic Test Equipment for testing integrated circuits. 用于测试集成电路的自动测试设备。

Burn-in: Process of screening parts for potential premature life time failures. 老化:筛选零件以发现潜在的过早寿命故障的过程。

DIB: Device Interface Board for interfacing DUT to ATE. Also called DUT board, probe card, load board, PIB. 用于将 DUT 连接到 ATE 的设备接口板。也称为 DUT 板、探针卡、负载板、PIB。

DMM: Electronic instrument for measuring voltage, current, and resistance. 用于测量电压、电流和电阻的电子仪器。

DUT: Device under test 被测设备

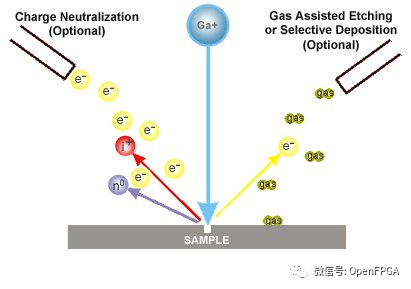

FIB: Focused ion beam 聚焦离子束

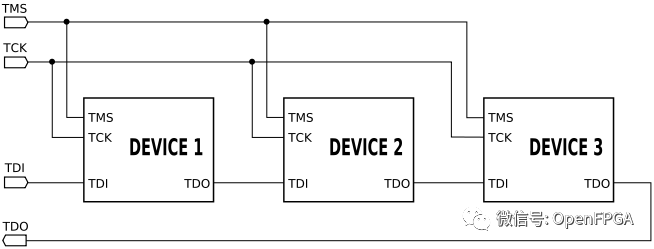

JTAG: Industry standard for verifying and testing/debugging printed circuit boards after manufacturing. 制造后验证和测试/调试印刷电路板的行业标准。

Logic Analyzer: Electronic instrument for capturing multiple digital signal from a system. 逻辑分析仪:用于从系统中捕获多个数字信号的电子仪器。

MCM: Multi-chip Module 多芯片模块

Oscilloscope: Electronic instrument for tracking the change of an electrical signal over time. 示波器:跟踪电信号随时间变化的电子仪器。

Probe Card: A direct interface between electronic test systems and a semiconductor wafer. 探针卡:电子测试系统和半导体晶片之间的直接接口。

SEM: Scanning electron microscope 扫描电子显微镜

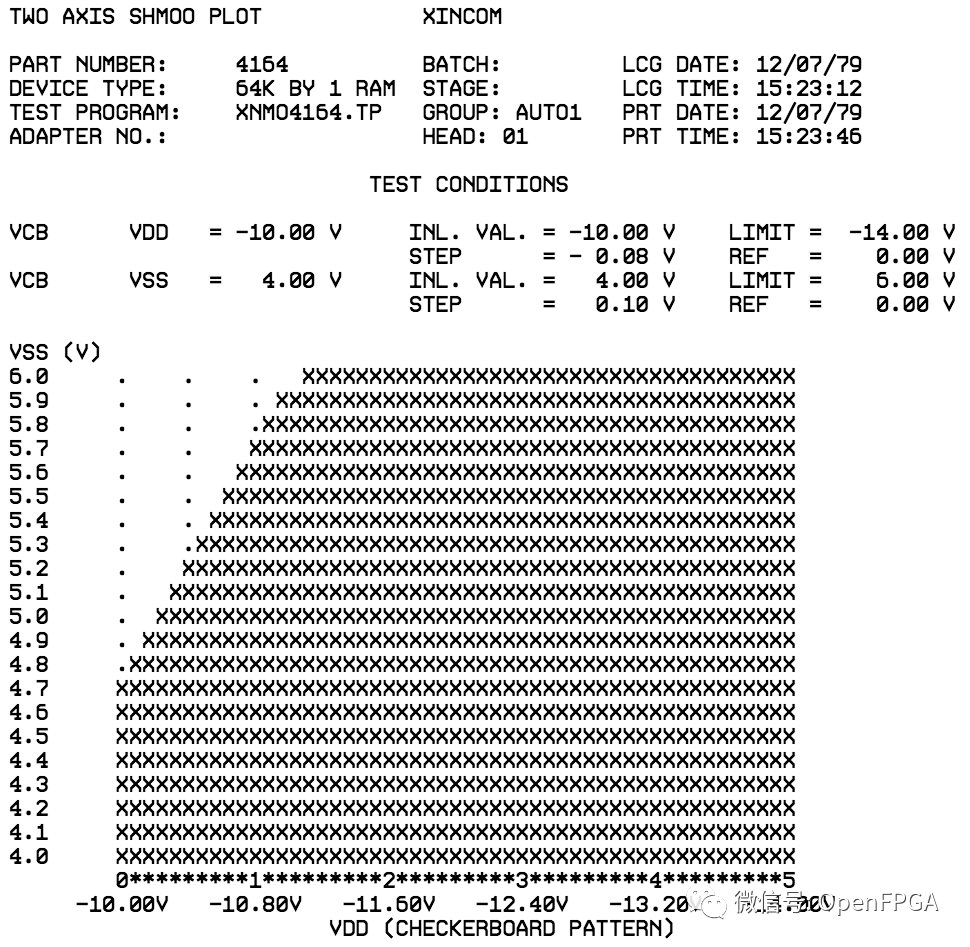

Shmoo Plot: An ASCII plot of a component response over a range of conditions. Shmoo 图:在一系列条件下组件响应的 ASCII 图。

Spectrum Analyzer: Electronic instrument for measuring the power of the spectrum of an unknown signal. 频谱分析仪:用于测量未知信号频谱功率的电子仪器。

审核编辑 :李倩

-

FPGA

+关注

关注

1631文章

21807浏览量

606729 -

IC

+关注

关注

36文章

5991浏览量

176424 -

adc

+关注

关注

99文章

6538浏览量

546047 -

模数转换器

+关注

关注

26文章

3222浏览量

127089

原文标题:FPGA/IC领域术语表

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DeepSeek在FPGA/IC领域的创新应用及未来展望

FPGA在图像处理领域的优势有哪些?

LED恒流IC领域的照明方案

FPGA在自动驾驶领域有哪些优势?

FPGA在自动驾驶领域有哪些应用?

HarmonyOS NEXT Developer Beta1最新术语表

源表的定义、原理和应用领域

FPGA 完整形式

fpga封装技术有哪些应用领域

fpga和数字ic区别 fpga和plc区别

适用于ARM Cortex®—A53处理器和 FPGA的集成电源管理IC TPS65220数据表

FPGA/IC领域术语表

FPGA/IC领域术语表

评论