2022年4月刊致辞

“ 在过去的一个月里,虽然疫情肆虐,但挡不住我们的技术团队依然在通过线上的方式为用户带来各种最新的解决方案,领域涉及了3DIC先进封装和高速测试等。我们的后勤保障团队,在物资极度紧缺、物流几乎停滞的情况下,也想尽办法,给每位上海员工家庭都送上了急需的物资包。春暖花开,我们期待疫情尽快过去,期待和您再次相聚。”

芯和半导体创始人、高级副总裁

代文亮博士

新闻亮点

ESD(Electronic System Design)电子系统设计联盟近日宣布,芯和半导体正式成为该联盟的成员。ESD联盟是SEMI旗下的一个代表电子系统和半导体设计生态系统成员的技术社区,是一个解决影响整个行业的技术、市场、经济和法律问题的社区,是沟通和提升半导体设计生态系统作为全球电子行业重要组成部分的价值的中心。除了 ESD 联盟的成员,芯和半导体同时也是 SEMI 的成员。SEMI 是代表了全球电子产品设计和制造供应链的全球性行业协会。

市场活动

如何从设计阶段就考虑串扰的规避,将会是每位SI工程师都需要直面的问题;高效、充分的产品验证是产品快速上市的一个保证。如何进行有效的产品开发阶段的串扰验证则是产品开发工程师需要思考的问题。芯和半导体的技术专家郑拓受邀于3月25日参加安立通讯科技的第11期高速接口测试论坛线上讲座,就高速数字产品设计与开发中串扰仿真和验证进行分享和交流。

3DIC第一讲:后摩尔时代异构集成的设计挑战及EDA的新使命

芯和半导体联合新思科技在全球首发了“3DIC先进封装设计分析全流程”EDA平台,是目前国内唯一布局了3DIC先进封装的本土EDA公司。芯和半导体技术支持总监苏周祥在本节课程中为我们全面分析3DIC先进封装最新的发展趋势,以及EDA如何迎接这其中的各项设计挑战。

应用案例

如何实现 “无阻抗校准的TOD去嵌”?

随着数据传输速率的不断提升,无源互连通道所承载的传输速率已经超过 67Gbps 甚至更高。为了能够准确预估无源通道的真实特性,需要具备更高带宽的测量仪器。然而,在现实的高速测量过程中,工程师难免都会遇到去嵌的问题:即待测器件无法与仪器直接相连,必须在两者之间插入转换夹具才能够实现测量,此时的测量结果同时包含了待测器件和夹具的效应,而在最终的结果中需要把夹具效应去除。

芯和半导体的SnpExpert针对不同应用场景提供了两种去嵌方法,包括Open-Short/Thru和 Thru-Only De-embedding(TOD)。本文着重介绍如何在不进行阻抗校准的情况下进行TOD去嵌,并通过实际案例,详细演示去嵌流程与结果。

高速接口利用T-coil的带宽提升解决方案

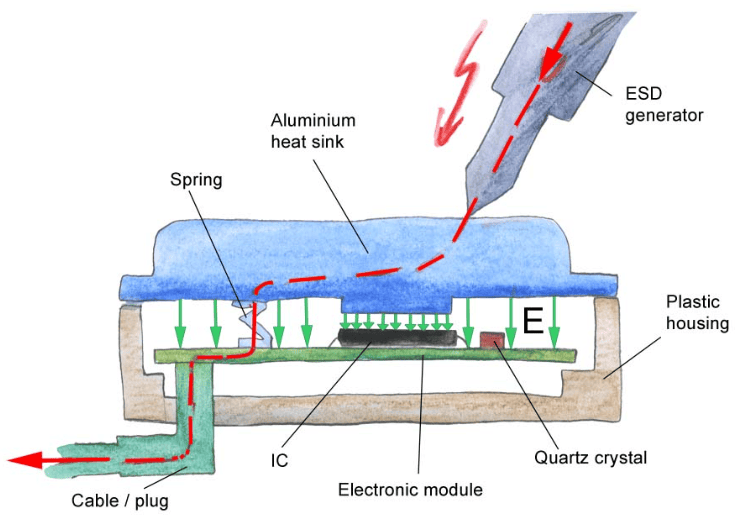

随着集成电路尺寸的缩小,以及集成电路工作速率的不断攀升,数据通信网络、微处理器、存储等产品的高速IO接口已经达到几十甚至上百GHz并对静电防护(ESD)越来越严格。然而,较大的ESD防护网络拥有高量级的电容,这对于接口带宽非常不利。是否能通过一种有效的方案,在不减少ESD电容的情况下,有效提升高速接口的带宽呢?

设计诀窍视频

如何在Hermes PSI中进行电源完整性分析

本次视频将为各位带来:如何使用芯和Hermes PSI工具,对电源网络的直流压降进行建模和仿真流程。

我们将以“一块PCB设计板”为例,为您一步步展示:

如何导入PCB版图文件至Hermes PSI中;

配置VRM和SINK;

检查DC结果电压分布图,电流密度图和功率密度图。

原文标题:员工抗疫物资已到——芯和半导体电子杂志4月刊

文章出处:【微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

ESD

+关注

关注

49文章

2040浏览量

173106 -

电子系统

+关注

关注

0文章

419浏览量

31191 -

芯和半导体

+关注

关注

0文章

108浏览量

31443

原文标题:员工抗疫物资已到——芯和半导体电子杂志4月刊

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成电路电磁兼容性及应对措施相关分析(一) 电子系统性能要求与ESD问题

集成电路电磁兼容性及应对措施相关分析(一) — 电子系统性能要求与ESD问题

虚拟设计与优化电力电子系统依赖于半导体芯片模型

第二季度电子系统设计行业增长18.2%

西门子EDA发布下一代电子系统设计平台

使用泰克示波器精确诊断并优化汽车电子系统

24芯M16插座在汽车电子系统中的关键作用

宏微科技将参加2024德国纽伦堡电力电子系统及元器件展览会

瑞萨收购Altium,以推动电子系统设计与创新

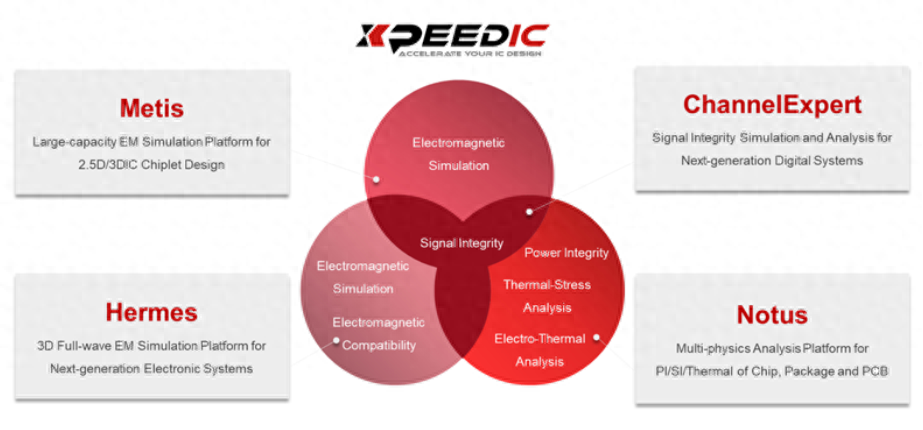

芯和半导体在DesignCon2024大会上发布针对下一代电子系统的SI/PI/多物理场分析EDA解决方案

DesignCon2024 | 芯和半导体发布针对下一代电子系统的“SI/PI/多物理场分析”EDA解决方案

ESD电子系统设计联盟宣布芯和半导体加盟

ESD电子系统设计联盟宣布芯和半导体加盟

评论