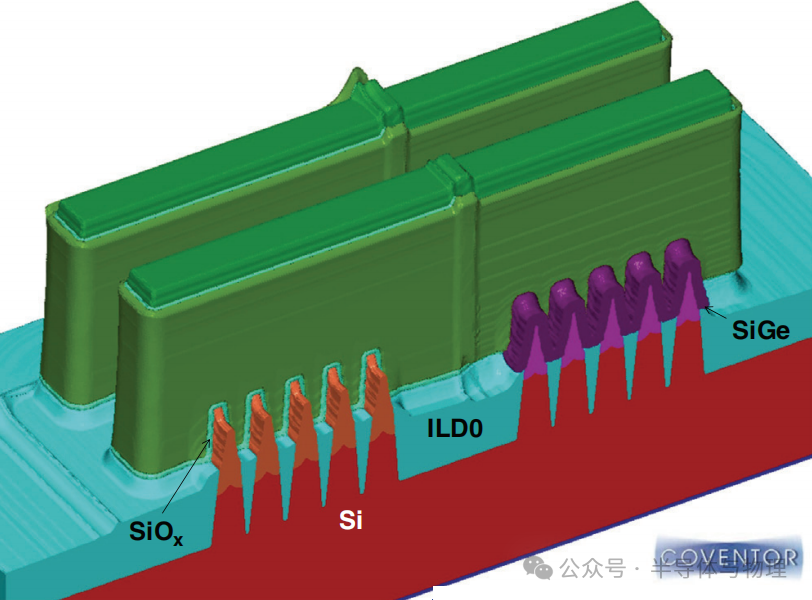

世芯电子完整体现了其在先进FinFET(先进鳍式场效电晶体)的技术组合并且成功完成在台积电7/6/5纳米的流片。除了先进 FinFET的技术组合,世芯的ASIC整体设计解决方案更是涵盖了全方位一流的IP种类和先进封装技术。世芯在7/6/5纳米的ASIC设计上能特别专注于具有数十亿逻辑门数的超大规模/尺寸IC设计。这些先进的IC主要用于人工智能、高性能计算、网络及存储应用等领域。

拥有一套经过自身验证的芯片设计流程和法则,是世芯成功的关键。它不仅能优化功耗、性能和面积的设计,同时还能符合客户严格的流片计划要求。世芯完整的7/6/5纳米设计能力包括大规模芯片设计里必要的分区和签核、测试设计流程,以及一套涵盖了全面系统协同设计签核的中介层/基板设计的完整2.5D封装设计流程。

世芯的创新封装服务也涵盖信号/电源仿真及热仿真(SI/PI),能提供即插即用的流片后解决方案,以减少基板层和由此产生的材料成本。这样产生的7/6/5纳米IC具有更精确的功率和热估算流程,能避免流片后的失败,在高功率设计中尤其关键。

世芯完整的5纳米“设计到交付”方法侧重于最大限度地缩短设计周期。其中的实体设计像是芯粒(Chiplet)技术平台、高性能计算IP组合含世芯的D2D APLink IP、IP子系统集成服务,以及最新的2.5D异构封装技术等。

“世芯的优势一直是先进工艺芯片设计。在7纳米系统芯片项目的设计流片量产上,我们与客户再次合作并取得了100%的流片成功率。”世芯总裁兼首席执行官沈翔霖表示,“我们的设计和验证法则乃经过严格认证,亦源于我们企业文化一贯秉持的核心服务理念”。

审核编辑 :李倩

-

芯片设计

+关注

关注

15文章

1041浏览量

55207 -

封装技术

+关注

关注

12文章

562浏览量

68146 -

FinFET

+关注

关注

12文章

253浏览量

90557

原文标题:先进FinFET工艺的多项流片巩固了世芯电子的业界领先地位

文章出处:【微信号:gh_81c202debbd4,微信公众号:世芯电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

先进FinFET工艺的多项流片巩固了世芯电子的业界领先地位

先进FinFET工艺的多项流片巩固了世芯电子的业界领先地位

评论