我们已经讨论了制造商购买正确的模数转换器 (ADC) 的想法,分辨率是决定的重要组成部分。大多数应用程序不需要 32 位精度;但高清音频、测试仪器和数字缩放等应用程序可以。想知道 32 位 ADC 的那些位是做什么的吗?下面简要概述了制造商需要了解的有关使这些部件在系统中按预期工作的知识。

首先,让我们看看精密 ADC 的内部结构。闪存和流水线 ADC 架构专注于速度,但在大约 16 位分辨率时会遇到限制。逐次逼近寄存器 (SAR) 以速度换取更好的分辨率。SAR 的工作原理是收敛 DAC,直到 A/D 输入电平匹配。SAR ADC 通常扩展到 24 位,少数推到 32 位,但它们往往会消耗功率。

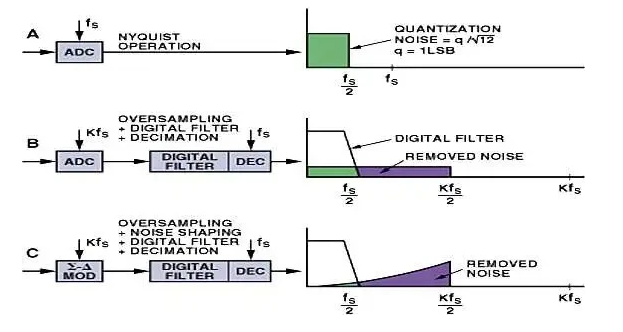

其他一些架构特性带有 delta-sigma 部分。在转换之前注意增益阶段,以增加动态范围并保持低噪声。此外,样本之间的信号变化量必须保持较小。最小化增量的首选方法是大规模过采样,比奈奎斯特速率高数百甚至数千倍。过滤和抽取使读数恢复到所需的采样率,但会增加较大的延迟。通常,减去过采样延迟的辅助转换通道会提供较低的分辨率,例如 22 位或 24 位。先进的噪声整形技术可以进一步降低本底噪声。

以下是过采样和噪声整形在数据转换中的工作原理。

即使在美好的一天,它也不是真正的 32 位

毫不奇怪,即使数据表说 32 位,这并不是一个得到多少位。平心而论,在大多数从 16 位及更高分辨率开始的转换器中,动态范围和噪声损失了几位是一种现象。对于 32 位转换器,理论动态范围约为 194 dB。没有物理传感器或模拟前端能提供这么多;实际设备以大约 130 dB 结束。噪音排在首位。正如之前的博客中所讨论的,高斯噪声可以通过过采样和平均来消除,这通常内置在 32 位 delta-sigma 部分中。

翻阅一些数据表可以看出,最先进的 32 位 delta-sigma ADC 可以以个位数的采样率提供多达 27 位,并带有大量的过采样和滤波。随着采样率的增加,有效位会下降一些,这可能是系统设计中的一个重要考虑因素。尽管如此,32 位部件可能比 24 位 ADC 在类似噪声条件下可以提供的有效分辨率有所改进。

真正的问题是,随着 ADC 的分辨率提高,最终用户的感知体验是否会更好。为了使更多位有用,必须端到端保留分辨率和动态范围。例如,以 32 位数字化音频并以低于该值的速度播放它就无法理解这一点。Rick Rubin 为贫血的 MP3 播放器和耳塞压缩录音范围而发了财。只有发烧友才注意到声音的差异。

然而,32 位随之而来

我将在 MP3 格式上另辟蹊径。假设一个人可以负担得起 32 位 ADC,并且更有效的分辨率适合应用中的体验。采样后有 32 位进行数字处理。带有 Arm 或 RISC-V 内核的快速 32 位微控制器现在很常见,这是一件好事。

对于在 32 位数据上运行的任何算法,例如相关或估计滤波器,整数数学成为一个问题。定点溢出和削波会破坏有效分辨率并增加数字失真。浮点是要走的路,许多 32 位 MCU 都具有硬件浮点能力。不过要小心;具有 23 位尾数的单精度浮点可能仍会裁剪结果。双精度 64 位浮点解决了这个问题。结合硬件中的 64 位内存提取和 C 或 Python 中的高级数学库支持,即使是复杂的算法也可以快速运行。

许多 32 位 delta-sigma 转换器可以运行到音频采样率范围。因为 delta-sigma 部件具有模拟内存和大延迟,所以以更快的采样率多路复用输入会变得混乱。32 位 delta-sigma 部件的最佳应用场景可能是非常低的采样率和激进的过采样。还有一个论点是不是薄弱环节——数字化更多位可能有助于算法将许多样本混合成更精确的结果。从 32 位 ADC 获取这些位的增量成本可能值得关注细节。

在通用动力公司从事导弹制导系统工作十年后,Don Dingee成为摩托罗拉 VMEbus 和单板计算机技术的传道者。他为 Planet Analog 撰写有关传感器、ADC/DAC 和信号处理的文章。

-

adc

+关注

关注

98文章

6509浏览量

544960 -

模数转换器

+关注

关注

26文章

3208浏览量

126871

发布评论请先 登录

相关推荐

基于高分辨率A/D转换器和DL技术实现时钟稳定电路的设计

AN-241:AD7710高分辨率(24位)∑-Delta A/D转换器评估板

32 位 A/D 转换器分辨率的真相

32 位 A/D 转换器分辨率的真相

评论