目录

近期打算写一些Cadence的使用总结,一来是可以加深自己对Cadence的熟悉程度,二来也可以替广大读者节约摸索时间。如有出入和需补充的地方,欢迎大家在评论区或私聊中指出。本期,作者拟介绍Cadence中Calculator的使用。我会在开头介Calculator的启动与界面,接着分别介绍Calculator的各个模块与使用方法。考虑到PDK版权问题,所有数值的结果均进行遮挡或者打码处理,请见谅。

1. Calculator的启动与界面

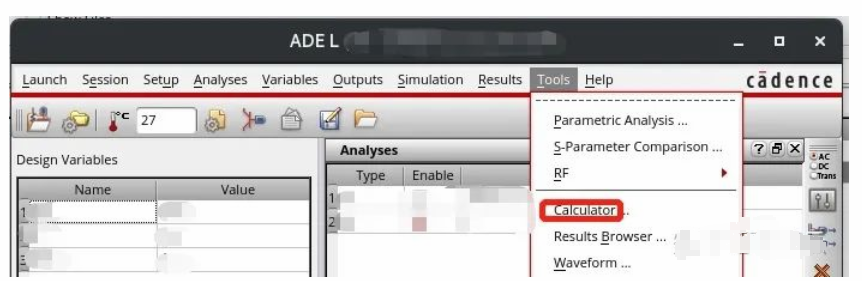

ADE L --> Tools --> Caculator

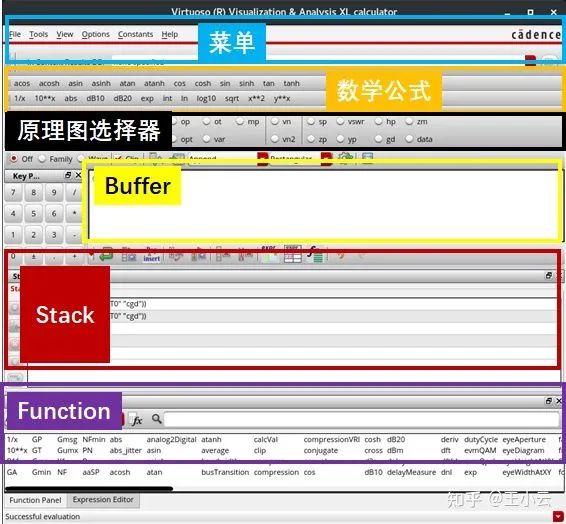

Calculator的界面由上至下分为以下几个板块,如图2所示。图2的界面可能与大家的界面不完全相同,这是因为我在View里面修改了设置。

“数学公式”比较简单,在此我就不做过多介绍了。下面,我会对其他版块进行逐一的介绍。

2. Buffer与Stack

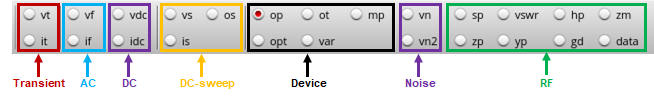

Buffer和Stack是最为常用的板块之一,它们存储了你“输入数据”和“表达式”。下面以“晶体管T21的直流工作点ids”为例讲解功能,如图3所示。

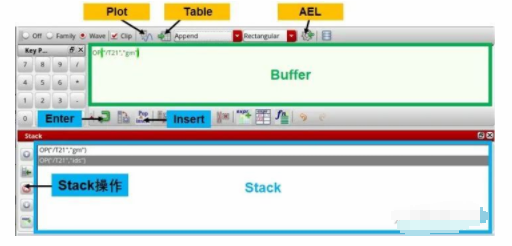

2.1 绘制曲线

点击图3所示“Plot”按钮,即可绘制“ids”曲线。

2.2 生成Table

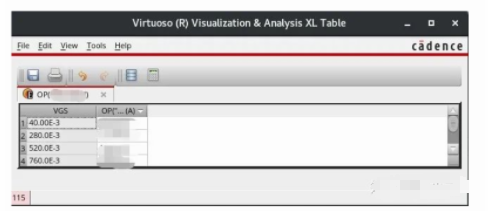

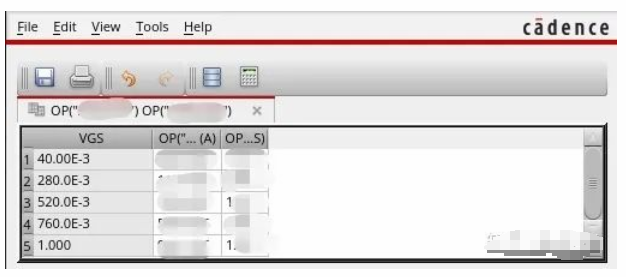

点击图3所示的“Table”按钮,可生成如图4所示的Table。第一列是参数扫描的变量“VGS”,第二列是晶体管T21的“ids”。

2.3 导出Table

在图4界面,File --> export (可以选择.csv)

之后可通过Matlab,Origin等软件进行处理或者绘图

2.4 生成多栏Table

保持图4中的Table打开

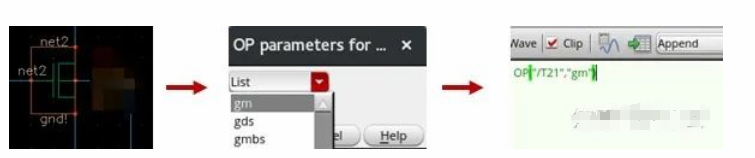

回到图3,在Buffer中输入晶体管T21的跨导表达式。

OP("/T21","gm")

接着点击图3中的“Table”按钮,即可生成如图5所示的多栏Table。新增加的第三列就是晶体管“T21”的跨导。

备注:“Table”按钮右侧选择“Append”才会添加新列,如果是“Replace”则是进行替换。

2.5 表达式送入AEL

点击图3所示的“AEL”按钮,可将“Buffer”中的表达式送入AEL。

2.6 Buffer与Stack交互

点击图3中的“Enter”按钮,可将“Buffer”中的表达式送入“Stack”。

点击图3中的“Insert”按钮,可将“Stack”中的表达式送入“Buffer”。

2.7 Stack内部操作

点击图3中“Stack操作”,我们可以对“Stack”内部存储的表达式进行“添加”,“删除”,和“顺序”调整。

3. 原理图选择器

我们可以通过如图6所示的“原理图选择器”在原理图中选择我们感兴趣的“元件”,“电压”和“电流”并将表达式送入“Buffer”。

我们以晶体管直流工作点“op”为例。点击op --> 自动跳转原理图 -->选择T21晶体管 --> 自动弹出List --> 选择gm --> 表达式进入“Buffer”,如图7所示。

4. 菜单

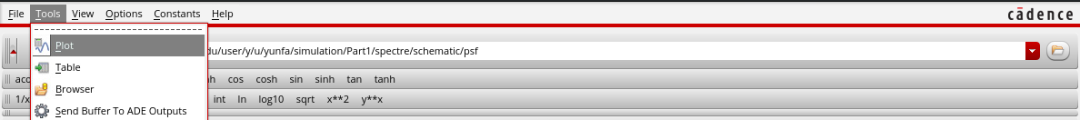

4.1 Tools

如图8所示为“Tools”的功能。我已在第二节中进行了详细介绍。

图8. Tools

图8. Tools

4.2 Views

可以选择是否显“数学公式”,“Stack”,“原理图选择器”等板块。

5 Function

Function的功能十分强大,可以对几乎所有的电路参数进行计算,可以显著提升设计效率。

5.1 常用函数

bandwidth(带宽):放大器设计常用

groupdelay(群时延):系统设计常用

NF(噪声系数):低噪放设计常用

Phasenoise(相位噪声):振荡器设计常用

还有摆率,功率谱密度,jitter等等常用函数都可以找到,使用非常简单。下面我以其中比较复杂的“上升延迟”举例。

5.2 举例“上升延迟”

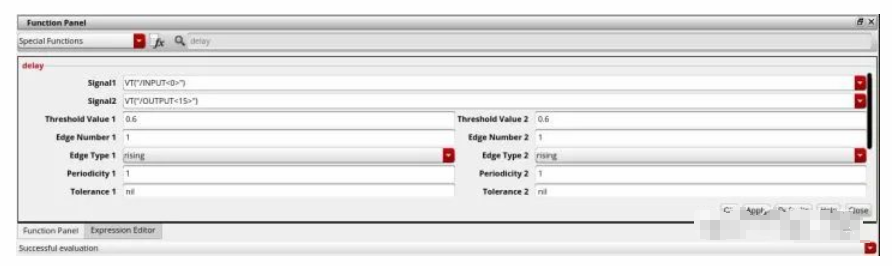

(1)如图9所示,在“Function”中搜索“delay”并选中

(2)在Signal1和2中分别填入我们所关注的信号

(3)VDD=1.2V,因此我们这里的临界电压设置为 0.6 0.6

(4)我们关注的是输入上升沿到输出上升沿的延迟,所以选择“rising”,“rising”。

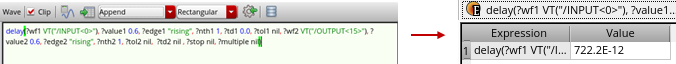

(5)点击“Apply”,在Buffer中出现如图表达式,并用Table导出为722.2 ps。

为了论证该结果的正确性,作者用Marker手动获得了上升延迟。将图10的结果与公式对比,容易证明是一致的。

-

Cadence

+关注

关注

68文章

1039浏览量

147472 -

Calculator

+关注

关注

0文章

6浏览量

7022

原文标题:仿真软件:Cadence中的Calculator使用总结

文章出处:【微信号:yaliDV,微信公众号:模拟混合信号设计验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Cadence携手TSMC加速新一代AI芯片设计

Cadence 与 Google 合作,利用 ChipStack AI Super Agent 在 Google Cloud 上扩展 AI 驱动的芯片设计

Cadence与Google合作,利用ChipStack AI Super Agent在Google Cloud上扩展AI驱动的芯片设计

Cadence Conformal AI Studio三大核心引擎重塑IC验证

Cadence Conformal AI Studio荣获2025亚洲金选奖年度最佳EDA奖

利用Cadence Fidelity CFD软件解决涡轮机械中的二次流效应

Cadence荣膺2025全球电子成就奖之年度EDA/IP/软件产品奖

今日看点:Cadence宣布收购ChipStack;德州仪器启用马六甲第二组装测试工厂

2025 Cadence 中国技术巡回研讨会即将开启 ——系统设计与分析专场研讨会(上海站)

Cadence中Calculator的使用

Cadence中Calculator的使用

评论