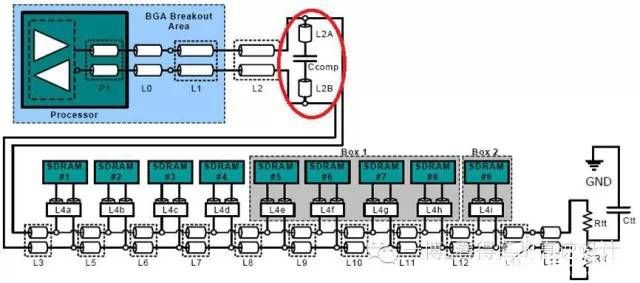

差分电容?没看错吧,有这种电容吗?当然是没有的,只是这个电容并联在差分信号P/N中间,所以我们习惯性的叫它差分电容罢了。如下图一中红色框中所示即我们今天的主角,下面容我慢慢给大家介绍。

图一

大家看到它是否有种似曾相识又不曾见过的感觉?确实,它只不过是一个普普通通的不起眼的电容罢了!但是,如果它真的只是一个普通的电容,高速先生也不屑拿出来和大家讲了,其实它普通的表面隐藏着很深的道道。到底有什么呢?嘘!一般人我不告诉他!

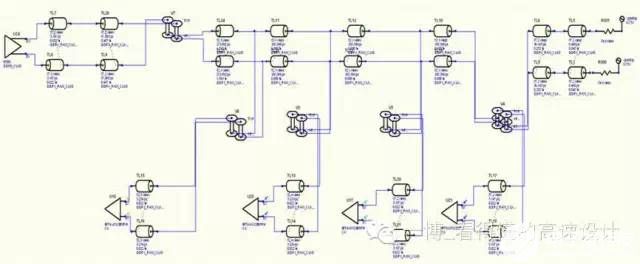

图一是Intel平台设计指导上经常可以看到的DDR3时钟拓扑结构,我们也经常会在仿真实践中去人为的添加这个差分电容,如下图二时钟信号一拖四所示为我们在设计中看到的一个真实案例。

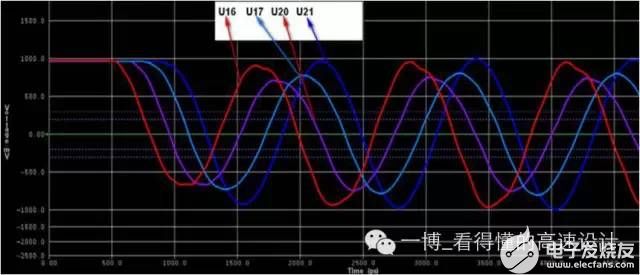

图二 无差分电容的时钟信号拓扑及波形

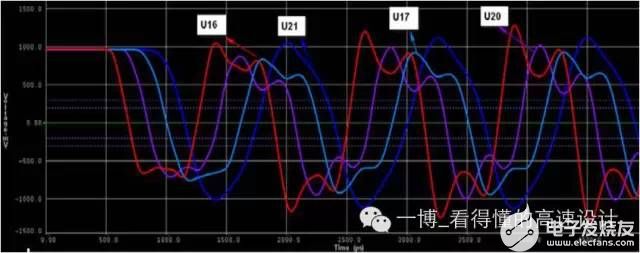

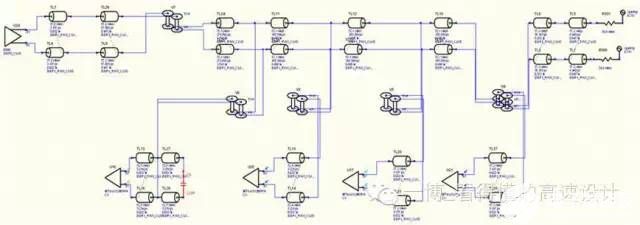

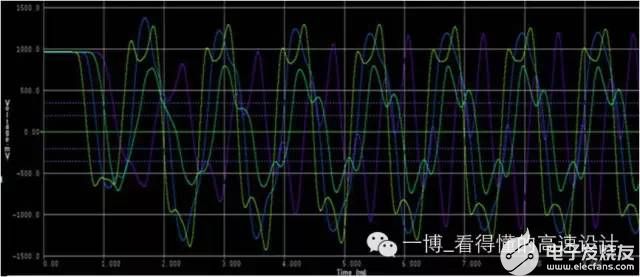

虽然看起来这个波形还凑合,没有太大的问题,但还是有优化的余地(工程师的强迫症又来了,真是伤不起啊!),可以通过在前端并联一个电容来优化,如下图三所示为并联了2.2pF差分电容后的拓扑结构和仿真波形。

图三 有差分电容的拓扑结构和波形

在前端加了差分电容后,虽然上升沿有微小的变缓,但波形真的是呈现了一个完美的正弦波曲线,振荡消除了,实在是苦逼的工程师们居家(埋头实验室)旅行(客户现场出差)、杀人灭口(消除反射等)之必备良方。此优化设计也已经投入使用,在加了这个电容后系统能稳定运行在800MHz的频率,如果没有焊接这个电容,系统只能稳定运行在667MHz,运行到800MHz时系统时有错误发生。

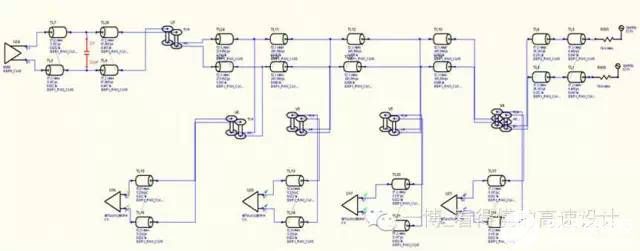

看到这里,一些脑洞大开的工程师可能会问,这个电容的位置有什么讲究吗?我可不可以把这个电容放在最后面那个颗粒?高速先生就喜欢有人提这种高质量的问题。下面还是看看仿真结果吧。

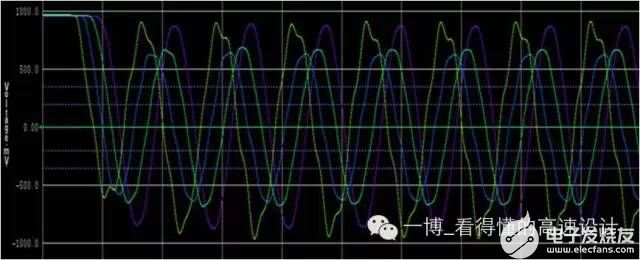

首先看看将电容放在第一个颗粒处的仿真结果,如下图四所示。

图四、电容在第一个颗粒处的拓扑和波形

可以看出此时波形已经没有放在前端(靠近发送芯片端)时的完美了,甚至出现了振荡的小苗头。接着把电容放在最后一片颗粒处,仿真结果如下图五所示。

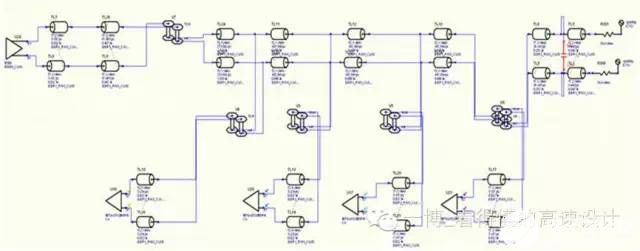

图五 电容在最后处的拓扑和波形

此时波形振荡甚至比没有电容的效果还明显,仿真结果表明此电容还是不要放在末端为好,最好的位置还是靠近发送端吧。

-

DDR3

+关注

关注

2文章

276浏览量

42242 -

差分电容

+关注

关注

0文章

6浏览量

8748 -

时钟信号

+关注

关注

4文章

448浏览量

28542

发布评论请先 登录

相关推荐

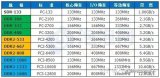

DDR3、DDR4、DDR5的性能对比

如何选择DDR内存条 DDR3与DDR4内存区别

基于FPGA的DDR3多端口读写存储管理设计

三星和SK海力士下半年停产DDR3内存

华邦倾力挺进DDR3市场,抓住转单商机

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

DDR3系列之时钟信号的差分电容

DDR3系列之时钟信号的差分电容

评论