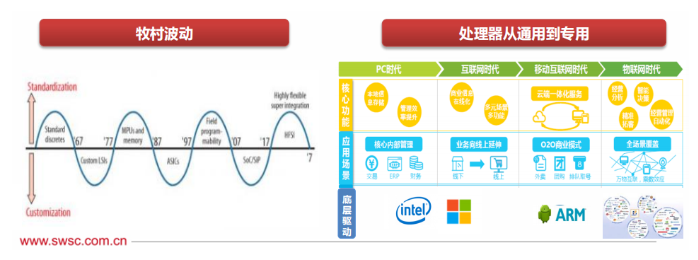

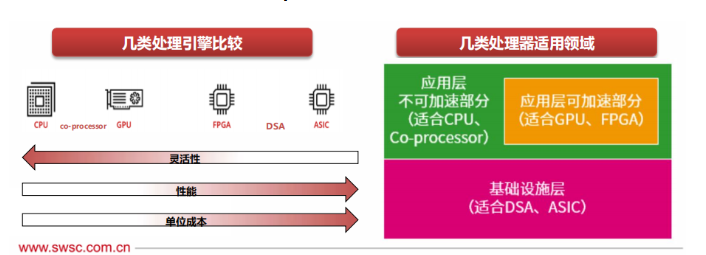

1)从通用到专用:面向不同的场景特点定制芯片,XPU、FPGA、DSA、ASIC应运而生。

2)从底层到顶层:软件、算法、硬件架构。架构的优化能够极大程度提升处理器性能,例如AMD Zen3将分离的两块16MB L3 Cache合并成一块32MB L3 Cache,再叠加改进的分支预测、更宽的浮点unit等,便使其单核心性能较Zen2提升19%。

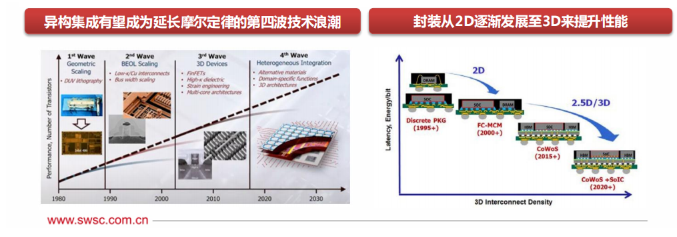

3)异构与集成:苹果M1 Ultra芯片的推出带来启迪,利用逐步成熟的3D封装、片间互联等技术,使多芯片有效集成,似乎是延续摩尔定律的最佳实现路径。

主流芯片厂商已开始全面布局:Intel已拥有CPU、FPGA、IPU产品线,正加大投入GPU产品线,推出最新的Falcon Shores架构,打磨异构封装技术;NvDIA则接连发布多芯片模组(MCM,Multi-Chip Module)Grace系列产品,预计即将投入量产;AMD则于近日完成对塞灵思的收购,预计未来走向CPU+FPGA的异构整合。

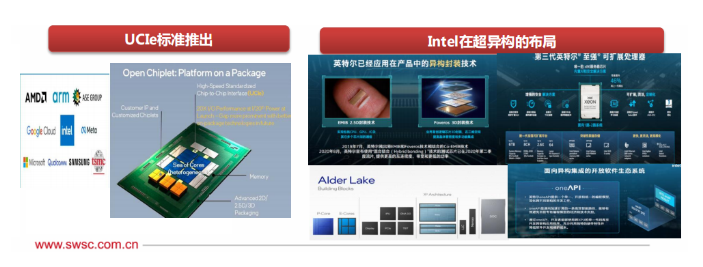

此外,英特尔、AMD、Arm、高通、台积电、三星、日月光、Google云、Meta、微软等十大行业主要参与者联合成立了Chiplet标准联盟,正式推出通用Chiplet的高速互联标准“Universal Chiplet InterconnectExpress”(通用小芯片互连,简称“UCIe”)。

在UCIe的框架下,互联接口标准得到统一。各类不同工艺、不同功能的Chiplet芯片,有望通过2D、2.5D、3D等各种封装方式整合在一起,多种形态的处理引擎共同组成超大规模的复杂芯片系统,具有高带宽、低延迟、经济节能的优点。

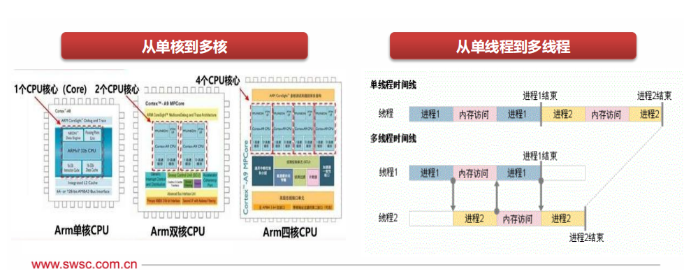

以多核提升性能功耗比:多核处理器把多个处理器核集成到同一个芯片之上,每个单元的计算性能密度得以大幅提升。同时,原有的外围部件可以被多个CPU系统共享,可带来更高的通信带宽和更短的通信时延,多核处理器在并行性方面具有天然的优势,通过动态调节电压/频率、负载优化分布等,可有效降低功耗,提升性能。

以多线程提升总体性能:通过复制处理器上的结构状态,让同一个处理器上的多个线程同步执行并共享处理器的执行资源,可以极小的硬件代价获得相当比例的总体性能和吞吐量提高。

微架构的改进

众多算数单元、逻辑单元、寄存器在三态总线和单项总线,以及各个控制线的连接下共同组成CPU微架构。不同的微架构设计,对CPU性能和效能的提升发挥着直观重要的作用。

微架构的升级,一般涉及到指令集拓展、硬件虚拟化、大内存、乱序执行等等一系列复杂的工作,还涉及到编译器、函数库等软件层次的修改,牵一发而动全身。

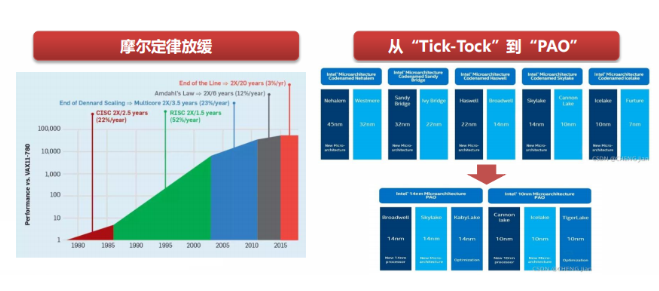

摩尔定律放缓

摩尔定律于上世纪60年代提出,直至2011年前,计算机元器件的小型化是提升处理性能的主要因素。2011年后,摩尔定律开始放缓,制硅工艺的改进将不再提供显著的性能提升。

“Tick-Tock”模式失效

自2007年开始,英特尔开始实施“Tick-Tock”发展模式,以两年为周期,在奇数年(Tick)推出新制成工艺,在偶数年(Tock)推出新架构的微处理器。

在14nm转10nm接连推迟后,英特尔自2016年起宣布停止 “Tick-Tock”处理器升级周期,改为处理器升级的三步战略:制程工艺(Process)-架构更新(Architecture)-优化(Optimization)。

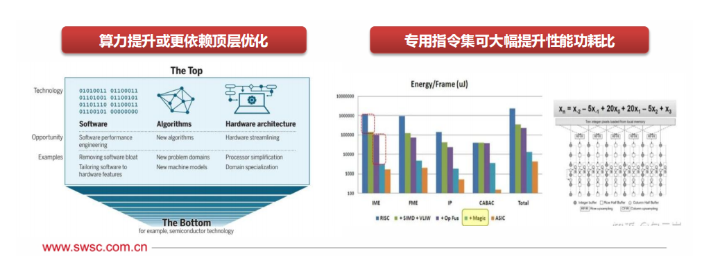

后摩尔时代,顶层优化或更为重要

新的底层优化路径被提出,例如3D堆叠、量子计算、光子学、超导电路、石墨烯芯片等,技术目前仍处于起步阶段,但后续有望突破现有想象空间。

根据MIT在《Science》发布的文章,后摩尔定律时代,算力提升将更大程度上来源于计算堆栈的「顶层」,即软件、算法和硬件架构。

通用指令集为了覆盖更多应用,往往需要支持上千条指令,导致流水线前端设计(取指、译 码、分支预测等变得十分复杂),对性能功耗会产生负面影响。

领域专用指令集可大大减少指令数量,并且能够增大操作粒度,融合访存优化,实现数量级提高性能功耗比。

新兴场景出现,CPU从通用向专用发展

1972年,戈登·贝尔(Gordon Bell)提出,每隔10年,会出现新一类计算机(新编程平台、 ,新网络连接、新用户接口,新使用方式且更廉价),形成新的产业。 1987 年, 原日立公司总工程师牧村次夫(Tsugio Makimoto) 提出,半导体产品未来可能将沿着“标准化”与“定制化”交替发展的路线前进,大约每十年波动一次。

经历了桌面PC、互联网时代和移动互联网时代后,“万物智联”已成为新的风向标,AIoT正掀起世界信息产业革命第三次浪潮。而AIoT最明显的特征是需求碎片化,现有的通用处理器设计方法难以有效应对定制化需求。

通用与性能,难以兼得

CPU是最通用的处理器引擎,指令最为基础,具有最好的灵活性。Coprocessor,是基于CPU的扩展指令集的运行引擎,如ARM的NEON、Intel的AVX、AMX扩展指令集和相应的协处理器。

GPU,本质上是很多小CPU核的并行,因此NP、Graphcore的IPU等都和GPU处于同一层次的处理器类型。

FPGA,从架构上来说,可以用来实现定制的ASIC引擎,但因为硬件可编程的能力,可以切换到其他ASIC引 擎,具有一定的弹性可编程能力。

DSA,是接近于ASIC的设计,但具有一定程度上的可编程。覆盖的领域和场景比ASIC要大,但依然存在太多的领域需要特定的DSA去覆盖。

ASIC,是完全不可编程的定制处理引擎,理论上最复杂的“指令”以及最高的性能效率。因为覆盖的场景非常小,因此需要数量众多的ASIC处理引擎,才能覆盖各类场景。

后摩尔定律时代,展望CPU未来发展之路

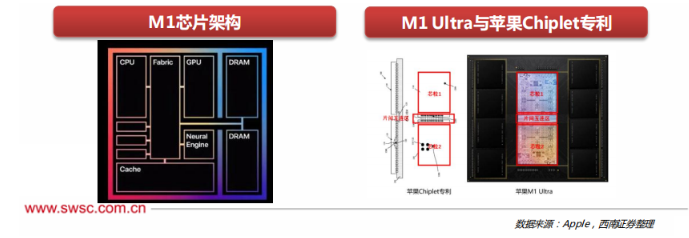

不可逆转的SoC集成:由于集成电路集成度不断提高,将完整计算机所有不同的功能块一次直接集成于一颗芯片上的 SoC 片上就成为整个半导体行业发展的一个趋势,可以显著降低系统成本和功耗,提高系统可靠性。M1 并不是传统意义上的 CPU,而是一颗SoC。CPU采用了8核心,包括4个高性能核心和4个高能效核心。每个高性能核心都提供出色的单线程任务处理性能,并在允许的范围内将能耗降至最低。

异构能力的大幅提升:M1还采用了统一内存架构(UMA),CPU、GPU、神经引擎、缓存、DRAM内存全部通过Fabric高速总线连接在一起,得益于此,SoC中的所有模块都可以访问相同的数据,而无需在多个内存池之间复制数据,带宽更高、延迟更低,大大提高了处理器的性能和电源效率。此外,最新一代的M1 Ultra本质上是两个M1 MAX的有效组合,通过UltraFusion架构,提供高达128G统一内存,相较M1的GPU性能提高8倍。

苹果M1处理器完成了一次从多芯片走向一体化的过程,这也是苹果打造完整PC生态链的必经之路,让我们看见了CPU未来发展的更多可能性。

后摩尔时代,异构与集成

海外芯片巨头积极布局异构计算:英特尔现已布局CPU、FPGA、IPU、GPU产品线,并接连公布Alder Lake、Falcon Shores等新架构;英伟达接连发布多芯片模组(MCM,Multi-ChipModule)Grace系列产品,预计即将投入量产;AMD则于近日完成对塞灵思的收购,预计未来走向CPU+FPGA的异构整合。

晶圆厂和封装厂亦积极投入异构集成:异构计算需要有先进的集成封装技术,得益于近十年来先进封装与芯片堆叠技术的发展,例如3D堆叠、SiP等,也使得异构集成成为了大幅存在可能。目前,2.5D封装技术已发展较为成熟,例如台积电的CoWoS,三星的I-Cube,3D封装成为各大晶圆厂发力方向。英特尔已开始量产Foveros技术,三星已完成X-Cube的验证,台积电亦提出了SoiC的整合方案。

CPU+XPU已广泛应用,但仍有优化空间。传统的异构计算架构存在IO路径较长,输入输出资源损耗等固有问题,并且仍然无法完全兼顾极致性能与灵活性。

Chiplet联盟组建,探索超异构可能性。2022年3月3日,英特尔、AMD、Arm、高通、台积电、三星、日月光、Google云、Meta、微软等十大行业巨头联合成立了Chiplet标准联盟,正式推出了通用Chiplet的高速互联标准“Universal Chiplet Interconnect Express”(通用小芯片互连,简称“UCIe”)。

在UCIe的框架下,互联接口标准得到统一。各类不同工艺、不同功能的Chiplet芯片,有望通过2D、2.5D、3D等各种封装方式整合在一起,多种形态的处理引擎共同组成超大规模的复杂芯片系统,具有高带宽、低延迟、经济节能的优点。

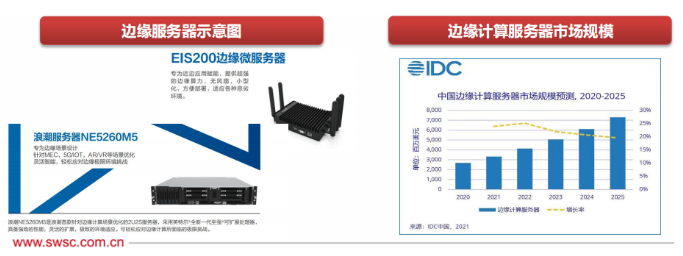

边缘计算服务器是解决AIoT时代“算力荒”的必备产物

云计算无法满足海量、实时的处理需求。伴随人工智能、5G、物联网等技术的逐渐成熟,算力需求从数据中心不断延伸至边缘,以产生更快的网络服务响应,满足行业在实时业务、应用智能、安全与隐私保护等方面的基本需求。

市场规模爆发式增长。根据IDC,中国边缘计算服务器整体市场规模达到33.1亿美元,较2020年增长23.9%,预计2020-2025年CAGR将达到22.2%,高于全球的20.2%。

定制服务器快速增加。当前通用服务器和边缘定制服务器占比分别为87.1%和12.9%,随着边缘应用场景的逐渐丰富,为适应复杂多样的部署环境和业务需求,对于具有特定外形尺寸、低能耗、更宽工作温度以及其他特定设计的边缘定制服务器的需求将快速增加。IDC预计边缘定制服务器将保持76.7%的复合增速,2025年渗透率将超过40%。

根据业务场景多样定制,集成化是趋势

区别于数据中心服务器,边缘服务器配置并不一味追求最高计算性能、最大存储、最大扩展卡数量等参数,而是在有限空间里面尽量提供配置灵活性。当前边缘服务器多用于工业制造等领域,需根据具体环境(高压、低温、极端天气)等选择主板、处理器等,下游需求呈现碎片化,未有统一的标准。

伴随越来越多的计算、存储需求被下放至边缘端,当前趋势通常涉及更紧密的加速集成,以满足包括AI算力在内的多种需求。超大规模云提供商正在开始研究分类体系结构,为了减少熟悉的多租户方法不可避免的碎片化,其中计算、存储、网络和内存成为一组可组合的结构,机柜式架构(RSA)分别部署了CPU、GPU、硬件加速、RAM、存储和网络容量。

云服务器正在全球范围内取代传统服务器

云服务器的发展使中国成为全球服务器大国。随着移动终端、云计算等新一代信息技术的发展和应用,企业和政府正陆续将业务从传统数据中心向云数据中心迁移。虽然目前中国云计算领域市场相比美国相对落后,但近年来我国的云计算发展速度显著高于全球云计算市场增长速度,预计未来仍将保持这一趋势。

面向不同需求,提供多样性算力。一般小型网站请求处理数据较少,多采用1、2核CPU;地方门户、小型行业网站,需要4核以上的CPU;而电商平台,影视类网站等,则需要16核以上的CPU。此外,云服务器亦提供灵活的扩容、升级等服务,一般均支持异构类算力的加载。

CPU+ASIC,云服务器异构趋势明显

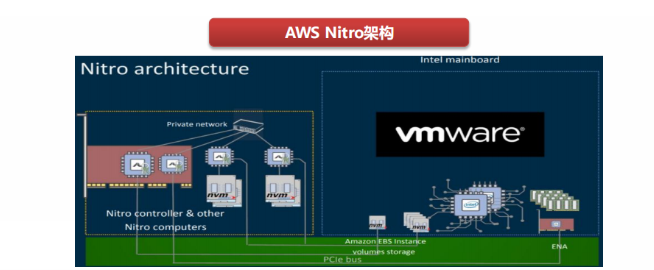

在传统的计算机虚拟化架构中,业务层为虚拟机,管理层为宿主机,业务和管理共存于CPU运行,导致CPU大概只有七成的资源能够提供给用户。

AWS创造性进行架构重构,将业务和管理分离到两个硬件实体中,业务运行在CPU,管理则运行在NITRO芯片中,既将虚拟化的损耗挪到定制的Nitro系统上,又提高了安全性。

Nitro架构不仅性能强大,而且特别灵活,可以基于一些常用的Hypervisor(如qemu-kvm,vmware)运行虚拟机,甚至可以直接裸跑操作系统,可节省30%CPU资源。

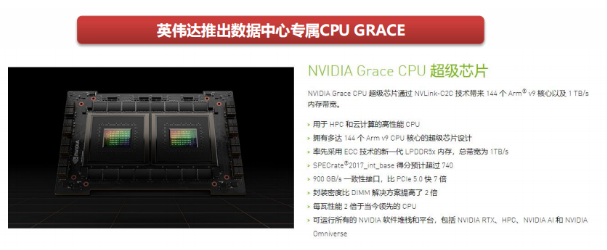

ARM或成重要挑战者,英伟达推出首款数据中心专属CPU GRACE

公有云巨头价格竞争激烈,国内一线城市能耗管控严格,ARM移动端的优势和低能耗特征是超大型数据中心解决节能和成本问题的重要方案之一;国内自主可控趋势背景下,若能够搭建强有力的生态联盟,是未来可能颠覆原有格局的最有力挑战者。

英伟达宣布推出首款面向AI基础设施和高性能计算的数据中心专属CPU——NvDIA Grace,由两个CPU芯片通过最新一代NVLink-C2C技术互联组成。

Grace基于最新的ARMv9架构,单个socket拥有144个CPU核心,利用纠错码(ECC)等机制提供当今领先服务器芯片两倍的内存带宽和能效,兼容性亦十分突出,可运行NvDIA所有的软件堆栈和平台,包括NvDIA RTX、HPC、Omniverse等。

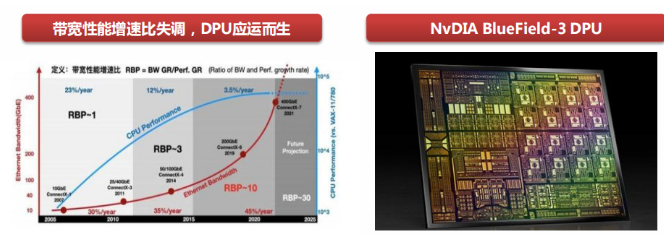

从CPU到CPU+DPU

DPU,即数据处理单元(Data Processing Unit),主要作为CPU的卸载引擎,主要处理网络数据和IO数据,并提供带宽压缩、安全加密、网络功能虚拟化等功能,以释放CPU的算力到上层应用。

2013年,AWS研发的的Nitro和阿里云研发的X-Dragon均可看作DPU前身;英伟达在2020年正式发布一款命名为“DPU”的产品,将其定义为CPU和GPU之后的第三颗主力芯片,DPU的出现是异构计算的另一个阶段性标志。

DPU是CPU和GPU的良好补充,据英伟达预测,每台服务器可能没有GPU,但必须有DPU,用于数据中心的DPU的量将达到和数据中心服务器等量的级别。

从CPU到CPU+XPU

AI模型通过数千亿的参数进行训练,增强包含数万亿字节的深度推荐系统,其复杂性和规模正呈现爆炸式增长。这些庞大的模型正在挑战当今系统的极限,仅凭CPU的优化难以满足其性能需求。

因此,AI服务器主要采用异构形式,表现形态多为机架式。在异构方式上,可以为CPU+GPU、CPU+FPGA、CPU+TPU、CPU+ASIC或CPU+多种加速卡。

现在市面上的AI服务器普遍采用CPU+GPU的形式,因为GPU与CPU不同,采用的是并行计算的模式,擅长梳理密集型的数据运算,如图形渲染、机器学习等。继续扩展模型以实现高度准确性和实用性,需要能够快速访问大型内存池并使 CPU 和 GPU 紧密耦合。

从CPU到CPU+TPU

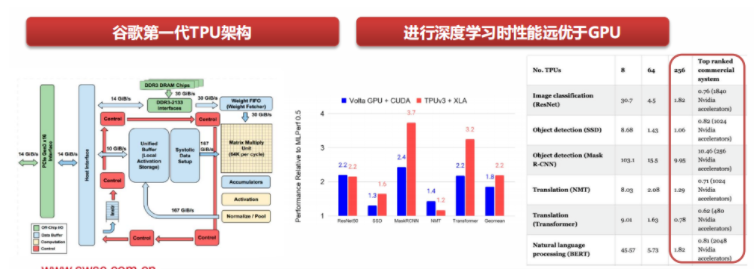

TPU,即张量处理单元(Tensor Processing Unit),是Google为加速深度学习所开发的专用集成电路(DSA),采用专用CISC指令集,自定义改良逻辑、线路、运算单元、内存系统架构、片上互联等,并针对Tensorflow等开源框架进行优化。

2015年起,谷歌发布TPUv1,应用于Alpha Go等特定内部项目;2018年,谷歌发布TPUv3,开始向第三方出售,TPU开始逐渐走向商用。

2021年,谷歌发布TPUv4i,其性能相较第三代TPU提升2.7倍;256块TPU仅用1.82分钟便完成NLP领域著名的“BERT”模型训练,而同样条件下,利用Nvdia A100 GPU则需要3.36分钟。

-

asic

+关注

关注

34文章

1199浏览量

120441 -

cpu

+关注

关注

68文章

10855浏览量

211594 -

AI

+关注

关注

87文章

30747浏览量

268900

发布评论请先 登录

相关推荐

后摩尔定律时代 未来CPU处理器技术发展趋势

后摩尔定律时代 未来CPU处理器技术发展趋势

评论