上篇我们介绍了相关的算法原理以及外设特性,本篇我们将介绍一下基于FPGA的实时图像边缘检测系统的实现方案,算法的Verilog实现以及最终实现的检测效果。

一、 设计方案

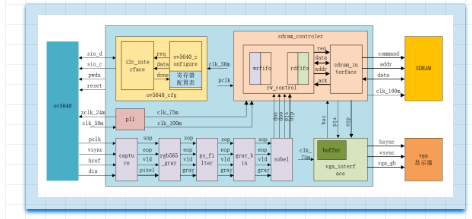

整个系统主要分为以下5个部分:摄像头传感器配置部分;图像数据采集与处理部分;图像缓存部分;VGA显示部分;以及PLL时钟管理部分;如图1所示。

图1 系统结构图

摄像头传感器配置部分

按照配置表中的参数,将摄像头配置为分辨率为1280*720像素点、RGB565数据格式、VGA时序输出;然后通过I2C协议将参数配置给摄像头的每个寄存器。

图像数据采集与处理部分

摄像头配置完成后,在摄像头输出时钟pclk驱动下,完成图像数据的采集与处理;图像采集模块(capture)对摄像头输出的像素数据进行串并转换,然后给到后续的图像处理模块,依次进行灰度转换(rgb565_gray)、高斯滤波(gs_filter)、二值化处理(gray_bin)、Sobel边缘检测(sobel);在进行二值化处理时,直接将灰度图像二值化为0或1。

图像缓存部分

主要是SDRAM读写控制逻辑(rw_control)与SDRAM接口(sdram_interface);其中,rw_control模块作为Master向sdram_interface发起突发传输请求。主要有以下几个功能:

跨时钟域数据缓存;

乒乓缓存控制;

SDRAM读写优先级的仲裁以产生读写传输请求、地址等。

sdram_interface模块作为Slave执行Master发起的突发传输请求,主要是根据接收到读、写请求以及数据、地址等,向SDRAM芯片发起各种命令、地址、数据,实现SDRAM的数据存取。

VGA显示部分

主要是实现1080*720@60分辨率的VGA显示时序,驱动VGA接口的显示器显示处理结果。

PLL时钟管理部分

主要是产生整个工程需要使用的几个时钟,100MHz的SDRAM控制器与SDRAM工作时钟、75MHz的VGA驱动时钟,24MHz的摄像头xclk时钟;图1中使用不同的颜色对不同的时钟域进行了标注。实际上,我们在设计SDRAM控制器时需要考虑存储器的带宽是否大于实际所需吞吐量。而存储器的带宽是由其工作时钟频率决定的,但由于刷新、激活、预充电的存在,SDRAM的实际存取速度比其工作时钟频率略小;实际所需吞吐量是指单位时间内向SDRAM写入的数据量与从SDRAM读出数据量之和。当存储器带宽小于实际所需吞吐量时,由于存取速度超过SDRAM的存取带宽会导致数据来不及写入或者读出,此时无论写数据缓冲器与读数据缓冲器的深度设置为多大,必然会导致写缓冲区上溢或者读缓冲区下溢。对于高速视频流缓存场景,这种问题会造成灾难性的问题。因此,在设计SDRAM控制器时需要根据数据存取速度合理设置SDRAM的工作时钟频率。

二、 主要模块分析

接下来我们对部分模块的Verilog代码实现方案进行简单介绍。

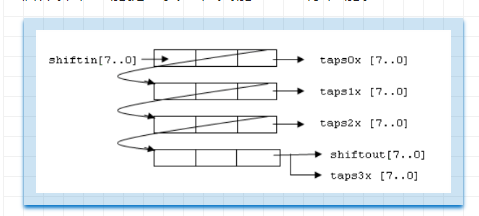

高斯滤波模块与sobel边缘检测模块都涉及到二维矩阵卷积,所以如何生成一个3*3的二维矩阵是我们需要考虑的。实际上,这里我们可以调用Quartus Prime软件自带的移位存储器(shift_ram)IP核,将其配置为3个tap,每个tap之间的间距为1280个数据,如下图所示。然后对每个tap输出的数据打两拍即可得到3*3的像素矩阵。然后使用流水线实现像素数据与模板权重的卷积计算,既能提高实时性又能保证时序性能。

图2 移位存储器结构示意图SDRAM控制器部分主要是对检测结果进行缓冲,由于我们使用的分辨率为1280*720,即使是二值(0、1)图像也需要两个大小为900Kbit的RAM存储器进行乒乓缓存,而我们使用的EP4CE6F17C8型号的FPGA片上RAM仅有270Kbit,远远不能满足需求;所以这里为了保证数据完整性,选用SDRAM来实现双缓冲。在实现乒乓缓存时,使用sop(帧起始)与eop(帧结束)来控制完整数据帧缓存或丢弃。

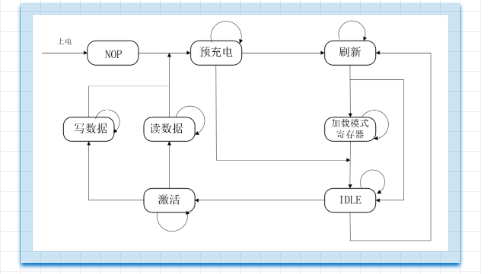

SDRAM接口模块主要是配置SDRAM芯片的工作模式、存取数据,为了保证SDRAM芯片以较高的吞吐量存取数据,这里将SDRAM配置成了连续突发模式、突发长度为512。由于SDRAM的指令较多,工作时序比较复杂,这里选择使用状态机来设计SDRAM接口时序,状态机设计如下图所示:

图3 SDRAM接口模块状态机转移图

三、 实现结果

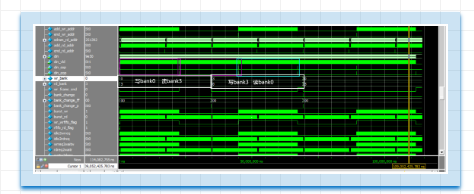

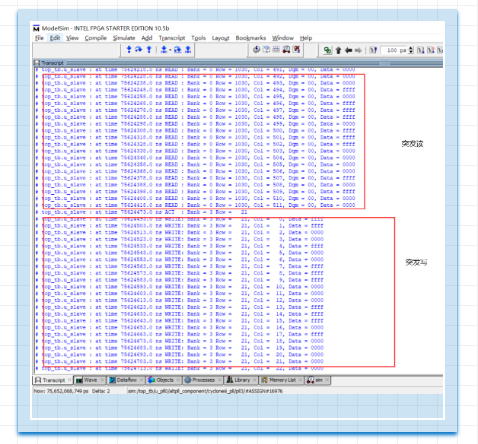

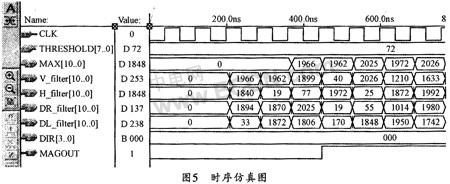

SDRAM乒乓缓存部分仿真结果如下图4所示;当向bank0写完第一帧数据之后,会丢弃下一帧数据,直到bank3中的一帧数据完整读完时才会切换读写bank,然后再缓存下一帧新的数据。从图5所示仿真结果可以看到,成功实现了对SDRAM两个Bank的交替存取,实现了乒乓缓存的效果。

图4 乒乓缓存仿真结果

图5 SDRAM存取仿真结果本设计最终实现结果如图6所示,能够实时的检测图像边缘,提取出目标的轮廓,达到预期效果。但是由于光线影响等方面的原因,导致最终实现出来的效果不是非常完美。

-

FPGA

+关注

关注

1664文章

22553浏览量

640503 -

检测系统

+关注

关注

3文章

1003浏览量

45598 -

图像边缘

+关注

关注

0文章

10浏览量

7492

发布评论请先 登录

基于FPGA实时图像边缘检测系统的实现

基于FPGA实时图像边缘检测系统的实现

评论