几年前,我在 Design Ideas 中写了一篇名为“ Double µC 的 PWM 频率和分辨率”的文章,其中我提到了如何使用两个具有相等占空比且相位为 180 度的 PWM 信号(一半一个周期延迟)彼此之间的差异。

PWM DAC 背后的想法非常简单:它滤除 PWM 信号的所有谐波成分,只留下其中的直流分量。为此,PWM 信号经过低通滤波。显然,当您使用具有较低截止频率的滤波器时,输出将更加“无纹波”,但瞬态响应将非常缓慢,反之亦然。

上述文章中提出的想法是生成一个反相信号,以通过相位抵消动作来抵消一些谐波分量,而不是仅仅依靠滤波器本身。

事实证明,这个想法在减少纹波方面很有用,同时也改善了瞬态响应。然而,它的用处是有限的,因为并非所有 PWM 信号的谐波分量都相互抵消。更具体地说,只有奇次谐波相互抵消,偶次谐波仅受滤波器影响,因为当我们引入半周期延迟时,只有奇次谐波经历 180 度相移,偶次谐波经历 360 度相移,即与同相相同。这导致偶次谐波不会相互抵消。

事实上,对于 50% 的占空比(它只包含奇次谐波),我们使用这种技术可以获得无纹波输出。对于任何其他占空比,都会有一些纹波,但与单通道等效物相比,纹波幅度仍然会有一些改进。我们可以通过使用更多具有不同相位差的 PWM 通道来扩展这个想法,以获得更多无纹波占空比点。

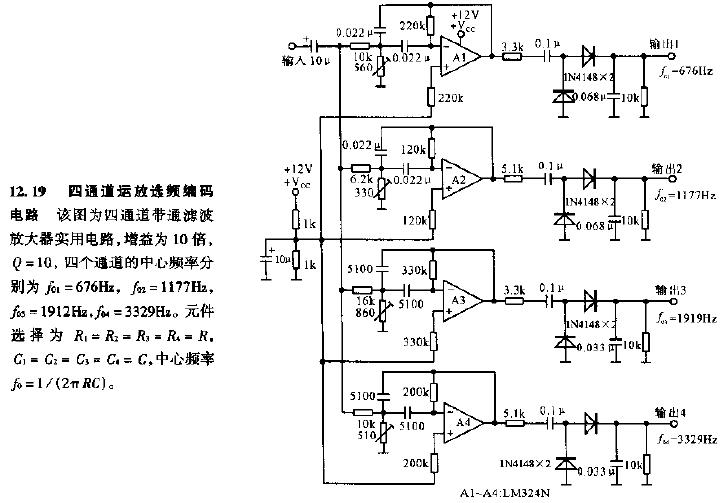

假设我们决定在 f Hz 处使用 n 个通道,如果每个连续的 PWM 通道相对于彼此具有 1/(fn) 延迟(或 360/n 相移),那么每个谐波分量都将被消除,因为间隔均匀除每 n 次谐波外的时间延迟。更清楚地说,假设我们使用 10 kHz 作为我们的主要 PWM 频率,并且我们实现了具有 25µs 时间延迟(90 度相移)的四个通道。在这种情况下,第一个通道是我们的基本通道,它没有延迟;第二个通道相对于基本通道有 25µs 延迟(90 度);第三个通道相对于基本通道有 50µs 延迟(180 度);最后一个通道相对于基本通道有 75µs 的延迟(270 度)。

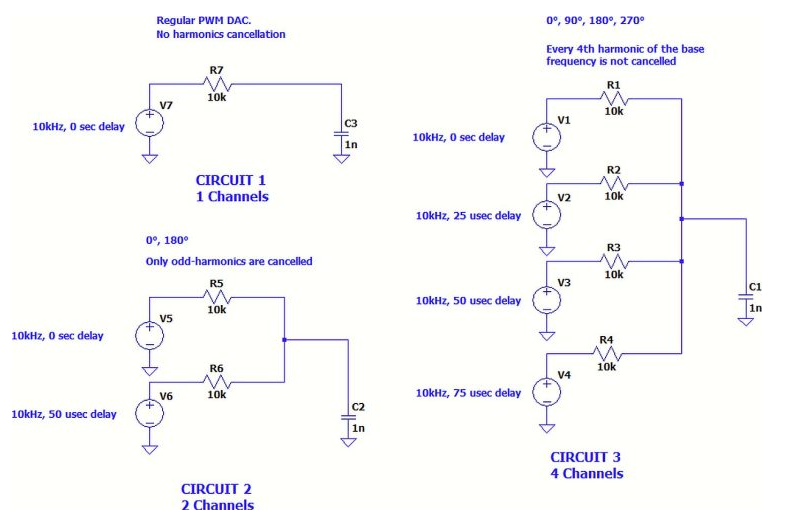

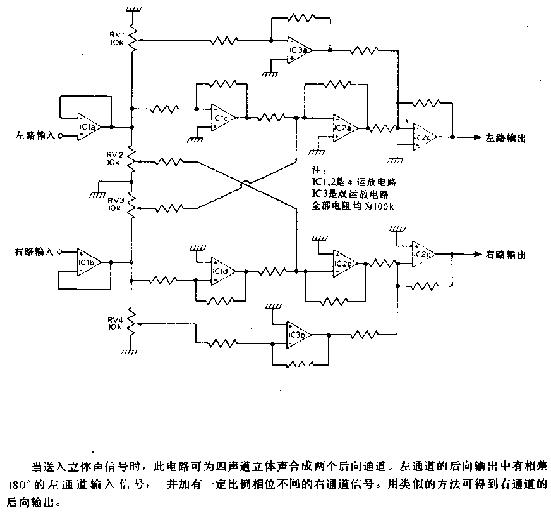

如前所述,每个连续通道相对于其“相邻”通道具有 25µs (1/(fn), f=10kHz, n=4) 延迟。图 1显示了该电路以及单通道和双通道版本。

图 1四通道相控阵 PWM DAC 电路以及一通道和两通道版本。

该四通道 PWM DAC 的输出将仅包含基本 PWM 频率的 4次谐波,因此当占空比为 25%、50% 或 75% 时,输出将不包含纹波,因为这些 PWM 信号没有 4次谐波含量。

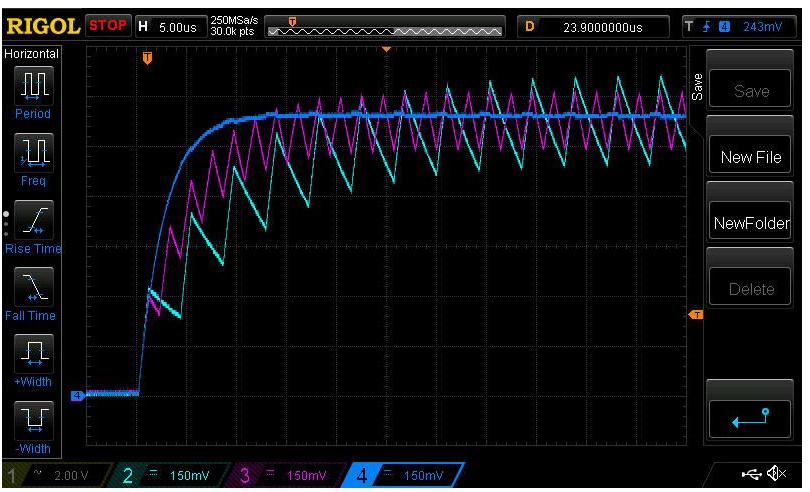

在图 2、3和4中,我们可以看到占空比分别为 25%、50% 和 75% 的每个电路的输出。

图 2占空比为 25% 的电路。

图 3占空比为 50% 的电路。

图 4占空比为 75% 的电路。

正如预期的那样,四通道电路(深蓝色)在25%占空比下输出几乎没有纹波,具有最快的瞬态响应;双通道电路(粉红色)有纹波,但纹波小于单通道(浅蓝色)电路输出,速度更快。在 50% 时,双通道电路(粉红色)和四通道电路(深蓝色)都没有任何纹波,但四通道电路具有更快的瞬态响应,显然单通道(浅蓝色)电路最慢和最吵。75% 的结果与 25% 的结果相同。

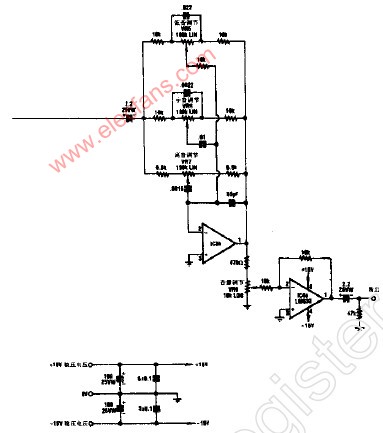

为了测试,电路是使用 FPGA 在 VHDL 中实现的(GitHub 链接在帖子末尾共享),因为通道很多,并且可以通过部署更多通道来进一步扩展这个想法。一般来说,如果实现了 n 个通道,将有 n-1 个无纹波占空比点(不包括 0% 和 100%,它们本身就是无纹波的)。从理论上讲,使用这种方法可以使用 256 个通道实现 8 位 DAC,但当然这将是非常不切实际的,但没有人能阻止您享受这个想法。

为了完整起见,该方法在 LTSpice 中最多模拟了 8 个通道(也在文章末尾的 GitHub 链接中)。出于同样的原因,对于一个八通道电路,您应该在 12.5% 占空比点的倍数处获得无纹波输出;您可以通过下载 LTSpice 文件自己查看。以同样的方式,如果您实现 100 个通道,您将在每 1% 占空比的倍数处获得无纹波输出。

总之,通过部署更多具有适当均匀间隔相位延迟的 PWM 通道,可以在某些占空比下实现无纹波输出,即使在随机占空比下,仍然可以同时改善瞬态响应和噪声性能,这是传统单通道 PWM DAC 方法。

-

FPGA

+关注

关注

1629文章

21729浏览量

603017 -

PWM

+关注

关注

114文章

5181浏览量

213810 -

谐波

+关注

关注

7文章

822浏览量

41779

发布评论请先 登录

相关推荐

四通道相控阵PWM DAC电路解析

四通道相控阵PWM DAC电路解析

评论