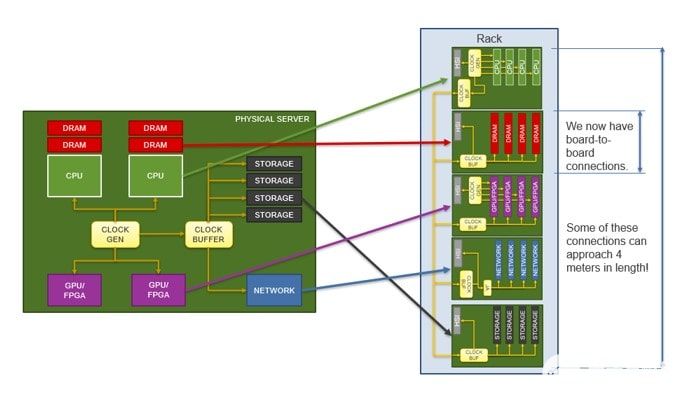

从历史上看,服务器将时间聚合到系统板上。现代服务器更普遍地将功能模块化并将设备迁移到不同的机架,例如 CPU、SSD、GPU、加速器、DRAM 卡等的托盘,如图 1 所示。

图像

图 1. 分解系统

对系统进行电源循环是一种理想的能力,但在分解系统中,调整整个系统的输入信号和电源序列变得更加复杂。理想情况下,系统始终通电;但在实践中,电源开启和输出时钟准备开启之间的时间差会有所不同。让我们来看一些与系统时钟设计相关的示例案例:

情况 1:无 VDD

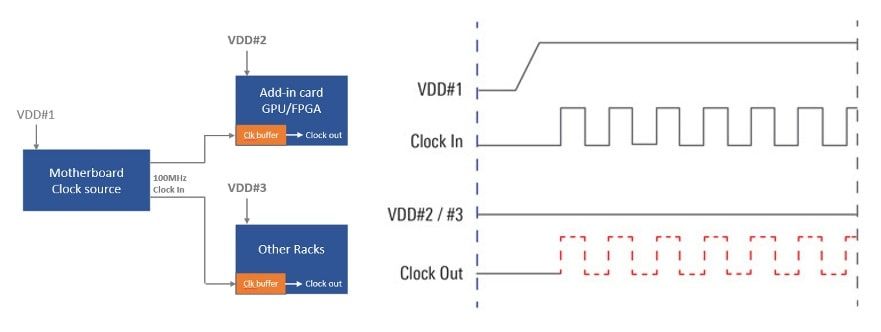

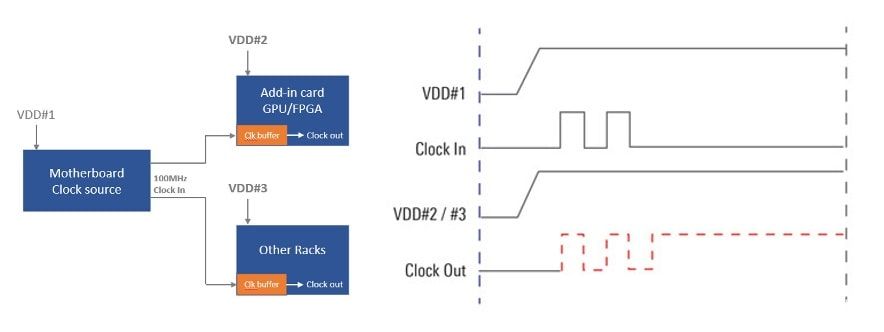

图 2 描述了在电源准备好之前主板将其时钟发送到其他机架和附加卡的场景。接收端的时钟缓冲器可能在其 VDD 开启之前就开始接收时钟信号,从而输出不良时钟信号。

图像

图 2. 无 VDD 时的错误时钟输出

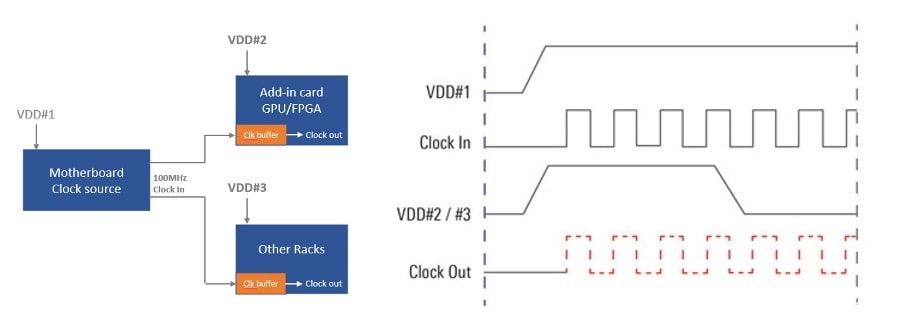

图 3 描述了时钟芯片在运行期间由于紧急中断(如系统过热、硬复位等)而断电的情况。智能时钟缓冲器可以在正确启用输出之前等待有效的 VDD。

图像

图 3. 系统关机时错误的时钟输出

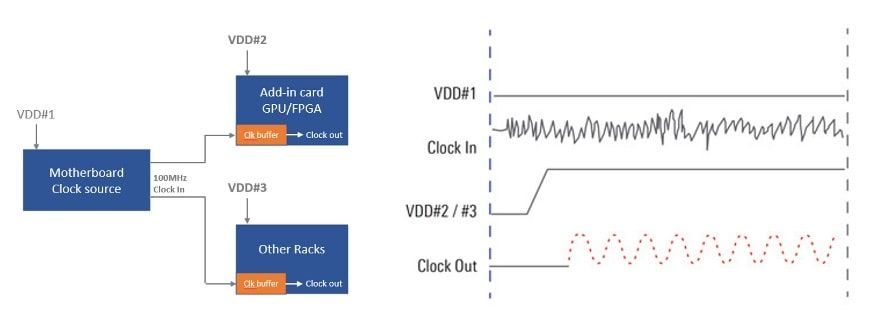

案例 2:噪声驱动时钟缓冲器输出振荡

如果时钟接收器侧的附加卡或机架首先上电,则接收器侧的附加卡或机架不一定会等待来自主主板的良好时钟源。如果您的时钟输入没有经过精心设计,您可能会触发 ESD 事件,或者时钟缓冲器输出可能会开始振荡以响应该刺激。智能时钟缓冲器内部具有监控有效输入时钟源的机制。

图像

图 4. 噪声输入导致时钟输出振荡

案例 3:泄漏问题

另一个常见问题是,当输入参考时钟消失时,时钟芯片的输出会停滞在高/低或低/高状态。HCSL 拓扑具有自然关闭特性,当它们被禁用时使用低/低状态。对于 LPHCSL 拓扑,如果没有将输入参考时钟同步到 OE、电源正常或断电引脚,这可能会导致问题。在这些情况下,系统应该断电,但时钟输出可能仍以 850mV 驱动,如图 5 所示。这种泄漏会给 CPU 增加不必要的热量。当输入上没有信号时,智能时钟缓冲器可以强制输出为低/低状态。

图像

图 5. 没有时钟输入时,输出仍以 850mV 驱动

帮助客户解决诸如此类的现实世界场景帮助我们定义了这样一个智能缓冲区。Renesas 的新型 PCIe Gen6 RC190024 / 20 / 16 / 13 / 08 / 04时钟缓冲器系列和RC19216 / 08 / 04 / 02多路复用器系列具有克服所有这些情况的内置功能,包括断电容限 (PDT )、灵活的启动序列 (FSS) 和 (自动时钟停放 (ACP)。所有这些对系统设计人员来说都是透明的,但可以在设计过程中轻松避免所有这些可能的陷阱。

审核编辑:郭婷

-

DRAM

+关注

关注

40文章

2315浏览量

183502 -

服务器

+关注

关注

12文章

9164浏览量

85430 -

Renesas

+关注

关注

0文章

1757浏览量

22764

发布评论请先 登录

相关推荐

关于如何解决MOS常见问题的方案参考

soc开发流程常见问题及解决方案

KeyStone设备的PCI Express (PCle)常见问题

如何解决4G工业路由器常见问题?

PCB设计中的常见问题有哪些?

如何解决同步时钟系统中的常见问题和故障?

步进电机常见问题及维护

如何解决PCIe时序设计的常见问题

如何解决PCIe时序设计的常见问题

评论