“软核”硬做-ODrive(FPGA版本)

之前稚晖君做了一个《机器人的心脏--超迷你FOC矢量控制驱动器》

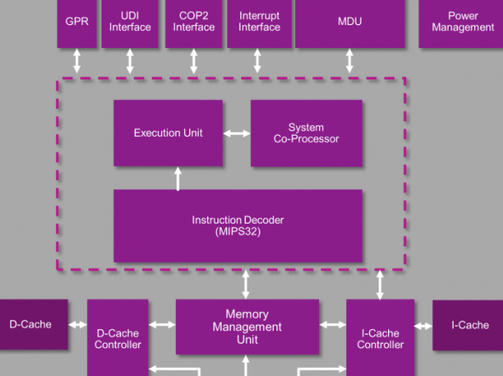

核心CPU是XX32FXXX,在工业控制领域其实FPGA占比也很大,所以能不能用FPGA做一个ODrive呢?答案是肯定的。

介绍

该项目旨在以低廉的价格准确地驱动无刷电机。目的是使在高性能机器人项目中使用廉价的无刷电机成为可能。像这样:

主要规格

控制两个电机。

提供 24V 和 48V 版本。

每个电机的峰值电流 120A。

持续电流取决于散热情况。

用于任意精确运动的编码器反馈。

支持两种制动模式:

制动电阻。

再生制动。

可选使用电池,意味着只需适度的电源即可实现非常高的峰值功率输出。

开源:硬件、软件

控制模式

Goto(带轨迹规划的位置控制)

位置命令

速度指令

扭矩指令

USB——自定义协议,开源

PC、树莓派等

步进/方向——现有的运动控制器

伺服 PWM/PPM——RC 接收器、Arduino 等。

CAN -- 基本自定义协议

一些通用数字和模拟引脚

硬件介绍

❝

https://github.com/madcowswe/ODriveHardware/tree/master/v2

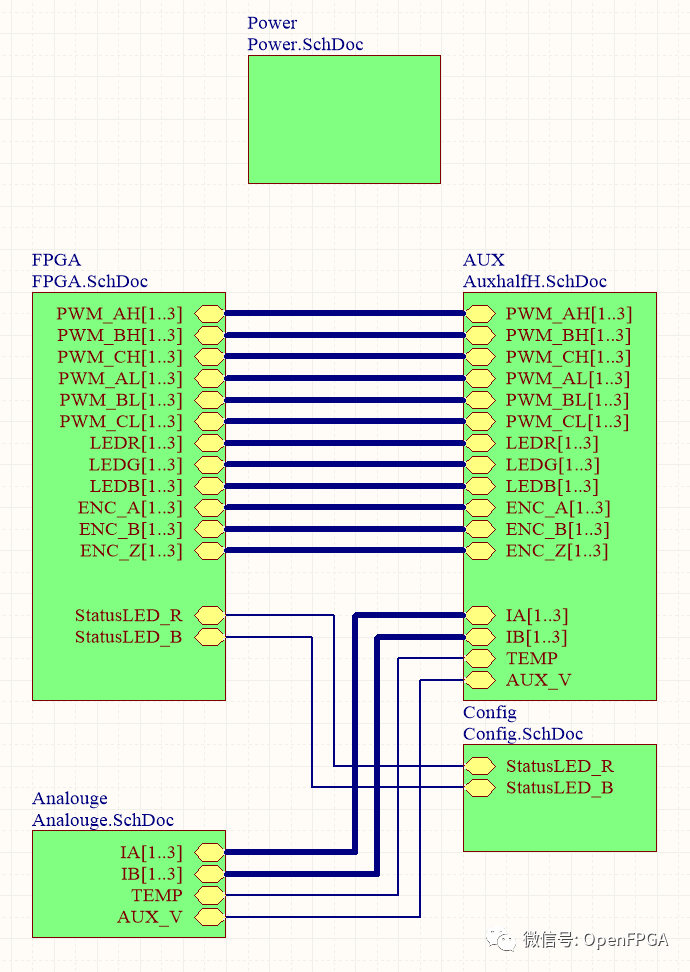

原理图TOP:

核心器件:

FPGA:10M08SAE144

电源:AP1117E33G-13、LM3490IM5-12/NOPB 这是给FPGA供电的,不需要太大电流

MOS:NTMFS4937NT1G

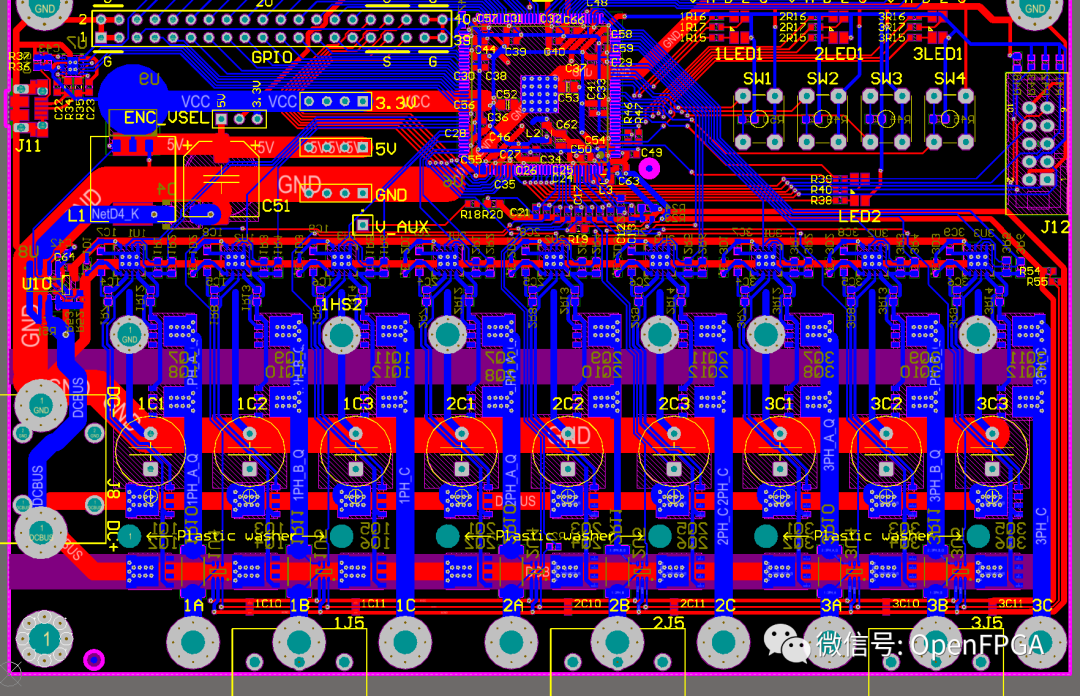

PCB欣赏:

版本勘误表:

编码器(M0、M1)的丝印标签是相反的。

在设计后置放大器滤波器时没有考虑电流放大器的输出阻抗。因此,响应比设计慢约 5 倍。因此,最大允许调制指数约为 50%。

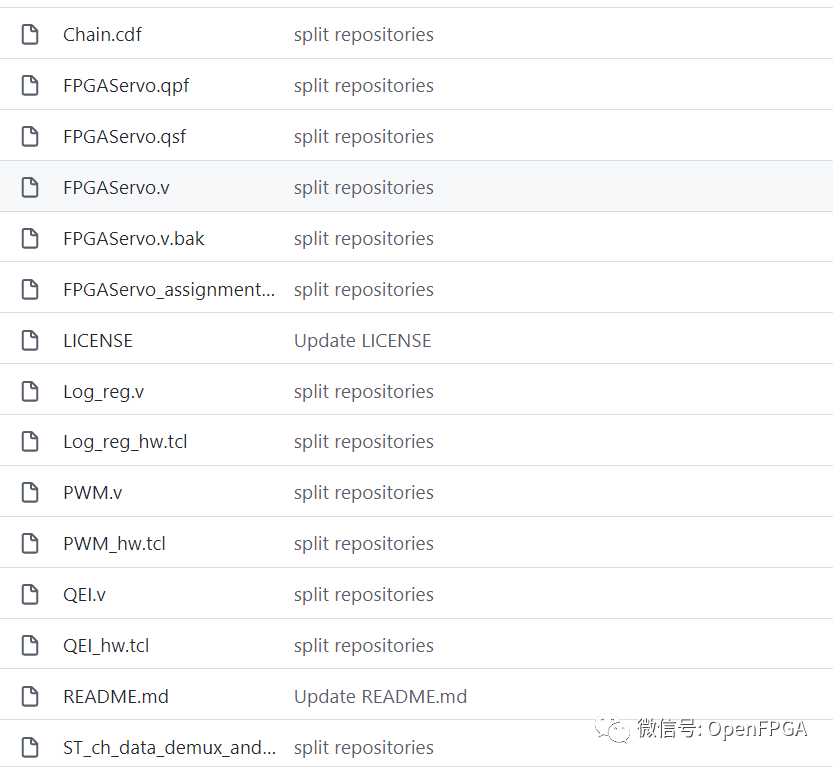

固件

代码地址:

❝

https://github.com/madcowswe/ODriveFPGA

EDA工具是QUARTUS_VERSION 13.1 ,整体逻辑不是很复杂。

官方网址:

https://odriverobotics.com/

审核编辑 :李倩

-

FPGA

+关注

关注

1629文章

21736浏览量

603419 -

电机

+关注

关注

142文章

9021浏览量

145501

原文标题:“软核”硬做-ODrive(FPGA版本)

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MIPSfpga软核处理器IP设计方案

FPGA的软核、硬核以及固核的概念

vivado版本升级后,怎么简单移植软核。

基于FPGA 的嵌入式ASIP 软核设计与实现

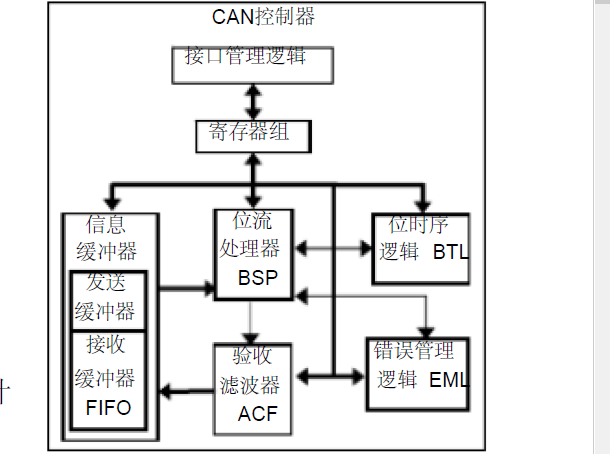

如何使用FPGA进行CAN控制器软核的设计与实现

FPGA硬核和软核处理器的区别

FPGA 系统中的处理器核们(二):软核,可杀鸡亦可屠龙?

“软核”硬做-ODrive(FPGA版本)

“软核”硬做-ODrive(FPGA版本)

评论