今天看《集成电路时序分析与建模》中看到这么一个知识点,觉得有点意思,就记录下来,与大家一起分享。

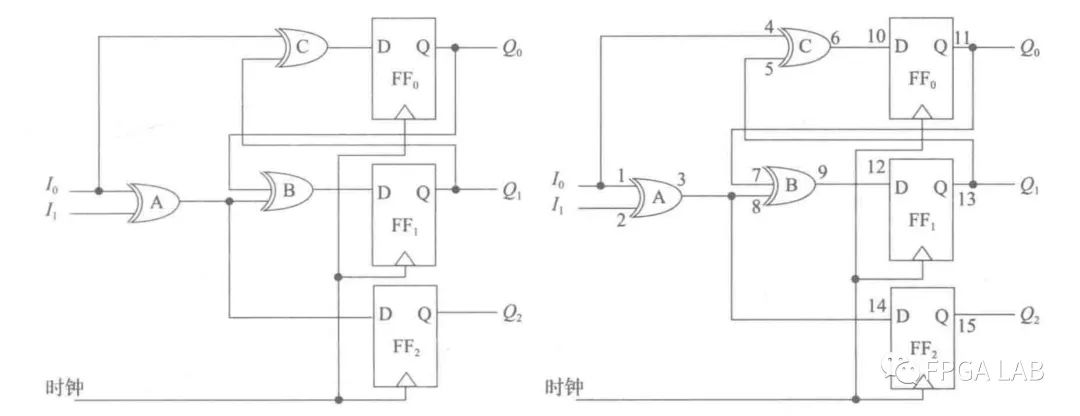

先看 如下电路图:

左边的电路图是需要分析的电路,我们的目的是要对此电路进行时序分析,那首先要找到该电路需要分析的时序路径,既然找路径,那找到时序分析的起点与终点即可。

寻找时序路径的起点和终点的原则如下:

起点:

设计边界的数据输入端口或信号输入端口;如上图右边的I0,I1;

时序元件(一般指DFF)的输出,例如上图右边的11,13,15;

存储单元的数据输出,其实这和第2条一致,时序单元也是存储单元,例如DFF,但这里的存储单元一般指存储器,例如RAM等;

终点:

时序单元的数据输入,例如上图右边的10,12,14;

存储单元的数据输入,类似于时序单元,但更多指存储器等,例如RAM等;

设计边界的输出Q0,Q1,Q2;

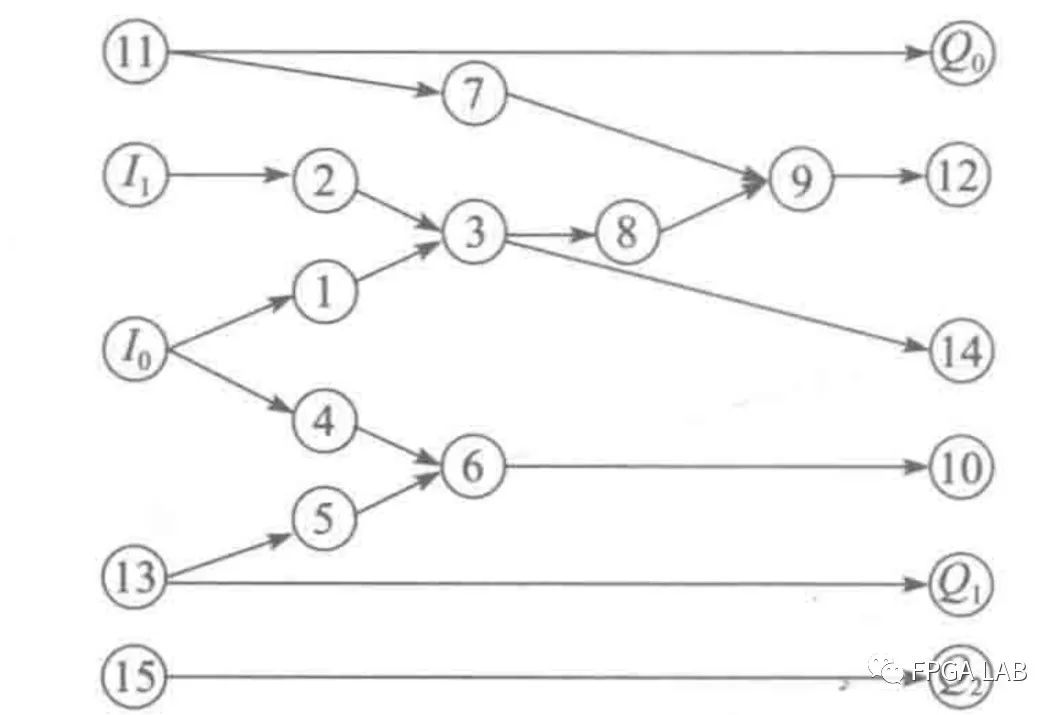

根据上述原则即可得到,时序分析的起点(最左边)和终点(最右边):

时序路径

中间经过的节点都可认为是延迟单元。

实际进行时序分析时,可不必每次都这么转换,但是不得不说,这种理论化的方式可以让你的分析更具理论支撑,见多了熟悉了之后便可更快速的识别时序路径。这是分析的第一步,祝入门快乐。

审核编辑 :李倩

-

集成电路

+关注

关注

5397文章

11667浏览量

364267 -

时序

+关注

关注

5文章

392浏览量

37492

原文标题:【静态时序分析】如何寻找时序路径的起点与终点

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成电路设计中静态时序分析介绍

亿纬锂能荣获双项起点金鼎奖

使用霍尔效应传感器针对篡改和移动终点位置检测实现限制检测

锁存器的基本输出时序

时序逻辑会产生锁存器吗

起点,经过点,终点,三点xyz,画三维圆弧。

电源时序器属于控制继电器吗

电源时序器输出电压多少伏

电源时序器的原理及使用方法是什么

FPGA 高级设计:时序分析和收敛

Xilinx FPGA编程技巧之常用时序约束详解

FPGA工程的时序约束实践案例

如何寻找时序路径的起点与终点

如何寻找时序路径的起点与终点

评论