DDR5 系统管理引入了一种全新的边带总线,其正式名称为 JESD403-1 JEDEC 模块边带总线。 DDR5 标准的开发正由 JEDEC 和 MIPI 联盟合作进行。

在引入这种全新应用的情况下,该应用所用到的 SPD 集线器、PMIC 和微控制器需要在确保协议合规性的基础上实现高度集成。 因此,瑞萨开发了一种结合瑞萨 SPD5 集线器 SPD5118、瑞萨 PMIC、温度传感器和新款瑞萨 RA RA2E2 组的解决方案,以实现符合 JEDEC JESD403 和 MIPI I3C BasicSM 要求的边带总线操作。 另一方面,这些关键的瑞萨设备已通过 MIPI I3C BasicSM 的全面认证,并且该系统还能够向后兼容旧版 JEDEC I2C 实施。

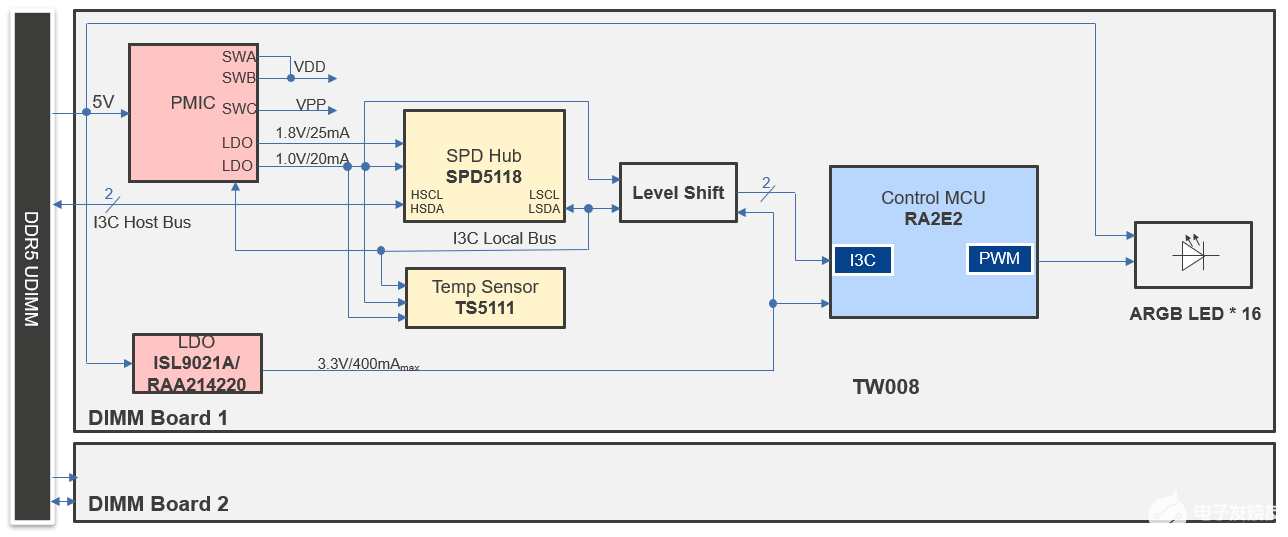

DDR5 DIMM 边带总线和主机总线的简要架构

瑞萨 DDR5 解决方案附带原型套件,可配合上述的总线和电源布局架构使用,并在 RA I3C 总线的前端采用了电平移动电路,以满足 JESD403-1 的特定总线电压要求。 客户可以通过他们的 SDRAM 模块充分利用此集成套件,从而加速产品发布计划。

管理总线协议

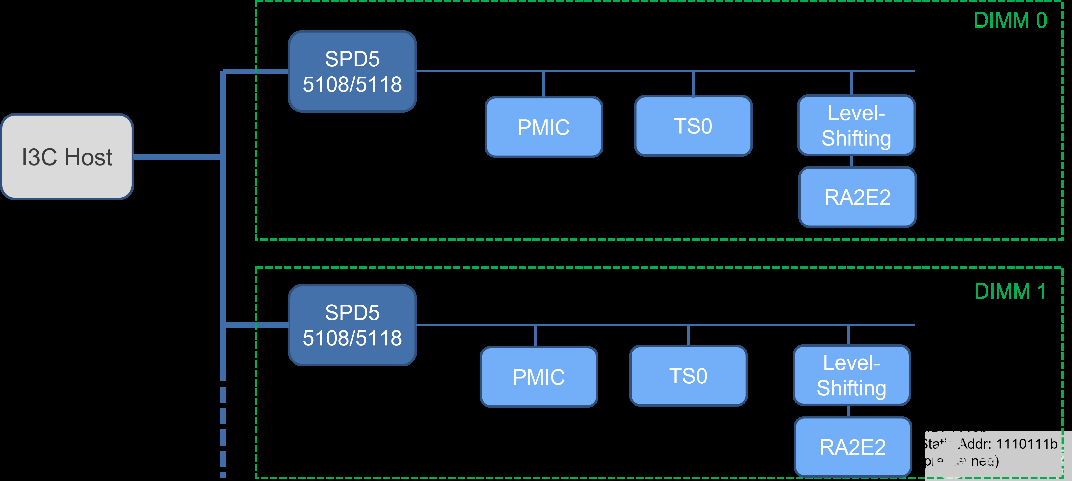

边带总线采用特定的结构化寻址方案(如下文简述)来识别 DIMM 以及 DIMM 上的设备。 因此,I3C 基础的 ENTDAA 和基于 PID 的地址计算方案并不需要强制执行。 基于此情况,SPD 集线器通过两个模式处理地址计算和 HID 分配,而 DIMM 上能够以 I3C 基础模式运行的设备应为 JEDEC SETHID CCC 和 SETAASA CCC 提供支持。

在 JEDEC I2C 模式中(默认通电),通信(以 DIMM 上的设备为目标从属设备)由主机发出启动条件开始,后接 7 位从属地址和一个读/写字位。 通信过程中,作为首个接收器的 SPD 集线器将替换寻址 DIMM 的从属地址的 LSB 3bits(HID)并转发到本地总线,不包括 0x7E 的广播地址。 SPD 集线器借助精密电阻检测 HID/DIMM_ID 并辅助 HID 分配。

JEDEC I3C 模式将一直生效,直至作为边带总线上首个接收器的 SPD 集线器接收到 JEDEC SETHID CCC 为止。 一旦集线器检测到 JEDEC SEHID CCC,集线器便会停止 HID 数位翻转,并将传入的 7 位从站地址按原样透明地传送到本地总线中。 在此操作之后,DIMM 上所有从 SPD 集线器接收 SETHID CCC 的 I3C 设备应更新其静态地址分配,并等待 SETAASA CCC 完成地址分配以进入 I3C 基础操作。

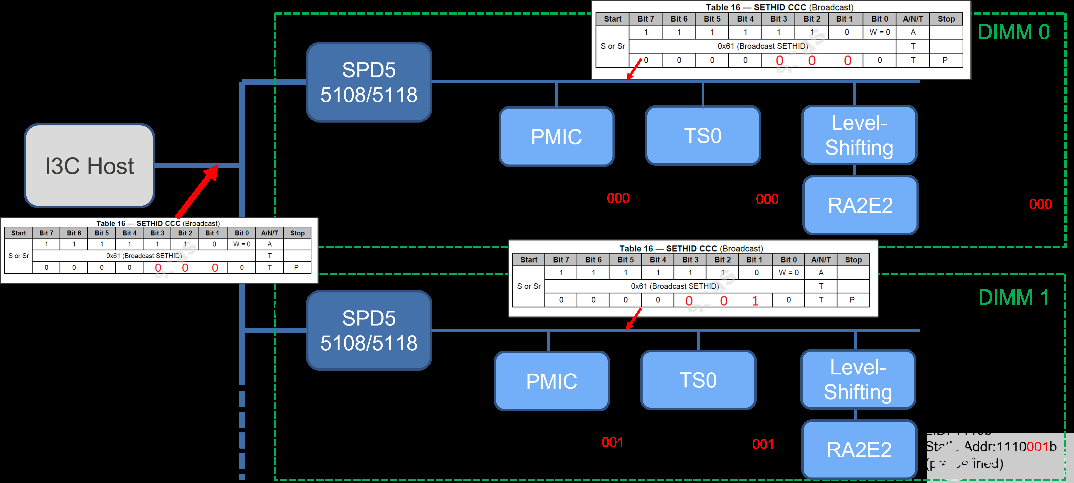

下图对上述两种模式的操作说明进行了汇总。

在收到 JEDEC SETHID CCC 之前,I2C 模式默认通电。

接收到 JEDEC SETHID CCC 时进入 I3C 模式。

RA2E2 组包含全面通过 MIPI I3C BasicSM 认证的 I3C 接口,可向后兼容旧版 JEDEC I2C 实施,设计师能够简化硬件设计,同时轻松而顺畅地实现从旧版 I2C 平台到 I3C 平台的转移。

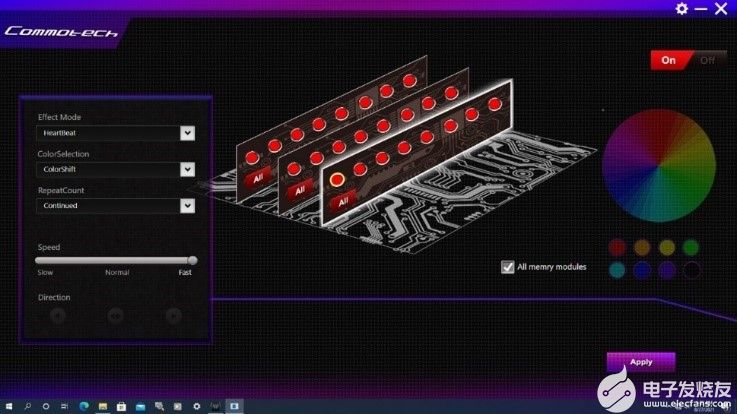

DDR5 ARGB LED 控制实施

RA2E2 组在尺寸仅为 4.00 x 4.00mm 的 24 引脚 HW 四方扁平无引脚 (HWQFN) 封装中提供 6 通道的通用 PWM 定时器。 借助硬件支持,可以通过最大化可控 ARGB LED 阵列的数量来拓展照明效果的选项。

演示和验证

作为 MIPI 联盟的成员和较早采用 MIPI I3C Basic SM 和 JEDEC JESD 403-1 的先行者,瑞萨解决方案的边带总线运行和协议合规性验证已通过 Prodigy I3C协议分析器和模拟器完成,可支持 MIPI I3C Basic V1.0, V1.1 规格。 此外,瑞萨解决方案能够向后兼容 SM 总线,以满足英特尔目前对 LED 照明控制的 DDR4 和 DDR5 结构要求,而瑞萨的第三方合作商也将提供包括 H/W、F/W 和 S/W 在内的全套解决方案,从而改善整体开发环境。

审核编辑:郭婷

-

英特尔

+关注

关注

61文章

10035浏览量

172514 -

模拟器

+关注

关注

2文章

886浏览量

43462 -

DDR5

+关注

关注

1文章

431浏览量

24250

发布评论请先 登录

相关推荐

【RA-Eco-RA4E2-64PIN-V1.0开发板试用】+03+UART+控制舵机+控制LED

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

Rambus推出DDR5客户端时钟驱动器,将业界领先的内存接口芯片产品扩展到高性能 PC领域

Introspect DDR5/LPDDR5总线协议分析仪

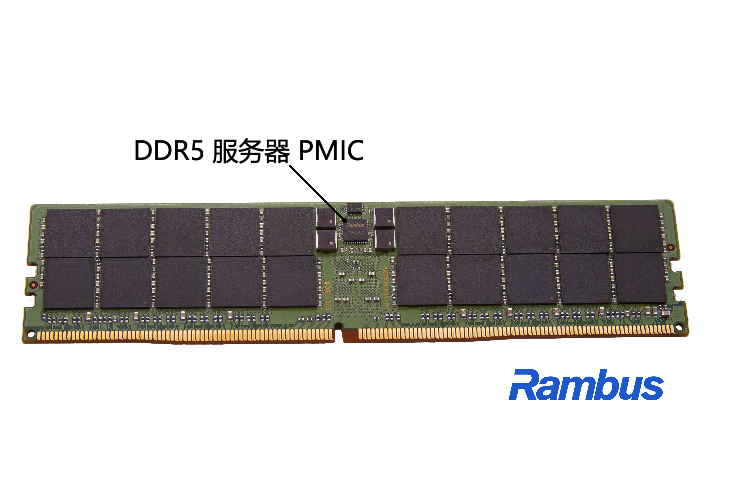

Rambus 通过 DDR5 服务器 PMIC 扩展适用于高级数据中心内存模块的芯片组

适用于DDR5 On-DIMM 电源的TPS53832集成式数字降压转换器数据表

适用于DDR5 On-DIMM电源的TPS53830集成式数字降压转换器 数据表

适用于DDR5 On-DIMM 电源的TPS53832A集成式数字降压转换器数据表

适用于DDR5 On-DIMM 电源的TPS53830A集成式数字降压转换器数据表

适用于单节电池的I2C控制型3A降压电池充电器BQ25622E数据表

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

适用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF缓冲基准的TPS51206 2A峰值灌电流/拉电流DDR终端稳压器数据表

RA2E2单片机组适用于DDR5 DIMM LED的控制应用

RA2E2单片机组适用于DDR5 DIMM LED的控制应用

评论