在本文中,我们将讨论一种大大增加收敛概率的方法,并在缩短模拟时间的同时实现这一目标。在振荡器嵌入数百个其他电路块的层次结构中,这种技术已被证明在获得收敛方面是有效的。

初始设置

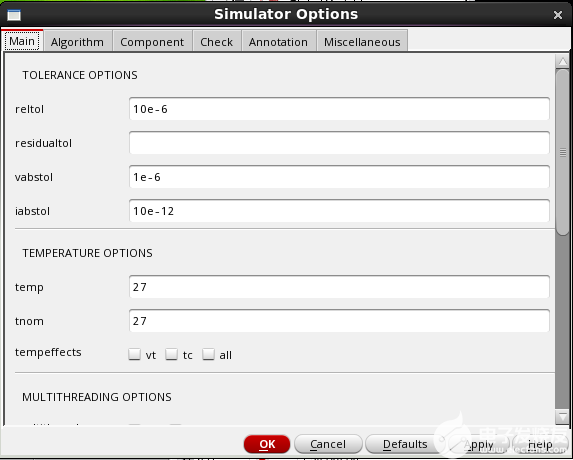

重要的是设置模拟选项,以最大限度地减少 Spectre 在寻找解决方案时的工作,以便当 PSS 确实收敛时;它实际上收敛到一个准确的结果。有一些默认的 Spectre 设置过于严格,对于大多数设计来说,这只是等待发生的意外——例如,“iabstol”。然而,对于高 Q xtal 振荡器,默认的 reltol 精度是不够的。

建议的起点是:

reltol=10e-6

iabstol=10p

gmin=10p

Spectre/SPICE 默认值通常为 1pA 的电流容错和 0.1% 的相对容差。使用标准双精度算法时,SPICE 只能在变量跨越不超过约 12 个数量级的范围时收敛,因此 1pA 对大多数电路来说是非常苛刻的。对于大电流,将此值增加到 100 pA 甚至 1 nA 有时是个好主意。然而,为了获得可靠的相位噪声精度,0.1% 的默认 reltol 还远远不够。

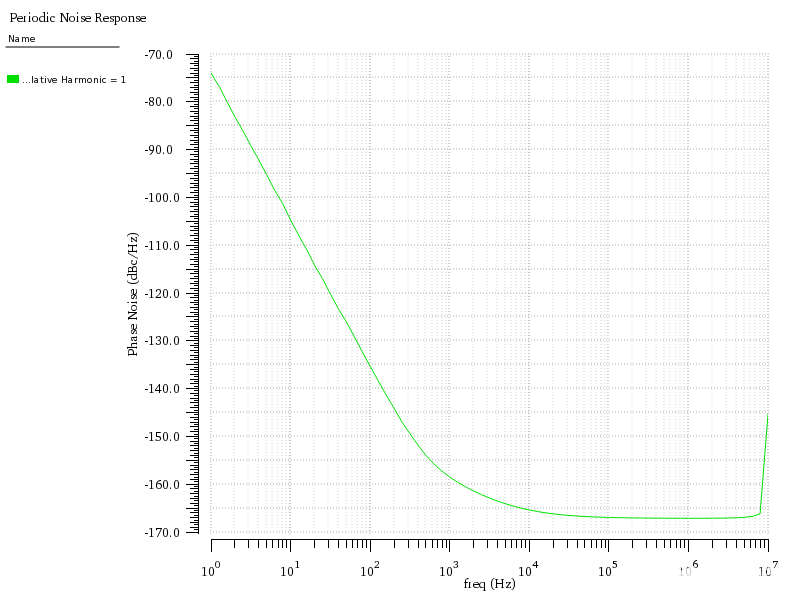

一个合理的起始值是 10e-6,但对于某些电路,这需要增加到 1e-6。不准确结果的一个明显迹象是相位噪声图中存在阶跃跳跃。

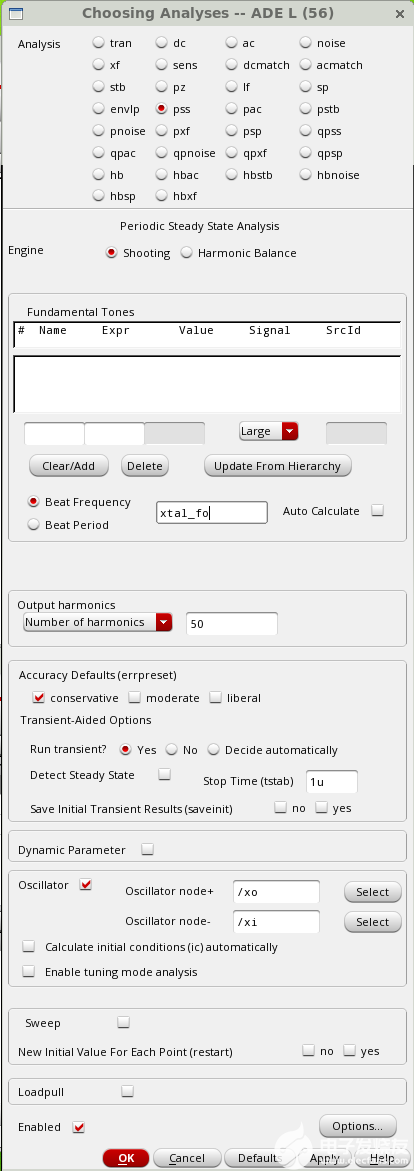

PSS 设置

必须设置 PSS 表格,以便始终执行预反式运行“tstab”。广泛的模拟表明,对于难以收敛的振荡器,旨在提高收敛性的选项基本上总是失败。那就是永远不应该使用检测“稳态”和“计算初始条件”。

建议的起点是:

谐波数=50

精度默认值=保守

运行瞬态=YES

停止时间=如下所述

检测稳定=未启用

计算初始条件=未启用

除了简单的正弦波输出之外,Shooting Method 通常是任何振荡器系统的最佳方法。大多数振荡器应用都需要平方限制器,以使系统具有高度非线性。因此,50 个谐波的默认值是一个很好的起点。对于特别困难的电路,可能需要 100 个谐波。同样,如果整体相位噪声图不平滑,则表明该图很可能是错误的。保守的精度设置向 Spectre 发出信号,要求实际上使 retol 的初始 10e-6 设置更加严格。

请注意,像往常一样,将振荡器节点设置为 XTAL 节点。

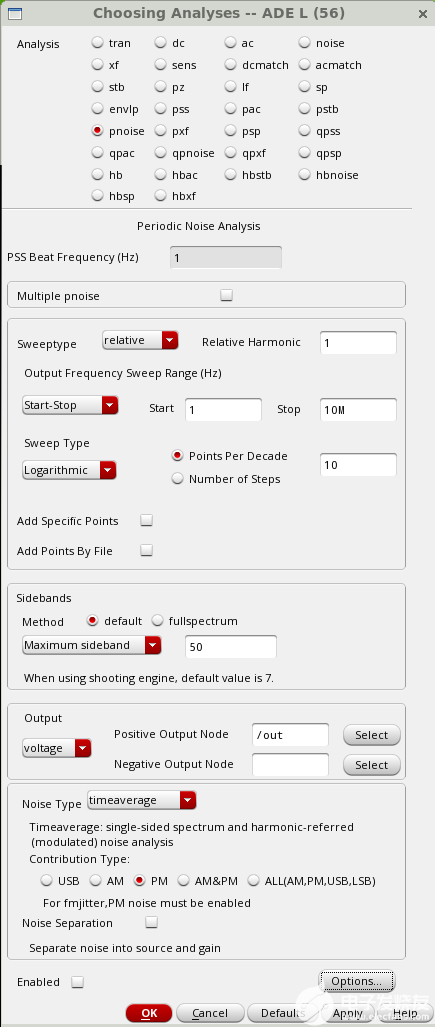

PNoise 设置

PNoise 设置是相对标准的。为了准确起见,将默认的最大边带设置为 50。

为了减少仿真时间,但仍能获得合理的平滑图,每十倍频点 10 点的对数图通常就足够了。通常只关注相位噪声,因此请选中相应的框。

输出/绘图设置

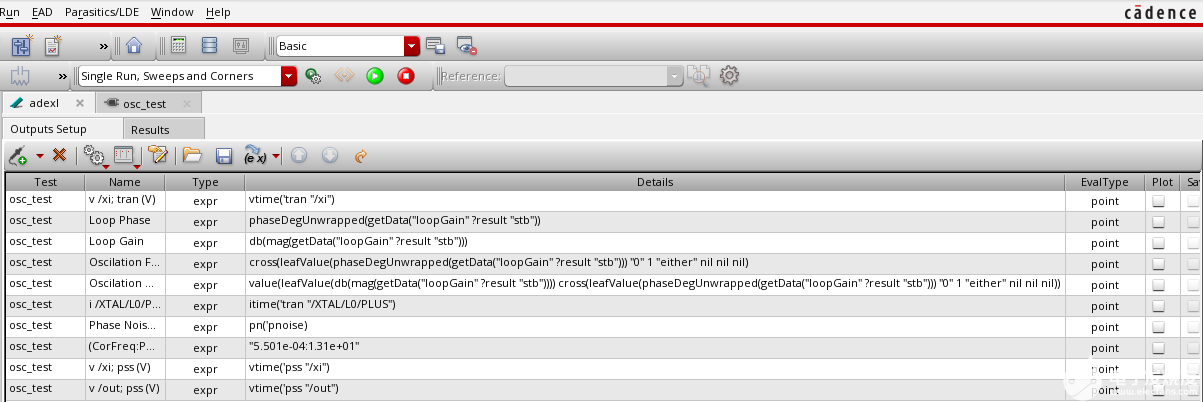

为确保振荡器实际工作,应首先运行节奏稳定性分析。

不幸的是,在撰写本文时,Cadence Stability Analysis 存在一个基本缺陷,即阻止使用其直接绘图功能输出环路增益裕度和环路相位裕度。(这是呃。. ahhmmm 。..。..尽管工单已提交给他们的 ahmmm 。..。..支持部门。..。..)

Cadence Spectre 日志将生成以下内容……

“ 警告 (SPECTRE-16922):由于电路是正反馈系统且不稳定,因此无法获得相位裕度和增益裕度。这是因为当 loopGain 的相位过零时,loopGain 的幅度在 10.003 MHz 处大于 1。为了使电路稳定,当loopGain的相位过零时,要保证loopGain的幅度小于1。”

所以,当然,它是一个振荡器!无论如何,只要吐出结果 Dah!…

所以。..。..输出表单应该使用手动脚本设置,如下所示:

循环阶段

phaseDegUnwrapped(getData(“loopGain” ?result “stb”))

环路增益

db(mag(getData(“loopGain” ?result “stb”)))

振荡频率

cross(leafValue(phaseDegUnwrapped(getData(“loopGain” ?result “stb”))) “0” 1 “either” nil nil nil)

振荡增益

值(leafValue(db(mag(getData(“loopGain”?result“stb”))))cross(leafValue(phaseDegUnwrapped(getData(“loopGain”?result“stb”)))“0”1“任一”无无零))

有时,根据电路的不同,相位会发生 360 度的整体偏移,因此应适当修改交叉点“0”。

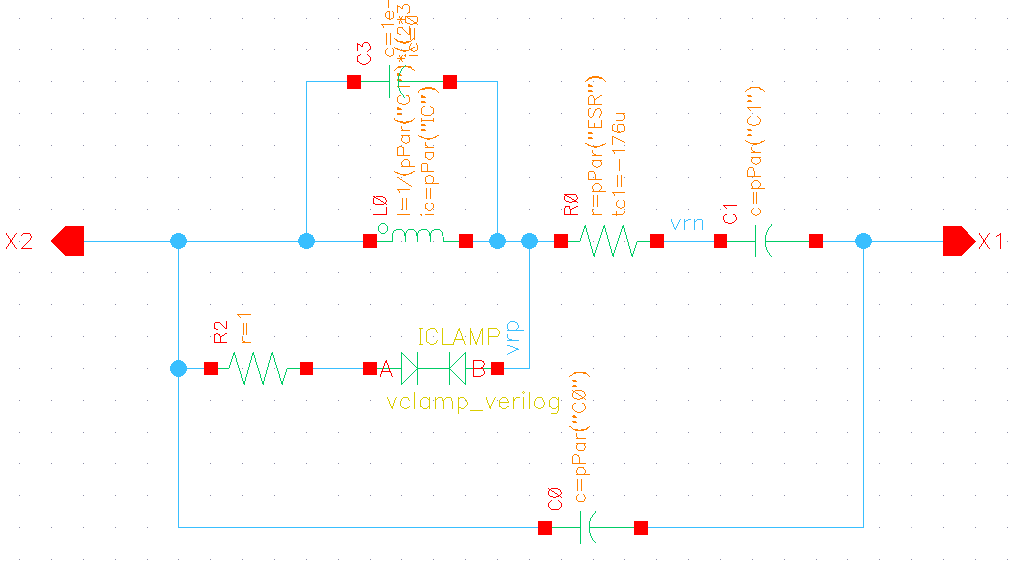

XTAL 模型设置

应设置 XTAL 的原理图,以便原理图根据 XTAL 的 c1 和 XTAL 频率计算所需的 XTAL 电感。

因此,电感器在其设置形式的电感字段中应具有以下设置:

1/(pPar(“C1”)*((2*3.141592654*pPar(“FS”))*(2*3.141592654*pPar(“FS”))))

组件 ICLAMP 是一个 Verilog 电压/电流限制器,有助于收敛,因为高 Q XTALS 可以生成 100kV 类型的数字,因此 SPICE 在收敛过程中可以产生更高的电压。它有助于避免那些“最后收敛节点=123.8 MV”的错误。但是,这可能不是必需的。

它的代码是:

`包括“constants.vams”

`包括“学科.vams”

模块 vclamp_verilog(A, B);

输入A;

电气 A;

输入 B;

电气 B;

参数实 imax = 0.5 ;

参数实 vmax = 1 ;

参数实 i0 = 1E-18;

模拟开始

I(A,B) 《+imax*tanh(i0*sinh(100*tanh((40/vmax/100)*V(A,B))));

结尾

电感两端的电容是一个非常小的虚拟电容,通常为 1e-20F。作为将电感器两端的初始电压强制为 0V 的便捷方法,这是必需的。此节点电压设置是此收敛技术的一部分。

收敛法

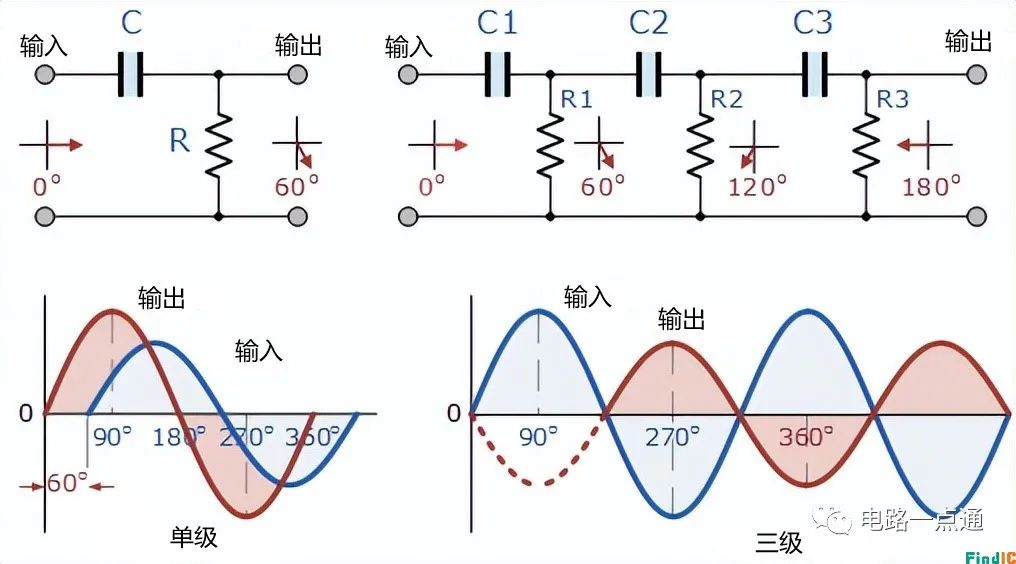

高 Q XTALS 收敛的问题是 Spectre 难以收敛,仅仅因为 Q 高。对于相同的电路,但 Q 值较低,通常问题不大。因此,该方法是求解低 Q 电路并使用该结果来帮助求解全 Q 值。

关键原则是低 Q XTAL 将比高 Q XTAL 更快地达到其稳态值。也就是说,如果 XTAL 以 100 倍“去Qed”,那么模拟的稳定速度将快 100 倍。

XTAL 振荡器的 Q 值由 XTAL 的 C1(串联电阻)决定。然而,XTAL 电感器中的稳态电流与 C1 无关。因此,低 Q 电感电流可用作全 Q XTAL 的初始电流。

因此,该方法的原理是将电感器电流初始化为接近稳态时的电流,该电流通过首先运行低 Q 版本的电路来确定。

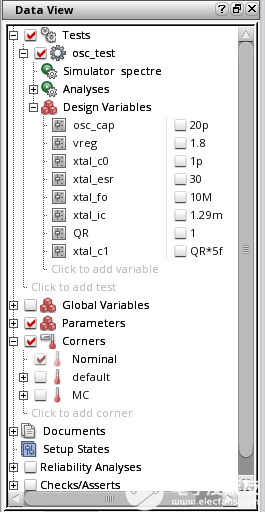

设置模拟的一种方便方法是引入一个变量(例如 QR),它与 C1 相乘,因此首先将 QR 设置为 100 用于低 Q 运行,然后设置为 1 用于完整 Q 运行。例如:

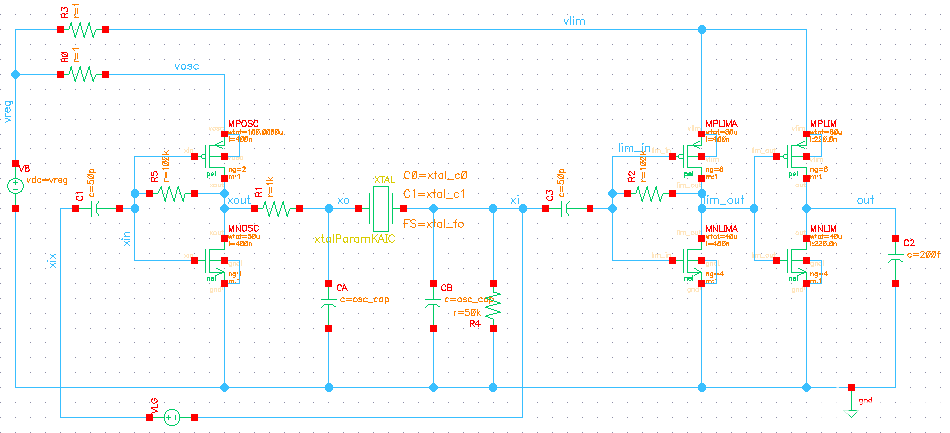

示例示意图

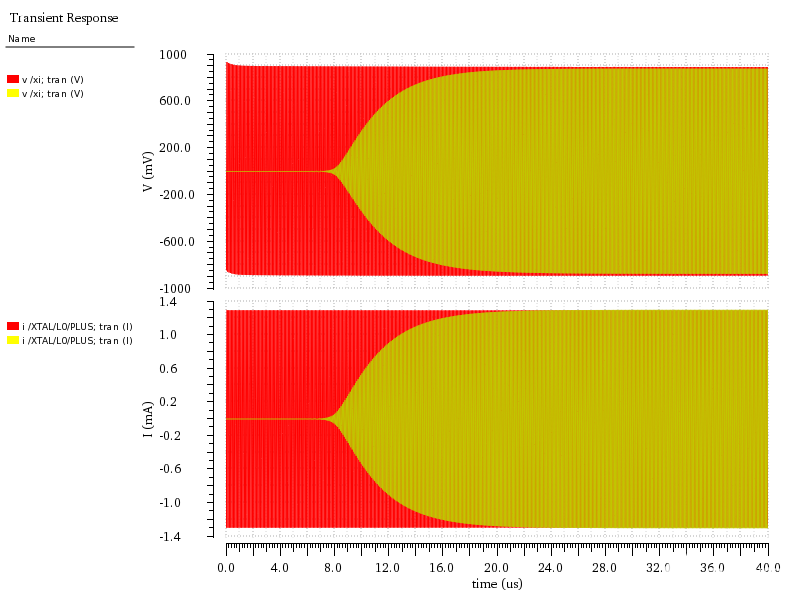

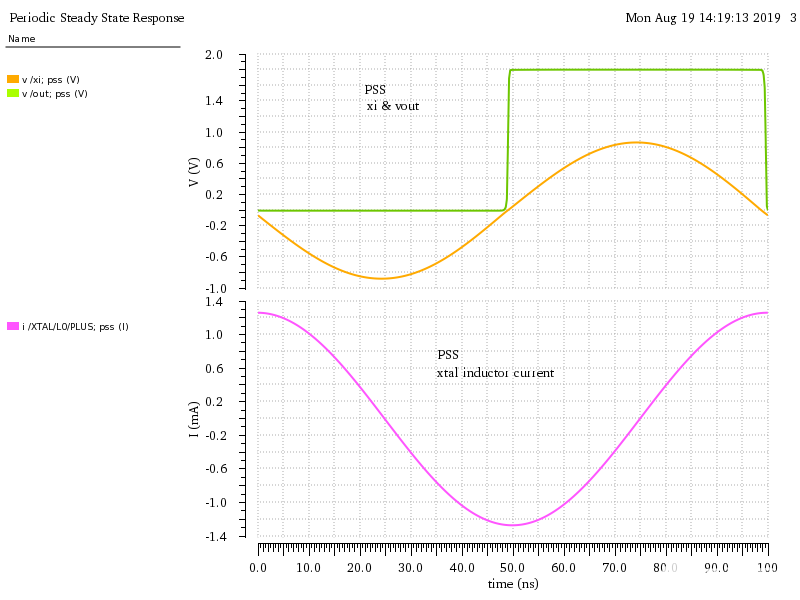

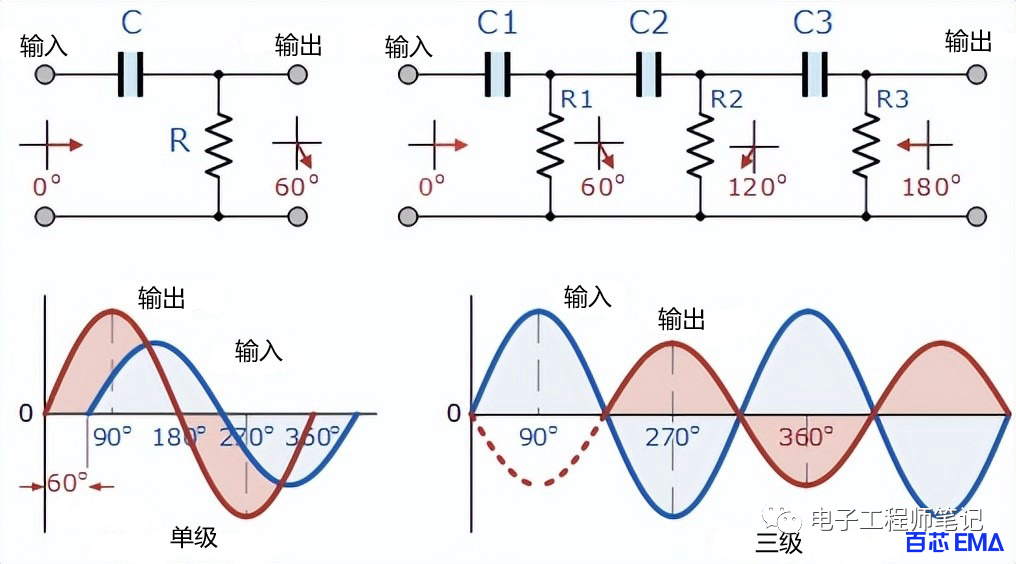

示例波形

上图显示了低 Q 和高 Q 运行时 X1 处的信号电压。下图显示了低 Q 和高 Q 运行的电感器电流。

可以看出,从低 Q 配置确定的值允许高 Q 配置基本上立即启动。

这使 PSS 有一个更好的起始条件,因此它更有可能收敛。在这种特殊情况下,PSS tstab 时间仅设置为 1us。对于困难的情况,需要根据经验确定。

特兰

PSSR

相位噪声

-

振荡器

+关注

关注

28文章

4191浏览量

143153 -

相位噪声

+关注

关注

2文章

197浏览量

23803

发布评论请先 登录

无刷双馈异步电机潮流建模和收敛性研究

B值独立同分布随机变元序列矩完全收敛性

B值同分布鞅随机列矩完全收敛性的注记

基于量子粒子群算法的收敛性研究

振荡器,振荡器的分类,振荡器的特性

压控振荡器,压控振荡器是什么意思

板级模拟电路仿真收敛性技术研究

关系模型的进化算法收敛性对比的详细资料说明

一文解读PSpice中的收敛性问题及其相关因素

如何获得高QXTAL振荡器的收敛性

如何获得高QXTAL振荡器的收敛性

评论