本文描述了有限状态机的基础知识,并展示了在 Verilog 硬件描述语言中实现它们的实用方法。

有限状态机,简称 FSM,是硬件和软件系统中最普遍的操作模型之一。几乎每个有用的数字系统都可以定义为有限状态机,因此最好尽可能多地了解这种有用的系统模式。

数字电路中的有限状态机

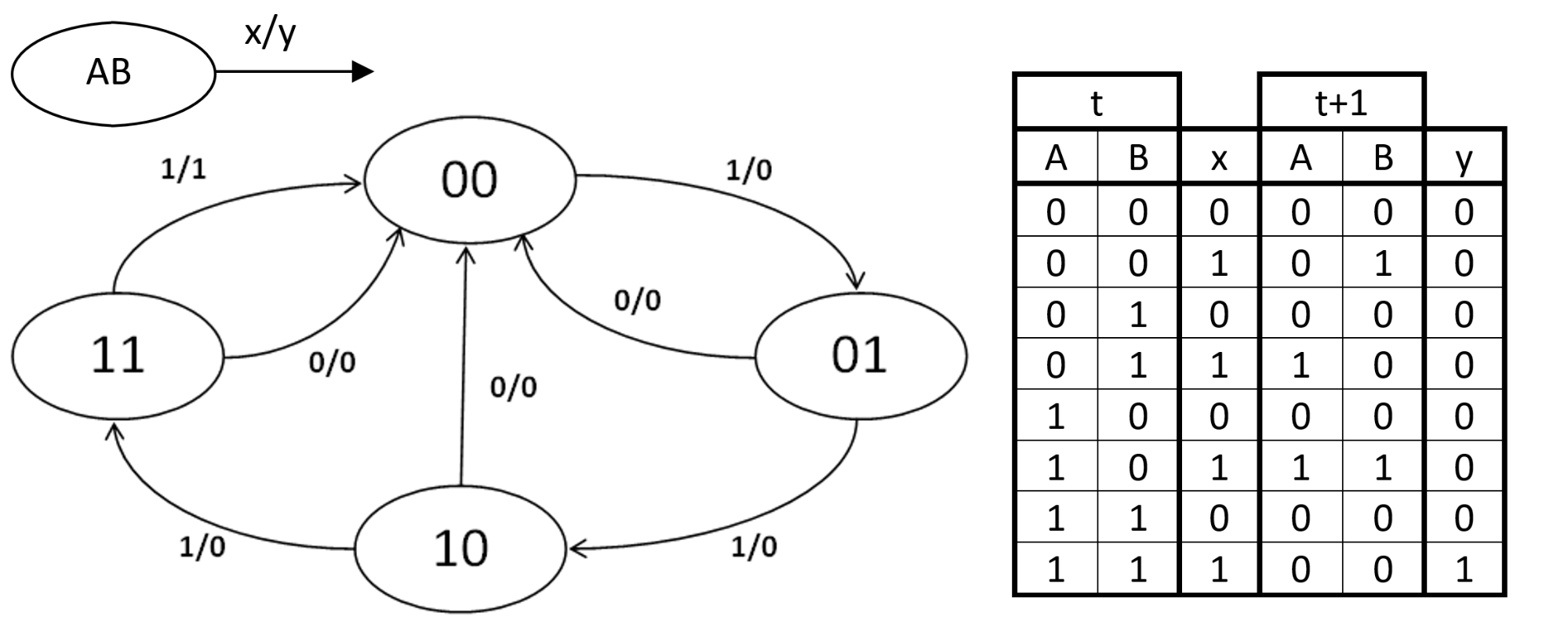

有限状态机有多种描述方式,但最流行的两种是状态图和状态表。两种表示的示例如图 1 所示。

图 1.显示为状态图和状态表的 FSM。左上角的图例显示了状态变量 A 和 B,以及输入 x 和输出 y。

请注意,这个 FSM 有一个输入信号 x 和一个输出信号 y,这使它成为一个Mealy 状态机。此 FSM 可以通过数字设计课程中教授的传统方法来实现,该方法围绕为实现状态变量的触发器生成激励逻辑。该逻辑是根据所选触发器类型的激励表设计的,即 SR、D、JK 或 T。

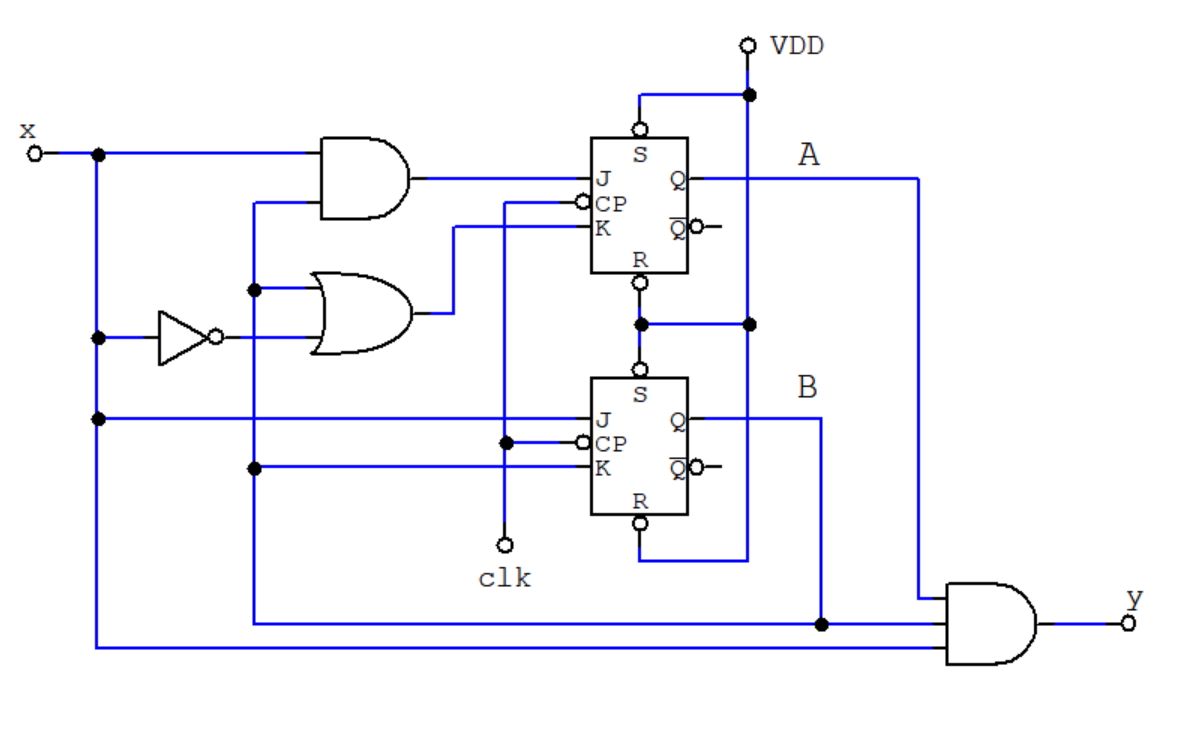

当我们将此技术应用于图 1 中的 FSM 时,我们会得到以下实现的某个版本。

图 2.使用 JK 触发器的示例 FSM 的实现。

有关状态机的更多信息,您可能需要阅读 David Williams的文章在 VHDL 中实现有限状态机。

Verilog 如何提供帮助

那么,如果您想在 Verilog 中实现如图 1 所示的状态机,该怎么做呢?Verilog 应该在设计过程的哪个阶段接管?

虽然可以 手动设计整个系统,一直到图 2 中的示意图,然后用 Verilog 编写代码,但这并不是解决问题的最流行的方法。更糟糕的方法是描述原理图中的每个门,包括构成触发器的门!如果您在门级别描述所有内容,您的系统可能会 以某种方式工作,但这没有给编译器留下空间来优化您的设计以满足您的实际 需求,这可能更关注时序和功率,而不仅仅是正确性。

请记住:使用硬件描述语言的原因是为了利用您将使用的综合编译器,并且像任何编译器一样,您给予它的自由度越大,您就越有可能产生最佳实现。

所以一个聪明的起点是状态表。您只需指示 Verilog 机器在每个状态下应该做什么,而不是使用哪个门或触发器。

在 Verilog 中,状态机的一个出色构造是Case 语句。每个案例的主体都应该检查状态变量及其期望的行为。下面的一段代码展示了这个结构。

case (state)

STATE_0: // Code for State 0

STATE_1: // Code for State 1

// ...

STATE_N: // Code for State N

endcase

因此,通过我们的示例,这是图 1 所示状态机的实现。请注意,输出 y 是一个组合函数。

module MyFSM(

input clk,

input x,

output y);

reg [1:0] state;

assign y = state[1] & state[0] & x;

always @ (negedge clk)

case (state)

2'b00: state <= x?2'b01:2'b00;

2'b01: state <= x?2'b10:2'b00;

2'b10: state <= x?2'b11:2'b00;

2'b11: state <= 2'b00;

endcase

endmodule

-

Verilog

+关注

关注

28文章

1351浏览量

110216 -

状态机

+关注

关注

2文章

492浏览量

27609

发布评论请先 登录

相关推荐

有限状态机的建模与优化设计

VHDL有限状态机设计-ST

初学者对有限状态机(FSM)的设计的认识

如何使用FPGA实现序列检测有限状态机

基于事件驱动的有限状态机介绍

基于事件驱动的有限状态机介绍

一个基于事件驱动的有限状态机

如何在Verilog中创建有限状态机

如何在Verilog中创建有限状态机

评论