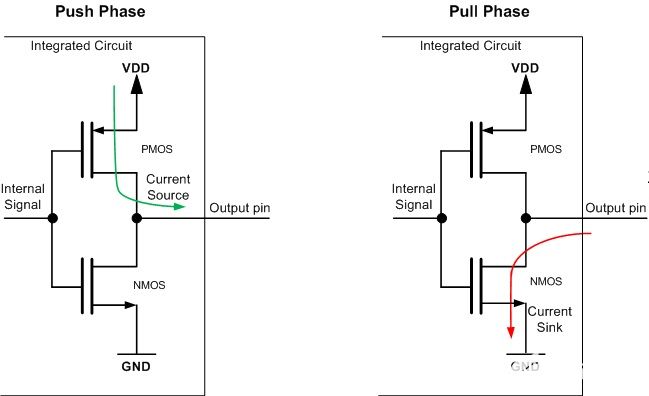

推挽输出又叫推拉输出,是最常见的输出配置了,正如它的名字那样,推拉输出能够驱动输出两种电平。一种是拉接到地(从负载灌入电流),另一个被推到电源电压(输出电流到负载)。推挽输出可以使用一对开关来实现。在集成电路中一般使用两个晶体管搭建。在下图中,我们可以看到使用 PMOS 和 NMOS 晶体管构建推挽输出配置。左侧显示的是推阶段的电路状态,右侧显示的是拉阶段的电路状态。

1.推挽电路工作原理

推动阶段——当连接到晶体管栅极的内部信号设置为低电平时,PMOS 晶体管被激活,电流从 VDD 流经它到输出引脚,NMOS 晶体管处于非活动状态(开路)且不导通。

拉动阶段——当连接到晶体管栅极的内部信号设置为高电平时,NMOS 晶体管被激活(关闭)并且电流开始从输出引脚流过它到 GND。同时,PMOS 晶体管处于非活动状态(开路)并且不传导电流。这种类型的输出不允许在总线配置中将多个设备连接在一起,推挽配置最常用于具有单向通信线上(线路上的信号传输仅在单一方向,比如SPI、UART等)。

2.电路应用注意事项

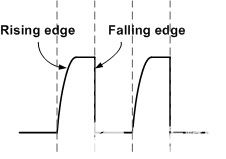

推挽输出在生成的输出数字信号的斜率方面提供了更好的性能,现在很多IC甚至可以配置信号上升或者下降的斜率,从而允许我们在传输速度和EMI方面找到最佳的平衡点。上升沿斜率——上拉电阻与线路的固有电容相结合,形成一个低通滤波器。从而我们可以根据电阻器的值和线路的电容来调整上升沿斜率,上升沿的斜率与下降沿的斜率可能存在明显差异。一般来说下降沿更尖锐,因为它是使用具有非常低内阻的晶体管实现的。而上升沿是由上拉电阻形成的,前面提到的低通滤波效果更加明显。

图 1 开漏输出产生的方波信号边沿

功耗和噪声干扰——在选择上拉电阻值时我们需要权衡。当线路上的设备驱动输出低电平时,它会导致较高的电流流过较低值的上拉电阻,这会增加功耗的问题。但是,选择较高值的电阻器会反过来导致流过电阻器的电流较低,这将使线路上的外部干扰(噪声)更容易影响信号状态。应该注意的是,在很多MCU中,配置为推挽的输出引脚在大多数情况下可以动态重新配置为输入,这是通过关闭两个晶体管来实现的,从而在线路上实现高阻抗状态。然后可以从其他外部设备采集输入信号。

-

推挽电路

+关注

关注

18文章

113浏览量

38157 -

推挽输出

+关注

关注

0文章

42浏览量

6546

发布评论请先 登录

相关推荐

功放电路电源设计注意事项

555电路调试技巧和注意事项

LMK时钟family LVDS输出交流耦合设计注意事项

PNP传感器输出信号的特点和工作方式

Buck电路中PCB layout布局设计和注意事项

恒流源电路的输出电流如何调节

推挽电路与图腾柱电路的区别

驱动电路输出模式的推挽与开漏输出

推挽输出电路工作原理以及注意事项(推拉输出电路)

推挽输出电路工作原理以及注意事项(推拉输出电路)

评论