1. 毛刺的产生原因:冒险和竞争

使用分立元件设计电路时,由于PCB在走线时,存在分布电容和电容,所以在几ns内毛刺被自然滤除,而在PLD内部没有分布电感和电容,所以在PLD/FPGA设计中,竞争和冒险问题比较重要。

信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。信号的高低电平转换也需要一定的过渡时间。由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为"毛刺"。如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在"冒险"。

可以概括的讲,只要输入信号同时变化,(经过内部走线)组合逻辑必将产生毛刺。将它们的输出直接连接到时钟输入端、清零或置位端口的设计方法是错误的,这可能会导致严重的后果。所以我们必须检查设计中所有时钟、清零和置位等对毛刺敏感的输入端口,确保输入不会含有任何毛刺。

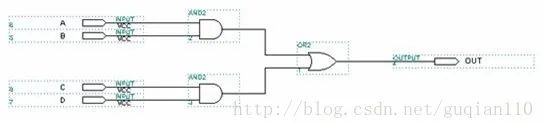

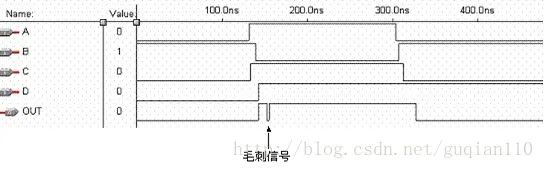

存在逻辑冒险的电路:

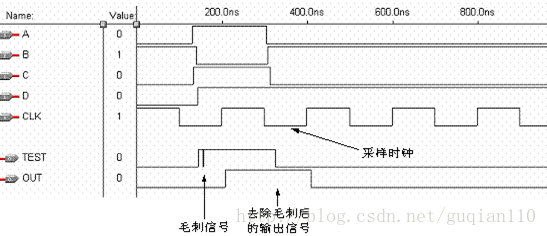

仿真波形:

2. 判断是否存在冒险

关于冒险的知识,数电书上有详细的说明,当时没有认真学,只了解个大概,现在又要重新看...还记得当年画卡诺图时的痛苦

冒险按照产生方式分为静态冒险&动态冒险两大类。静态冒险指输入有变化,而输出不应该变化时产生的窄脉冲;动态冒险指输入变化时,输出也应该变化时产生的冒险。动态冒险是由静态冒险引起的,所以,存在动态冒险的电路也存在静态冒险。

静态冒险根据产生条件不同,分为功能冒险和逻辑冒险两种。当有两个或两个以上的输入信号同时变化时,在输出端有毛刺,称为功能冒险;如果只有一个输入变量变化时,出现的冒险称为逻辑冒险。

因为动态冒险是由静态冒险引起的,所以消除了静态冒险,也就消除了动态冒险。功能冒险是由电路的逻辑功能产生的,只要输入信号不是按照循环码的方式变化,就会产生功能冒险,而且不能通过修改设计来消除,只能通过对输出进行采样来消除。判断逻辑冒险的步骤:

判断信号是否会同时变化

判断信号同时变化时,是否会发生冒险(代数法 or 卡诺图

3. 消除毛刺

我们可以通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

毛刺并不是对所有的输入都有危害,例如D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害,我们可以说D触发器的D输入端对毛刺不敏感。根据这个特性,我们应当在系统中尽可能采用同步电路,这是因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害。(由于毛刺很短,多为几纳秒,基本上都不可能满足数据的建立和保持时间)

以上方法可以大大减少毛刺,但它并不能完全消除毛刺,有时,我们必须手工修改电路来去除毛刺。一般有两种方法:

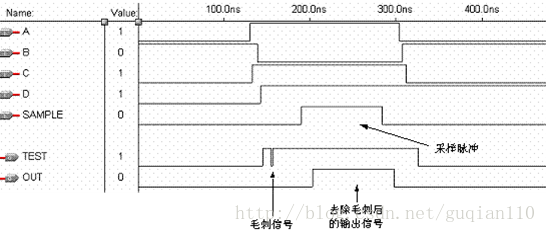

脉冲选择法

一般说来,冒险出现在信号发生电平转换的时刻,也就是说在输出信号的建立时间内会发生冒险,而在输出信号的保持时间内是不会有毛刺信号出现的。如果在输出信号的保持时间内对其进行"采样",就可以消除毛刺信号的影响。缺点是必须人为的保证sample信号必须在合适的时间中产生

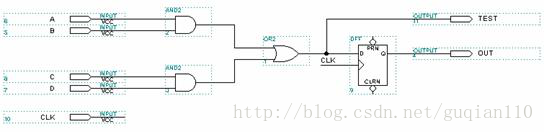

时序逻辑保持法

利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号,这种方法类似于将异步电路转化为同步电路。

4. 具体信号的讨论

1. 置位/复位信号

清除和置位信号要求象对待时钟那样小心地考虑它们,因为这些信号对毛刺也是非常敏感的。正如使用时钟那样,最好的清除和置位是从器件的引脚单直接地驱动。有一个主复位Reset引脚是常用的最好方法,主复位引脚给设计项目中每个触发器馈送清除或置位信号。几乎所有PLD器件都有专门的全局清零脚和全局置位。如果必须从器件内产生清除或置位信号,则要按照“门控时钟”的设计原则去建立这些信号,确保输入无毛刺。

2. 组合逻辑输出

当PLD输出引脚给出系统内其它部分的边沿敏感信号或电平敏感信号时,这些出信号必须象内部时钟、清除和置位信号一样小心地对待。只要可能就应在PLD输出端寄存那些对险象敏感的组合输出。如果你不能寄存险象敏感的输出,则应符合“门控时钟”中讨论的门控时钟的条件。决不能用多级逻辑驱动毛刺敏感的输出。

3. 异步输入信号

按照定义,异步输入不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。采用附加触发器同步使能信号的方法可保证不违反计数器的建立时间,从而解决可靠性的问题。

审核编辑 :李倩

-

FPGA

+关注

关注

1632文章

21816浏览量

607078 -

PLD

+关注

关注

6文章

230浏览量

59566 -

毛刺

+关注

关注

0文章

29浏览量

15695

原文标题:FPGA学习-关于毛刺

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速AD加上时钟后,输入信号会有一个两倍于时钟信号的毛刺产生是什么原因

用ADS1298做心电采集时,基线有毛刺是什么原因造成的?

MAX13487接了终端电阻120Ω时,下降沿有很长的毛刺,是什么原因导致的?

ADC08200采样速率高的情况下,波形出现毛刺的原因?

TPA3118D2输出产生毛刺噪声怎么解决?

用AD623做应变调理电路,正弦波动和高频毛刺产生的原因和避免的方法?

简述自激振荡产生的原因

纹波电压的产生原因及控制方法

交越失真产生的原因和消除方法

使用OPA549作为输出级,输出100mV就会出现下冲毛刺,是什么原因引起的?

SMT贴片加工产生焊接裂缝的原因是什么?

MOS管尖峰产生的原因

无铅锡膏焊接后,边缘有毛刺和玷污的原因有哪些?

毛刺的产生原因:冒险和竞争

毛刺的产生原因:冒险和竞争

评论