对于任何低功耗设计,设计人员都可以选择选择低功耗组件或关闭外围设备的电源。在考虑非易失性闪存的选择时,设计人员可以使用这两个相同的选项——从系统操作、功耗和可靠性的角度来看,每个选项都有其优点和缺点。但是,还有另一种可用的低功耗解决方案具有简化系统设计和提高可靠性的额外好处。

使用外部闪存的典型设计

尽管具有嵌入式闪存的微控制器 (MCU) 设备激增,并且它们可以在多种低功耗模式下运行,但出于扩展原因,越来越多的系统仍然需要外部闪存设备来补充片上闪存。无线 (OTA) 更新、数据记录、用户配置文件和其他应用程序都促成了这一点。

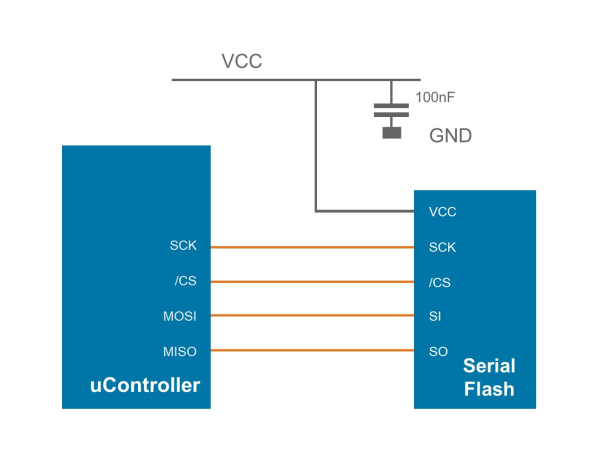

对于许多基本应用,图 1 所示的典型设计是可接受的解决方案。

图 1:使用外部闪存的典型设计

在该方案中,电源是持续提供给闪存设备的。当串行闪存芯片选择信号 ( /CS ) 未置位且存储器处于待机模式时,待机电流通常约为 ~10uA 至 ~20uA。还有一个选项可以进入命令驱动的深度掉电模式,该模式将待机功耗进一步降低到通常约为 2uA 至 ~5uA。

然而,在其他一些系统中,例如能量收集或小型电池供电设备,即使 2uA 也可能仍然代表过高的电流消耗值。而且,如果不经常使用闪光灯或很少使用闪光灯,则长时间待机 2uA 可能会过度消耗电源和能量储备,从而降低整体电池/系统的使用寿命。

具有简单电源开关控制电路的外置闪光灯

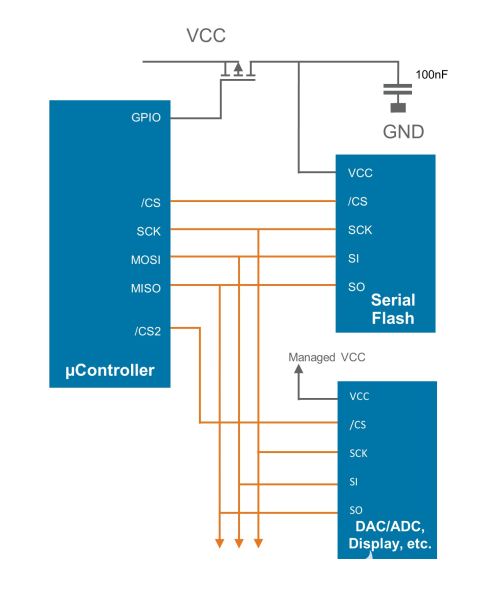

为了提高系统电池寿命,设计人员通常会实现一个简单的电源开关控制电路,如图 2 所示。闪存设备的电源通过一个备用 MCU GPIO 引脚在软件控制下进行管理,以便仅在需要时为串行闪存供电。

图2:串口闪光灯外接电源控制电路

不要太舒服!

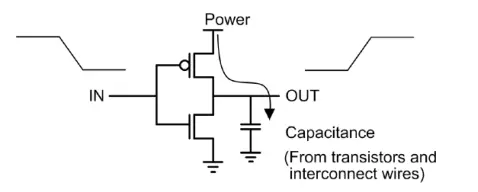

加入 MOSFET 完全关断串行存储器 VCC 会使存储器的待机功耗降低到零,但 MOSFET 本身有潜在的漏电流和漏电流,在某些情况下高达 1.5uA,仅好 500nA比正常待机时的内存高达 2uA。

可靠性问题

利用带有控制栅极的外部 FET 或 LDO 来管理外围设备 VCC 引脚的电源的解决方案正变得越来越普遍;但是,这也需要一个额外的 MCU GPIO 引脚。

更重要的是,当多个外围设备共享一个公共 SPI 总线并且各个设备已切换 VCC 引脚时,必须小心。

在图 2 所示的配置中,如果关闭 flash 的 VCC 并且 VCC = 0V,继续访问 SPI 总线上的其他 SPI 控制设备(例如 DAC/ADC/Display)将导致总线信号也出现在串行闪存 SPI 引脚。

在这种情况下,当闪存(或其他设备)的 VCC 为零时,外围 SPI 总线引脚上的高 VCC 将导致 I/O 保护二极管正向偏置,并且设备可能会通过 I/O 汲取电力自己别针。这可能会导致短期或长期的可靠性问题和操作问题。

对于任何其他可能在闪光灯关闭时通电的情况,杂散电容也应最小化,以使任何引脚上的电压不超过 VCC 引脚上的电压。或者,设计人员可以考虑更繁琐的解决方案,并为可以关闭 VCC 的串行存储器添加单独的 SPI 总线。仔细的硬件和软件设计和实施可以克服所有这些挑战和问题。然而…

超深度断电 (UDPD) 选项

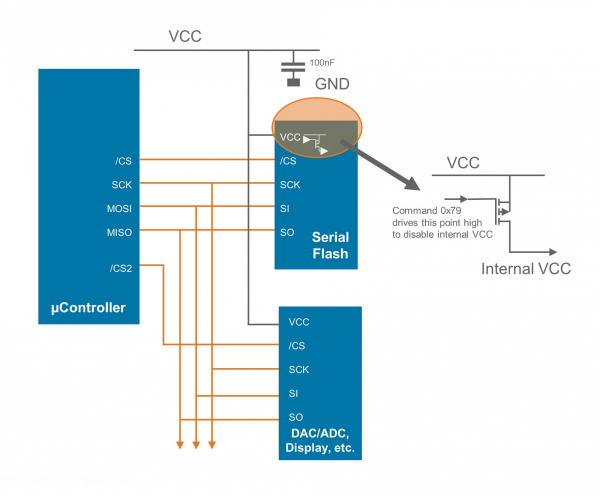

…通过将电源控制电路集成到存储设备本身并允许主设备 (MCU) 通过串行闪存 SPI 命令接口控制电源模式,可以实现更高效的解决方案。这样可以节省 GPIO 引脚用于其他用途。请参见图 3 中的图表。

该解决方案的好处是:

它比标准的深度掉电消耗更少的功率。

它不需要外部 MOSFET。

它允许设计人员将相同的 SPI 总线用于其他外设,从而简化设计。

它减轻了可靠性问题,因为 VCC 引脚始终连接到 VCC,并且电源由内部控制。

图 3:内部管理并通过 SPI 命令接口驱动的串行存储器电源控制

此解决方案的其他好处是:

它节省了一个用于切换外部 MOSFET 或 LDO 的 GPIO 引脚。

它简化了软件,因为它消除了多余的 MOSFET/LDO 控制程序。

它提供了更简洁的 PCB 设计并减少了 BoM。

除了待机和深度掉电模式外,Adesto Fusion、FusionHD™ (AT25XExxx) 和 DataFlash™ (AT45DBxxxE/F) 闪存器件还提供这种超深度掉电模式。待机和深度掉电模式导致的电流消耗与其他行业标准闪存设备相似或更低。

Ultra Deep Power Down 模式将 Fusion 的静态电流降至 200nA 以下,FusionHD 的静态电流降至 100nA,DataFlash 的静态电流降至 400nA 以下。

使用超深度掉电

实现 UDPD 模式很简单。我们在应用笔记 AN111中概述了详细说明。

结论

选择合适的低功耗存储器可能是能量收集或小型电池供电设备的关键系统设计因素。了解和管理 SPI 总线上组件的交互对于提高功能和可靠性也很重要。通过考虑如何在实际系统中实现存储器,Adesto 的串行闪存解决方案为设计人员提供了简化设计、降低风险、提高可靠性和节省外部组件的选项,从而大大简化了电路并降低了材料成本。

作者:Paul Hill ,Gordon MacNee

审核编辑:郭婷

-

存储器

+关注

关注

38文章

7484浏览量

163767 -

ldo

+关注

关注

35文章

1940浏览量

153311 -

电池

+关注

关注

84文章

10563浏览量

129482

发布评论请先 登录

相关推荐

MAX32675C超低功耗Arm® Cortex®-M4F MCU

物联网系统中TCP低功耗产品长连接状态下降低功耗功能的实现方案

栅极驱动芯片选型低功耗原因

利用超低功耗单片机 MSP430 作为系统伴随芯片应用报告

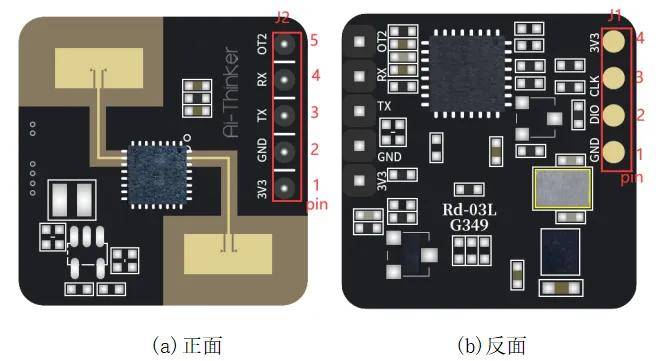

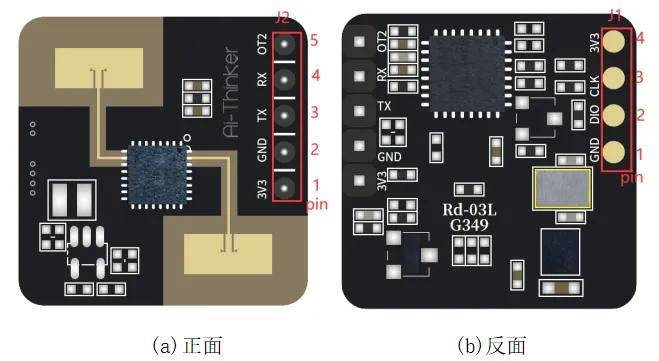

0.1mA!24GHz超低功耗人体存在毫米波雷达模组

适用于超低功耗和低功耗应用的独特高效隔离式DC/DC转换器

400nA超低功耗升压DC/DC转换器 大幅提升电池驱动时间

DA16600 超低功耗 Wi-Fi + 蓝牙低功耗模块开发套件数据手册

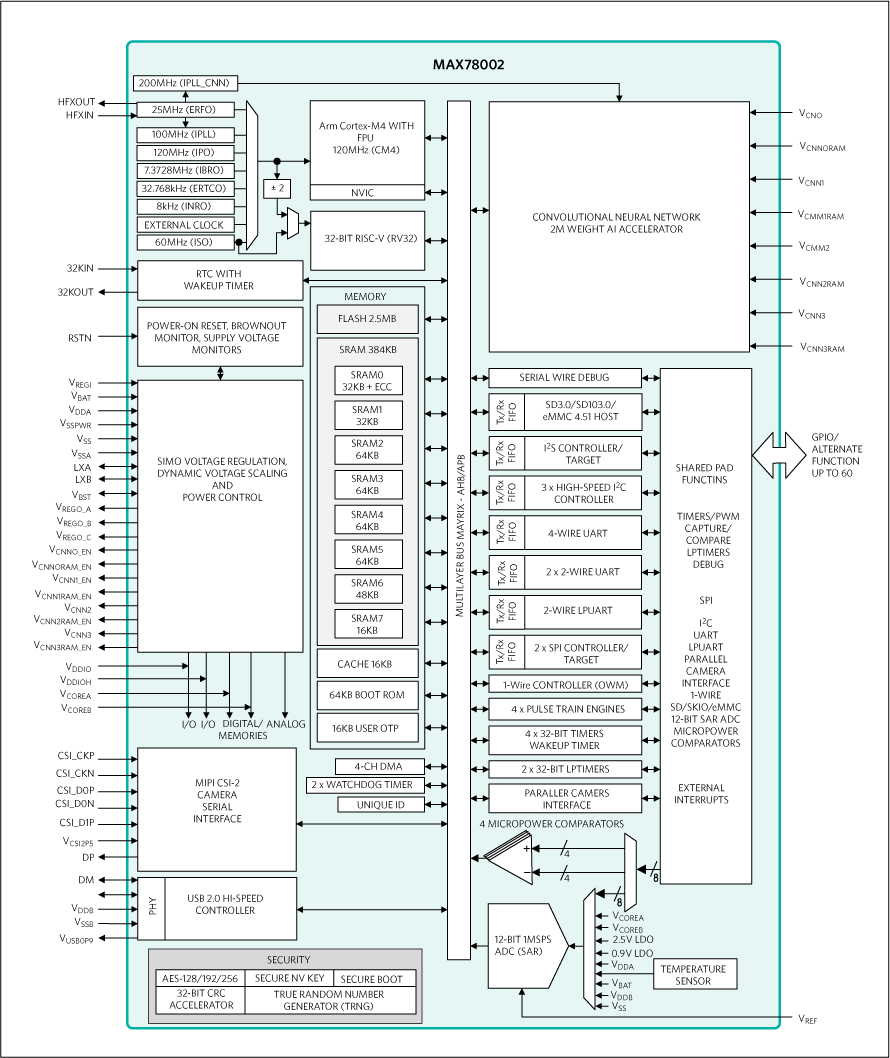

芯品#MAX78002 新型AI MCU,能够使神经网络以超低功耗运行

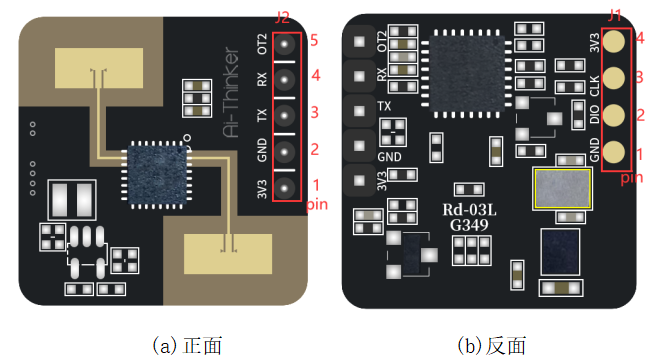

安信可Rd-03L检测使用—— 超低功耗实现人体存在检测,上位机配置快速上手

0.1毫安!超超超超超低功耗安信可雷达模组Rd-03L

在简化系统设计的同时实现超低功耗运行

在简化系统设计的同时实现超低功耗运行

评论