每隔几个月就会有更新换代的电子产品问世。它们通常更小、更智能,不仅拥有更快的运行速度与更多带宽,还更加节能,这一切都要归功于新一代先进的芯片和处理器。

跨入数字化时代,我们如同相信太阳明天一定会升起那样,确信新设备会不断地推陈出新。而在幕后,则是工程师们积极研究半导体技术路线图,以确保新设备所需的下一代芯片能够就绪。

很长一段时间以来,芯片的进步都是通过缩小晶体管的尺寸来实现的,这样就可以在一片晶圆上制造更多晶体管,从而使晶体管的数量在每12-24个月翻一番——这就是众所周知的“摩尔定律”。多年来,为了跟上时代的步伐,整个行业进行了诸多重大的创新,包括铜/低k互连、新型晶体管材料、多重图形化方案和三维(3D)架构。

开发3D结构的转变带来了新的挑战,随着深宽比的增加,挑战也在加剧。你可能已经想到,3D架构需要从器件设计上做根本性改变,需要新的材料、新的沉积和刻蚀方法来实现。在本文中,我们将带大家一起回顾半导体行业在实现3D架构过程中的重要里程碑。

准备阶段:平面工艺

创建集成电路最初是一个二维的问题:取一块平坦的硅片,在表面放置各种结构,用导线将它们连接起来。这是通过沉积一层层的材料,利用光刻技术对其进行图形化处理,并在暴露的区域刻蚀出必要的特征来完成的。这曾是电子工业的一个巨大突破。

随着技术需求的不断发展,需要在更紧凑的空间中构建更多的电路,以支持更小的结构。过去相对直接的过程变得越来越复杂。

随着创建2D结构的成本不断增加,以及在二维平面上进行微缩的可行方法逐渐枯竭,3D结构变得越来越有吸引力。半导体行业早在十多年前就开始开发早期的选择性刻蚀应用以支持3D技术,并不断扩展,从封装到非易失性存储器甚至晶体管本身。

晶体管走向3D

许多电子系统的主力都是晶体管。在过去,晶体管一直是扁平结构,其特性由晶体管通道的宽度和长度决定。晶体管性能由放置在通道上的栅极控制,不过这只能提供有限的控制,因为通道的另一边和底部不受控制。

从平面转向3D的第一步是为通道设计一个鳍,它可以由三面的栅极控制。不过,为了实现最优控制,需要接触到晶体管的所有四面,因而推动了全包围栅极(GAA)晶体管的发展。在GAA结构中,多根导线或多个薄片相互堆栈在一起,栅极材料完全包围着通道。

闪存提升

向3D的转变早在10年前就被应用于NAND闪存,当时内存位的水平字符串是向上堆栈的。

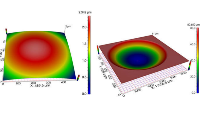

垂直结构由交替的薄层材料和尽可能多的工艺层堆栈而成。在构建这样的结构时,至少在两方面需要特别小心:第一,每一层都必须厚度均匀,并且非常平整,使每层中的位都与其他位具有相同的尺寸;第二,各层必须相互连接——这需要先建构一层堆栈并通过刻蚀在堆栈中进行钻孔,然后用适当的连接材料来填充这些孔,从而完成这样的结构。这其中,无论是刻蚀还是沉积工艺都极具挑战性,需要精确的执行。

这些挑战限制了堆栈的层数,因此需要采用新的方法来增加层数。

展望未来:3D DRAM

动态随机存取存储器(DRAM) 的物理机制与3D NAND完全不同,所用的方法也做了彻底的改变。

DRAM需要高容量的电容器,这对于在2D阵列中进行精确构建是一个挑战。垂直堆栈的难度更大,还需要更多研发以找到经济的方法来将电介质和活性硅堆栈在一起。光刻可能需要同时影响多层——目前还没有可量产的工艺。

3D封装越来越受欢迎

芯片经过封装后被放置在印制电路板(PCB)上。在过去,封装只是为了保护脆弱的硅芯片,并将其连接到电路板上。如今,封装通常包含多个芯片,随着缩小芯片占用空间的需求提升,封装也开始转向3D。

3D封装要求芯片被堆栈起来,这涉及到芯片之间的密集连接——这种连接可以提高信号速度,因为它们短得多,又可以同时传输更多信号。然而,在两个以上芯片的堆栈中,其中一些信号还需要通过传导通道连接到堆栈更高的芯片,这些通道被称为“硅通孔”(TSVs)。

3D芯片堆栈重要的终端市场应用一直在内存领域——高带宽内存 (HBM) 是最为常见的。内存芯片还可以被堆栈到CPU或其他逻辑芯片上,以加快从内存中获取数据的速度。

如今,3D是微缩的必要条件

在解决半导体制造中的所有微缩限制时,考虑3D已成为标准做法。虽然3D可能不是解决所有问题的选择,但它在上述应用中特别有用。

每一个新的应用都伴随着如何构建的难题,这需要创新的思维和硅工艺领域的持续发展,半导体制造设备就是芯片行业不断实现3D结构的主要推动者。

-

3D

+关注

关注

9文章

2894浏览量

107658 -

带宽

+关注

关注

3文章

940浏览量

40974 -

半导体行业

+关注

关注

9文章

403浏览量

40560

发布评论请先 登录

相关推荐

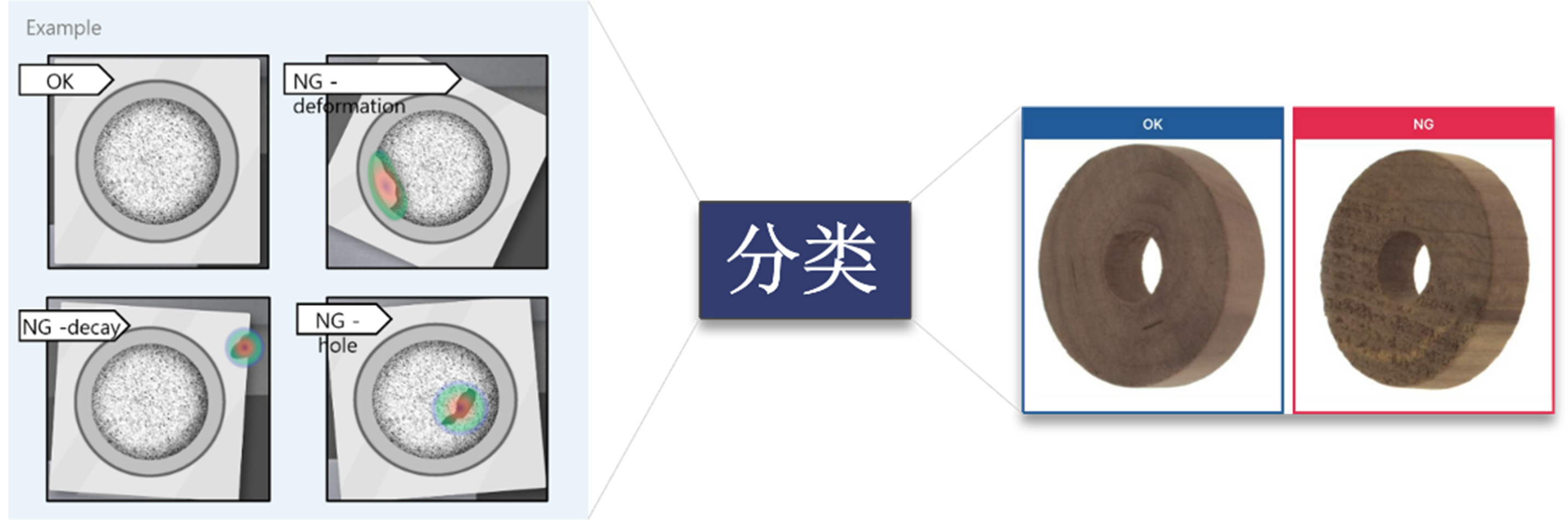

多维精密测量:半导体微型器件的2D&3D视觉方案

技术前沿:半导体先进封装从2D到3D的关键

技术资讯 | 2.5D 与 3D 封装

揭秘3D集成晶圆键合:半导体行业的未来之钥

物联网行业中的模具定制方案_3D打印技术分享

NEO推出3D X-AI芯片,AI性能飙升百倍

3D封装热设计:挑战与机遇并存

SK海力士五层堆叠的3D DRAM生产良率达到56.1%

安徽烁轩半导体开展车规级Micro LED驱动及3D封装技术研究

3D DRAM进入量产倒计时,3D DRAM开发路线图

光学3D表面轮廓仪&共聚焦显微镜:引领半导体行业走向新质生产力时代

光学3D表面轮廓仪&amp;共聚焦显微镜:引领半导体行业走向新质生产力时代

半导体行业如何实现3D架构过程

半导体行业如何实现3D架构过程

评论