瑞萨电子提供业内最广泛、最深入的芯片时序产品组合。除了我们广泛的缓冲器和时钟合成器产品选择外,我们还提供领先的系统时序解决方案,以解决几乎任何应用中的时序挑战。我们的产品组合在模拟和数字定时领域拥有超过 20 年久经考验的专业知识,在先进的定时技术中具有最低的相位噪声和最高的性能。

时序和时钟 IC 广泛用于网络、射频、物联网、电信、图像传感器、医疗甚至音频应用等应用。围绕时序IC设计外部电路时,一定要注意电源设计。就像我们不应该用廉价的汽油填充兰博基尼一样,我们也不应该用嘈杂的电源为我们的低噪声定时 IC 供电。

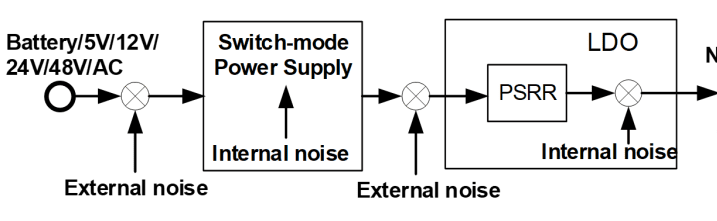

对于所有上述应用中使用的定时和时钟 IC,电源通常是电池,或 5V 到 AC 之间的任何电压总线。电源电压通常通过开关模式电源降压到适当的电平。在这里,一些外部辐射或传导噪声可能会耦合到系统中,并且电源可能会产生其自身的内部噪声,从而导致其输出电压承载宽频谱并生成不准确的时序/时钟信号。在不添加强滤波器或低噪声 LDO 的情况下,我们不应直接从此类噪声电源馈送任何对噪声敏感的时序或时钟 IC,如图 1 所示。由于尺寸原因,低噪声 LDO 始终优于大型滤波器优点,准确的输出电压和更好的动态负载响应。

图 1 为噪声敏感电路供电的典型电源图

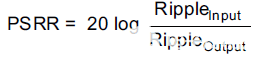

这种低噪声 LDO 通常具有非常高的 PSRR(电源抑制比)来阻挡传入噪声,并且它还具有非常低的自生噪声。PSRR 是特定频率下 LDO 输入电压纹波与输出电压纹波的比率,通常以对数形式表示:

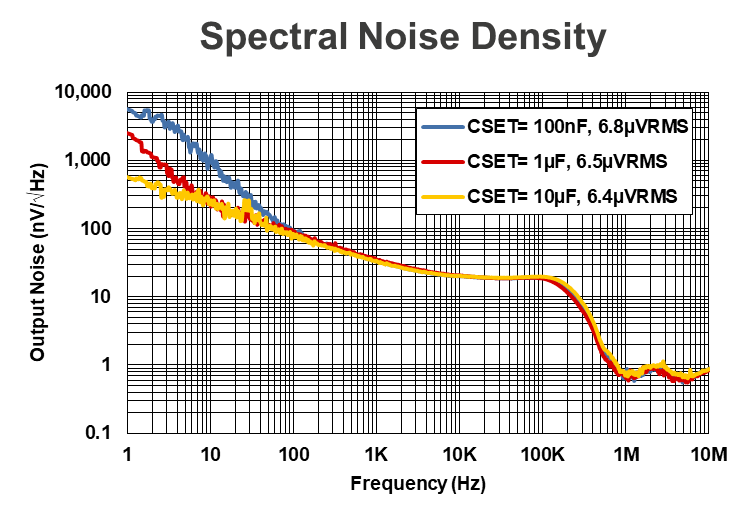

PSRR 通常随负载电流、裕量电压、输出电容以及外部噪声滤波电容和输出电压的不同而变化。高频 PSRR 可以通过外部电容器轻松改善。然而,对于低频滤波,电容可能会变得非常大且价格昂贵,因此选择在低频下具有非常高 PSRR 的 LDO 可能有助于减小电容尺寸。

图 2 显示了不同系统设置下的 PSRR 差异。根据图 2B,PSRR 在高频下随着输出电容器的增大而更高,并且 LDO 在低频下已经具有非常高的 PSRR。根据图 2D,如果需要在轻负载时更高的 PSRR,设计人员可以在带隙引脚上添加一个小型低成本电容器,这不仅可以改善 PSRR,还可以改善内部噪声。

图 2 PSRR 与其他系统设置

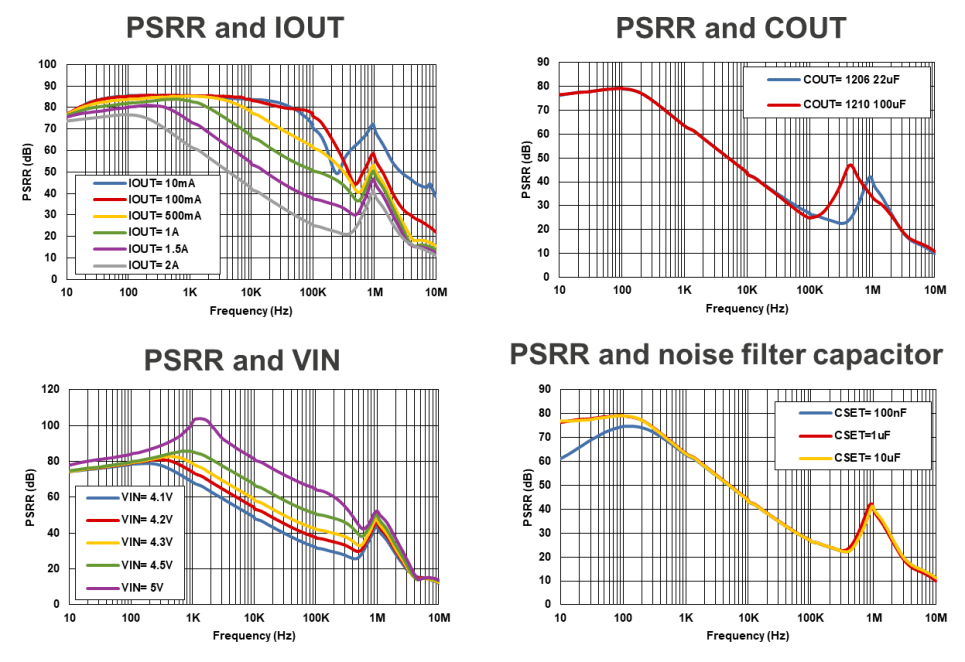

LDO 的另一个重要参数是内部噪声,它以两种方式表示。一个是频谱噪声密度,一条显示噪声与频率的曲线。在对频谱进行调节的射频等应用中,必须将噪声控制在“发射掩模”内才能通过认证测试。因此,用户应该检查感兴趣的频率周围的频谱噪声密度曲线。典型的频谱噪声图如图 3 所示。

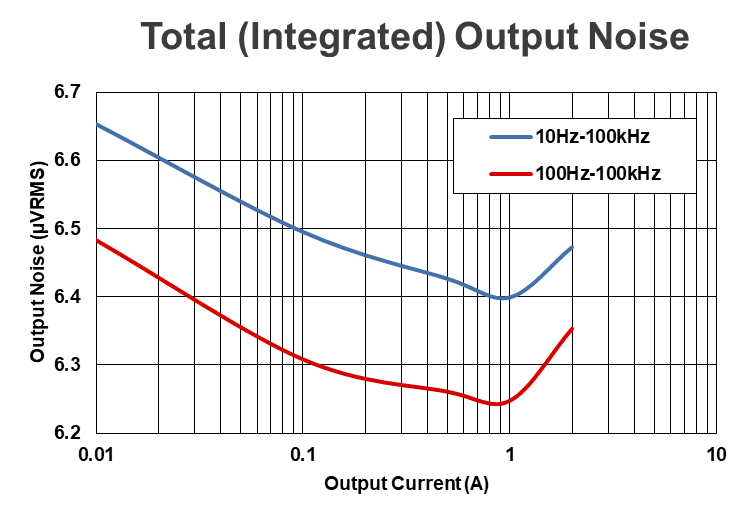

另一种是综合输出噪声,通常也称为输出噪声电压。它是在一定频率范围内积分的频谱噪声密度。在 ADC 或 DAC 等应用中,从 DC 到系统带宽的所有 LDO 噪声都被集成并作为整体计算,以影响 ADC/DAC 精度。因此,总输出噪声对于此类应用很重要,典型的图表如图 4 所示。图 3 和图 4 取自瑞萨电子性能卓越的低噪声 LDO。

图 3

图 4

瑞萨发布了两款额定输出为 5.5V 和 2A 的超低噪声 LDO RAA214020和RAA214023,它们现在完全有资格为瑞萨时序和时钟 IC 产品组合供电,并且包含在每个评估板的 BOM 中。下面显示了一些具有匹配时钟 IC 和 LDO 器件的示例。更多具有各种额定电流和性能的低噪声 LDO 即将推出。

审核编辑:郭婷

-

ldo

+关注

关注

35文章

1920浏览量

153199 -

adc

+关注

关注

98文章

6453浏览量

544160 -

dac

+关注

关注

43文章

2272浏览量

190859

发布评论请先 登录

相关推荐

LMK04208具有双环PLL的低噪声时钟抖动消除器数据表

CDCM9102低噪声双通道100MHz时钟发生器数据表

用于定时和时钟IC的低噪声电源

用于定时和时钟IC的低噪声电源

评论