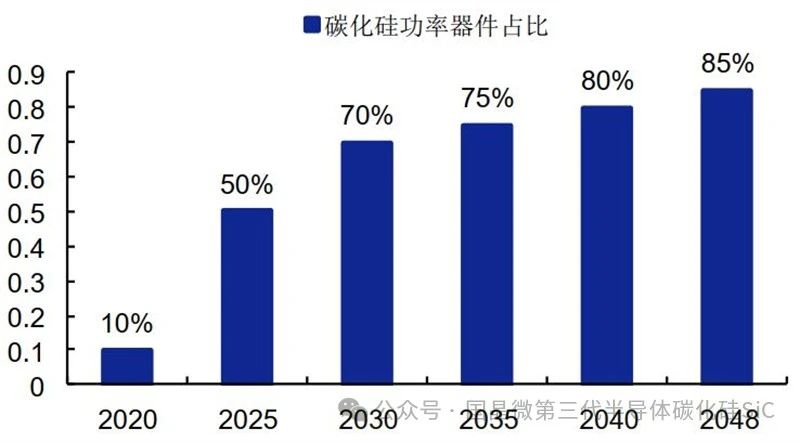

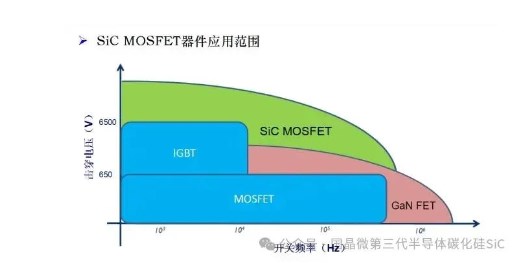

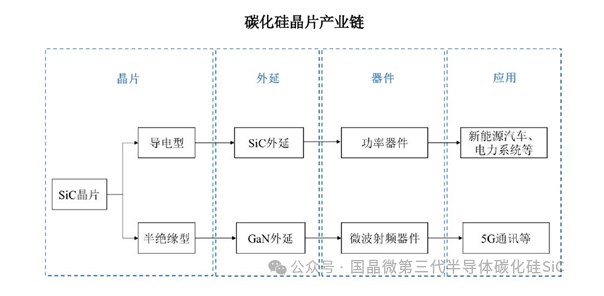

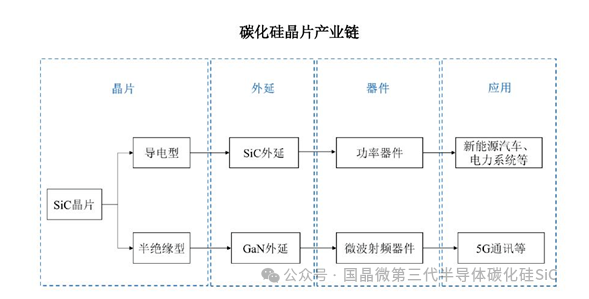

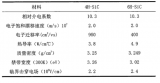

近几十年来,以新发展起来的第 3 代宽禁带功率半导体材料碳化硅(SiC)为基础的功率半导体器件,凭借其优异的性能备受人们关注。SiC与第1代半导体材料硅(Si)、锗(Ge)和第 2 代半导体材料砷化镓(GaAs)、磷化镓(GaP)、GaAsAl、GaAsP 等化合物相比,其禁带宽度更宽,耐高温特性更强,开关频率更高,损耗更低,稳定性更好,被广泛应用于替代硅基材料或硅基材料难以适应的应用场合。

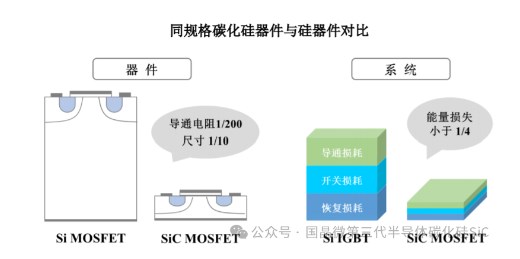

(1)禁带宽度更宽:SiC 的禁带宽度比 Si高 3倍以上,使其能耐受的击穿场强更高(临界击穿场强是Si基的 10倍以上),故器件能承受的峰值电压更高、能输出的功率更大。相同电压等级下,SiC功率半导体器件的漂移区可以做得更薄,可使整体功率模块的尺寸更小,极大地提高了整个功率模块的功率密度。另外,导通电阻Ron与击穿场强的三次方成反比例关系,耐击穿场强的能力高,导通电阻小,减小了器件开关过程中的导通损耗,提升了功率模块的效率。

(2)耐温更高:可以广泛地应用于温度超过600 ℃的高温工况下,而 Si 基器件在 600 ℃左右时,由于超过其耐热能力而失去阻断作用。碳化硅极大提高了功率器件的耐高温特性。

(3)热导率更高:SiC 器件的热导率比 Si高 3 倍以上,高导热率提升了器件和功率模块的散热能力,减低了对散热系统的要求,有利于提高功率模块的功率密度。

(4)载流子饱和速率更高:SiC 与 Si 相比,其载流子饱和速率要高 10 倍以上,而 SiC 器件的开关频率是Si基IGBT的5~10倍,增强了器件的高频能力。SiC 器件不仅导通电阻 Ron小,而且开关过程损耗也低,提升了功率模块的高频性能。

(5)临界位移能力更高:不仅SiC的临界位移能力比Si高2倍以上,而且SiC器件对辐射的稳定性比Si 基高 10~100 倍,SiC 基器件具备更高的抗电磁冲击和抗辐射破坏的能力。适合用于制作耐高温抗辐射的大功率微波器件。

然而,现有的封装技术大多都是沿用 Si基器件的类似封装,要充分发挥碳化硅的以上性能还有诸多关键问题亟待解决。

由于 SiC器件的高频特性,结电容小,栅极电荷低,开关速度快,开关过程中的电压和电流的变化率极大,寄生电感在极大的 di/dt 下,极易产生电压过冲和振荡现象,造成器件电压应力、损耗的增加和电磁干扰问题。

关于在高温、严寒等极端条件下可靠性急剧下降等问题,急需寻求适应不同工况的连接材料和封装工艺,加入三代半交流群,加VX:tuoke08,满足不同封装形式的热特性要求。

针对模块内部互扰、多面散热、大容量串并联、制造成本和难度等问题,适当减少热界面层数,缩减模块体积,提升功率密度和多功能集成是未来的趋势。

采用先进散热技术、加压烧结工艺,设计功率半导体芯片一体化,优化多芯片布局等方式,起着一定的关键作用。

针对上述问题,国内外专家及其团队研发不同封装技术,用于提升模块性能,降低杂散参数,增强高温可靠性。

美国 Wolfspeed 公司研发出结温超过 225 ℃的高温 SiC 功率模块,并将功率模块的寄生电感降低到5 nH。美国GE公司的全球研究中心设计了一种叠层母线结构,构造与模块重叠并联的传导路径,使回路电感降至4. 5 nH。德国赛米控公司采用纳米银烧结和 SKiN 布线技术,研发出 SiC 功率模块的高温、低感封装方法。德国英飞凌公司采用压接连 接 技 术 ,研 制 出 高 压 SiC 功 率 模 块。德 国Fraunholfer 研究所采用 3D 集成技术研制出高温(200 ℃)、低感(≤1 nH)SiC 功率模块。瑞士 ABB公司采用 3D 封装布局,研制出大功率低感 SiC 功率模块。瑞士 ETH 采用紧凑化设计,优化功率回路,研制出寄生电感≤1 nH 的低电感 SiC 功率模块。日本尼桑公司基于双层直接敷铜板(direct bonded copper,DBC)封装,研制出低感 SiC 功率模块,应用于车用电机控制器。

上述碳化硅的优良特性,只有通过模块封装布局的可靠性设计、封装材料的选型、参数的优化、信号的高效和封装工艺的改善,才能得以充分发挥。

本文中重点聚焦典型封装结构下,低杂散参数、双面散热模块下缓冲层的影响和功率模块失效机理等关键技术内容的梳理总结,最后展望了未来加压烧结封装技术和材料的发展。

1 模块封装形式

随着新兴战略产业的发展对第 3代宽禁带功率半导体碳化硅材料和芯片的应用需求,国内外模块封装技术也得到迅速发展,追求低杂散参数、小尺寸的封装技术成为封装的密切关注点,国内外科研团队和半导体产业设计了结构各异的高性能功率模块,提升了SiC基控制器的性能。

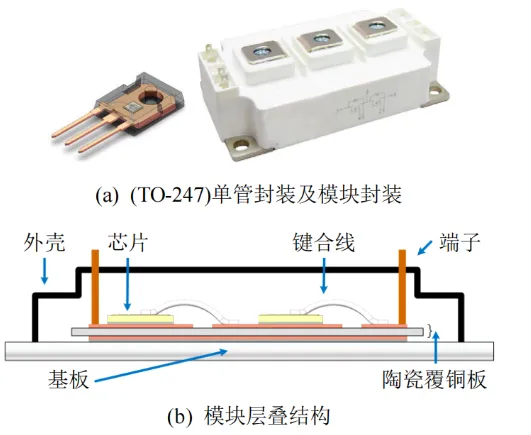

(1)传统封装:Wolfspeed、Rohm 和 Semikron 等制造商大多延用传统Si基封装方式,功率等级较低,含有金属键合线,杂散电感较大。

(2)DBC+PCB 混合封装:Cha 等和 Seal 等把 DBC和 PCB板进行整合,通过键合线连接芯片和PCB板,研创出DBC+PCB混合封装。实现了直接在PCB 层间控制换流回路,缩减换流路径来减小寄生电感。

(3)SKiN 封装:德国 Semikron 公司采用纳米银烧结和SKiN布线技术,采用柔性 PCB板取代键合线实现芯片的上下表面电气连接,模块内部回路寄生电感仅为1. 5 nH。

(4)平面互连封装:通过消除金属键合线,将电流回路从 DBC 板平面布局拓展到芯片上下平面的层间布局,显著减小了回路面积,降低了杂散电感参数,如 Silicon Power 公司采用端子直连(DLB)、IR的Cu-Clip IGBT和Siemens的SiPLIT技术等。

(5)双面焊接(烧结)封装:在功率芯片两侧焊接 DBC 散热基板,为芯片上下表面提供散热通道;或者使用银烧结技术将芯片一面焊接 DBC,另一面连接铝片。双面散热既能优化基板边缘场强,还能够降低电磁干扰(EMI),减小桥臂中点的对地寄生电容,使其具有损耗低、热性能好、制造成本低等优点。橡树岭实验室、中车时代电气、天津大学和CPES等可以将寄生电感降低至5 nH。同时,铜烧结作为一种更低成本的芯片连接方案更被视为是未来几年的研究热点。目前双面散热技术主要应用在新能源电动车内部模块。

(6)压接封装:压接型器件各层组件界面间依靠压力接触实现电热传导,分为凸台式和弹簧式两类。与焊接型器件相比,压接封装结构模块具有高功率密度、双面散热、低通态损耗、抗冲击能力强、耐失效短路和易于串联等优点,而且采用数量较少的压接型模块便可满足换流时电压等级和容量需求,但由于密封等要求多采用 LTCC 陶瓷设计,成本较高,且压接封装结构复杂,目前只用于高压模块的制造,具有一定的应用市场。但离汽车领域的实际应用尚有一定的差距。

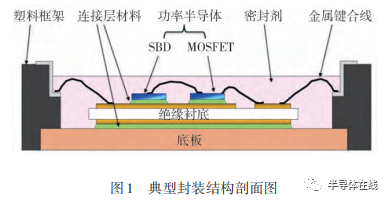

(7)三维(3D)封装:Tokuyama等和Herbsommer等将SiC模块的上桥臂直接叠加在下桥臂上,由于SiC 模块的结构是垂直型的,可以大幅缩短换流回路的物理长度,以进一步减少与 di/dt 相关的问题。 目前该封装技术最大的优势是可以将模块寄生电感降至 1 nH 以下。还有将电压波动最大的端子放置在三维夹心结构的中间,使端子与散热器之间的寄 生 电 容 急 剧 降 低,进 而 抑 制 了 电 磁 干 扰噪声。 功率模块的典型封装结构剖面图如图1所示。

2 低杂散电感封装技术

目前,引线键合分为线材和带材两类,根据金属特性不同,主要有 Al、Cu和 Au。铝线是最基本的键合方式,铝带通流能力更强,强度更高,Au由于其成本较高,应用相对较少,铜带是未来的趋势。其中柔性箔、铝涂层铜线和顶部DBC-铜夹技术也具有一定的应用市场。

对于金属引线键合式模块的 3 维封装结构,通过降维处理,可以极大简化功率模块结构的仿真时间,将三维立体结构转换为2D平面结构的研究为整体功率模块的研究应用奠定了基础,如图2所示。

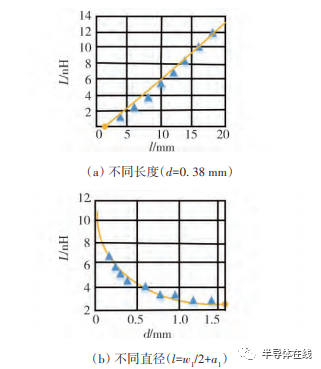

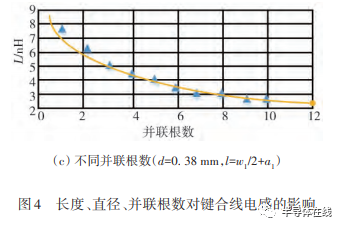

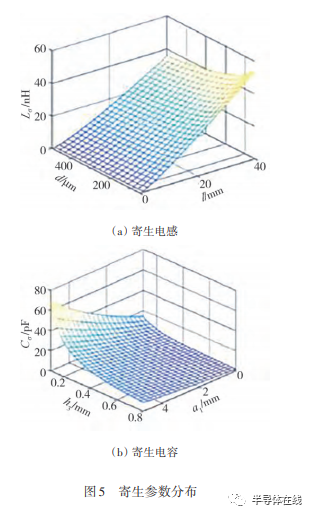

本文中采用 ANSYS Q3D 仿真软件进行模型寄生参数提取,以单条金属键合线的长度l和直径d作为待优化参数,仿真分析l和d对寄生电感的影响特性,如图3所示。

各层的厚度 h1-h7和边距 a1-a3为优化参数,其中,a3是DBC结构上层铜距离陶瓷层边沿的距离,因为绝缘性能、DBC小坑和阻焊等工艺的需求,a3普遍等于1 mm。传统典型2维封装结构模块各层宽度w和厚度h的具体尺寸如表1所示。对于金属引线键合式焊接的封装结构,寄生电感主要来自于键合线,其寄生电感可近似表示为

式中:l为键合线长度,l= w1/2+a1;μ0 = 4 ×10-7,是真空磁导率;d为铝键合线的直径。

参照文献[30]对键合线进行仿真,结果如图 4所示。经验证与式(1)的数据拟合结果基本一致。

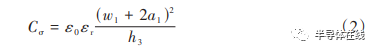

曾正等的研究表明,芯片功率回路的寄生电容主要由DBC陶瓷层的寄生电容决定,可表示为

式中:ε0 = 8.85 × 10-12F/m,表示真空介电常数;εr =9,表示 Al2O3陶瓷相对介电常数,对于陶瓷 AIN和陶瓷Si3N4,相对介电常数分别等于8. 8和6. 7。

寄生参数分布仿真结果如图 5 所示,经验证与式(1)和式(2)的数据拟合结果基本一致。

由图 4 和图 5 还可明显看出各个关键变量对寄生参数的影响规律。键合线长度越短、直径越大,寄生电感越小,其中键合线长度对寄生电感影响更显著;陶瓷层越厚、面积越小,寄生电容越小,其中陶瓷层厚度对寄生电容影响更显著。

降低开关器件换流回路中电流流通路径所通过的面积,可以减小杂散电感,将上半桥 SiC MOSFET的续流二极管和下半桥的 SiC MOSFET 进行位置互换,减小换流路径的导通面积,可降低杂散电感,如图6所示,其仿真结果如图7所示。

将功率模块的封装模型导入杂散参数提取软件ANSYS. Q3D,依次采取网络剖分、工况定义的步骤,设置激励源(Source)和接地(Sink),并且分别把激励源添加到功率模块端子的表面,注意激励源可以设置多个,但是接地只能一个,图 8 是 SiC 模型的网格剖分图。

牛利刚等研究表明,利用ANSYS. Q3D提取半桥功率模块的寄生电感为20. 6 nH,实际检测结果是21. 23 nH,相差为 0. 63 nH,即相对误差为 3%,证明了叠层功率模块杂散电感的仿真提取方法的准确性。

金属键合线的寄生电感越小,寄生振荡越轻微,开关关断过程中的电压冲击越小,开关速率越高,开关损耗越小;与此同时,键合线的寄生电容也应尽可能小,以抑制电磁干扰的影响。

Lσ 和 Cσ 共同决定电磁干扰(EMI)噪声的转折频率fr:

3 双面散热技术

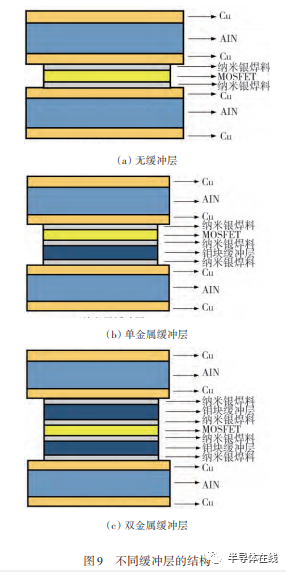

双面散热的功率模块封装结构可以通过取消金属键合线,增加缓冲层并对缓冲层的形状、材料、尺寸的优化,可减小杂散电感,增加散热途径,降低功率模块中芯片所承受的长时间高温危害,提高模块的使用寿命。

根据双面散热结构缓冲层的数量,分为无缓冲层、单层缓冲层、双缓冲层 3种,如图 9所示,其中无缓冲层和双层缓冲层均为对称结构。缓冲层可有不同形式,其中有的采用金属垫块。文献[33]中研究了芯片发热状态下3种模块所受最高结温和金属垫块结构所承受的热应力分布情况。

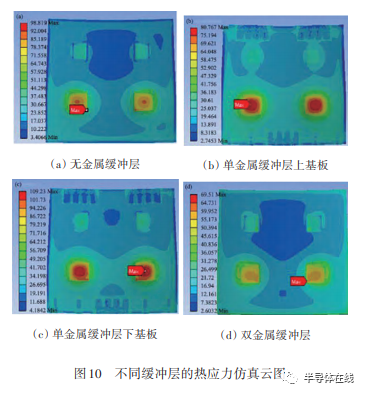

杨宁等的研究发现,不同金属构造的各部分热应力值如表 2所示,而对应的仿真云图如图 10所示。其中单层金属缓冲层因结构的不对称性,对其上下应力层需要单独分析。

从仿真云图中不难看出:无金属垫块缓冲层的双面散热结构的最大等效热应力为 99 MPa;单层金属垫块缓冲层的双面散热结构的上基板最大等效热应力是109MPa,下基板最大等效热应力是70 MPa,上下基板的最大等效应力结果相差较大,主要与芯片和金属层的热膨胀系数、温度差异有关;双金属层垫块缓冲层的最大等效热应力为81 MPa。

陆国权等研究表明,随着钼块厚度的增加,应力 缓 冲 效 果 明 显 ,应 变 减 小 。双 面 互 连 的 SiCMOSFET芯片最大von Mises应力和纳米银互连层的最大塑性应变均减小。同时,在缓冲层和上基板间烧结银互连层中增加 1 mm 银垫片可进一步降低双面互连结构的芯片应力和互连层应变,提高双面散热SiC模块的热机械可靠性。

与方形缓冲层对比,圆柱形缓冲层可有效消除芯片和纳米银互连层应力集中效应,大幅降低 SiC芯片所承受的最大 von Mises 应力和烧结银互连层的最大塑性应变。采用圆柱形缓冲层时,纳米银层塑性应变比采用方形缓冲层时的纳米银层的塑性应变值减少了47. 5%。这主要是因为圆柱形缓冲层边缘过渡圆润,应力分布更均匀,而方形缓冲层的边缘或尖角易造成芯片和烧结银互连层出现应力集中,造成局部热应力剧增。

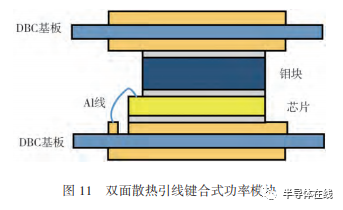

双面散热引线键合式功率模块如图 11 所示。Nakatsu等研究表明,双面散热功率模块的热阻值比引线键合功率模块约小50%;另外,它还具有优异的电学性能。

Liang等研究表明,双面散热功率模块的开关损耗降低到商业功率模块的 10%,由于键合引线会使寄生参数数值较大,所以无键合线模块,寄生参数数值大幅减小,SiC 芯片的耐高温、高频特性优势得到极大发挥。

模块封装中的材料都具有一定的临界热应力点,超过这一数值,就会出现断裂失效的危险。SiC功率模块的衬底尺寸主要取决于芯片的面积大小,绝缘衬底常规厚度在0. 03 mm,翘曲率在3 mil/in,陶瓷材料用作绝缘衬底采用直接覆铜技术。金属层边缘采用台阶状可有效减小应力,台阶高度应为铜层的一半。

基板主要趋势是使用高性能材料,减少层数和界面的数量,同时保持电、热和机械特性。绝缘金属基板(IMS)和IMB基板仅用于中低功率模块,如EV/HEV等。主流材料正逐渐从直接覆铜(DBC)转向活性金属钎焊(AMB),并采用高性能基材。双面冷却结构将促进在模块的顶部使用第2个陶瓷基板/引线框架。

直接冷却的基板,如销鳍基板,减少热界面的数量,避免使用热界面材料(TIM)。基板和冷却系统的集成以及冷却模块设计的部署和减少热接口数量将是一个强大的趋势,为未来几年提供新的解决方案。封装技术还需要具备高温可靠性的陶瓷基板和金属底板等相应套件。

目前能适应碳化硅设备更高运行温度的硅胶和环氧材料正在研发中。为了实现复杂和紧凑的模块设计,在包括EV/HEV等许多应用中,硅胶由于其低廉的价格,使用范围更广泛。环氧树脂材料的应用,仍受到高温下可靠性的限制

4 失效方式汇总

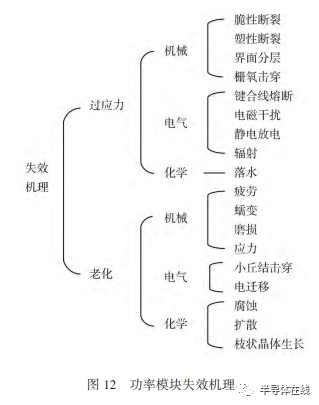

功率模块的失效机理主要集中在电气、温度、材料、化学等各个方面,如图12所示。

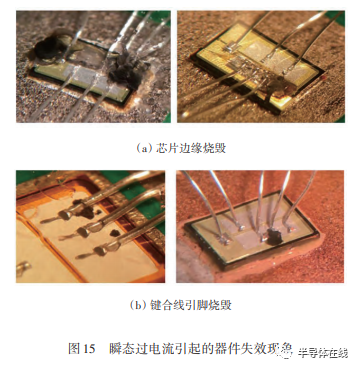

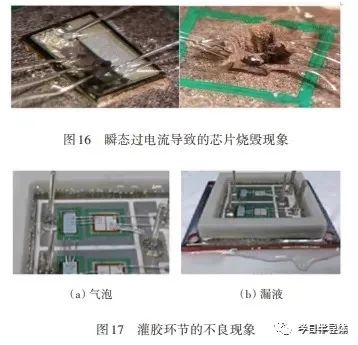

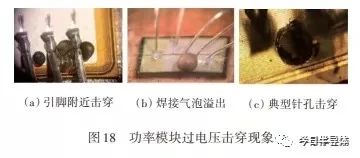

功率模块常见的损坏有过流损坏、过热损坏和过压损坏等,过流损坏为流经功率模块的电流超过耐流值,过流冲击导致芯片发热严重,超过结温耐温值,从而损坏芯片。过压损坏为加在SiC MOSFET的漏极(G)和源极(S)间电压 UGS大于耐压值,使得器件极间击穿损坏。

保障功率模块的安全运行,不仅要考虑功率模块电流电压的可承受范围,还须考虑驱动信号添加后,避免导通电路出现短路问题和上下桥臂直通等故障。因此,可以通过增加检测保护电路和对控制程序进行优化来保障功率模块的安全运行。

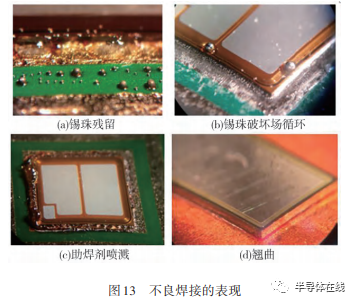

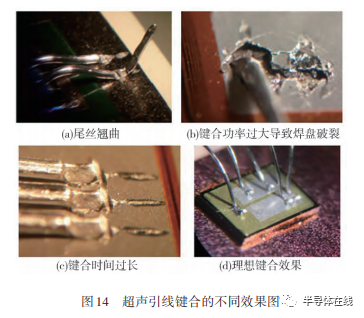

各种原因导致的功率模块的真实失效现象如图13~图19所示。其中功率模块里的续流二极管发生短路和集电极-发射极击穿烧断等是常见的失效现象。

对功率模块通过均匀涂抹导热硅脂作为热界面材料(TIM)已经不能满足要求,采用金属烧结等方法是下一步的研究方向,另外增加散热器、风扇和温度传感器等可有效防止过热问题。增加电流互感器检测器件与 RC 缓冲电路和对程序驱动算法进行优化等措施可有效解决过流问题。通过母线电压采集,进行对比保护等可有效解决过压问题。

5 先进技术展望

基于焊接与引线键合的传统材料工艺存在熔点低、高温蠕变失效、引线缠绕、寄生参数等无法解决的问题,新型互连材料正从焊接向压接、烧结技术发展。

与焊接式功率模块相比,压接式模块的优势具体有以下几点。

(1)焊接通过引线连接芯片和 PCB 板,在多次功率循环后容易老化脱落,造成模块失效。而且,焊接层空洞增加热阻,降低可靠性。压接借助压力将芯片压在基板上,电流从铜板直接流过,提高可靠性。

(2)传统焊接式多为单面散热,而压接式多为双面散热,可提升散热性能,有利于器件性能的充分发挥。

(3)键合线和焊接层引入杂散参数,高频特性下,电压和电流易产生较大波动,影响芯片串联特性。

考虑到纳米银焊膏具有高导电率、高导热性和优良的延展性,且熔点显著高于传统焊料,相关科研团队利用纳米银焊膏将芯片和集电极钼层烧结在一起,成功开发出银烧结压接封装器件,显示出其在压接型功率模块的封装应用中具有一定优势。

银烧结封装可以降低压接型器件的导通电压和通态损耗,减缓芯片与发射极钼层间的接触磨损,提升器件使用寿命。

目前烧结封装技术在发展中仍然存在着不能忽略的问题,同时也提出如下一些可行性方案。

(1)由于银和 SiC 芯片背面材料热膨胀系数不同引起的问题,可通过添加金属缓冲层来改善互连性能,但会增加功率模块封装工艺的复杂性和成本。采用满足性能指标和可靠性的烧结层代替缓冲层,成为研发的可行性方案。

(2)银层的电迁移现象,不利于功率电子器件长期可靠应用。铜烧结既能满足减少电迁移现象,又能够降低成本,使其成为高温模具连接材料的一种很有前途的替代品。

(3)优化烧结工业,创新烧结方案,缩减预热、烧结时长,提升生产效率;流水线工作,提升可制造性和生产设计的灵活性。

(4)与无压烧结相比,低压烧结可靠度和散热性能较好。虽然部分厂商已解决压力问题,但是烧结过程中的致密性、连接层的温控和极限环境中性能退化问题还尚待解决。

上述问题的解决需要产业链上下游的联动协调攻关,部分问题随着技术进步将逐步得到解决。尽管当前模块封装几乎全是以连线键合方式为主,预计未来3~5年银烧结封装技术会是功率模块互连的主流技术。由于银离子迁移对互联结构有负面影响,加之成本和热应力适配需求,与银烧结技术类似的瞬时液相烧结(TLPS)、银铜烧结、铜烧结技术和相应的焊浆材料也在快速发展,部分技术瓶颈有望在近几年突破。芯片贴装、基板连接、模块与散热器的连接等都是烧结技术潜在的应用范围。

6 结论

本文重点分析和综述了碳化硅功率模块封装中的 4 个关键问题:

(1)总结归纳了结构各异的低杂散参数模块封装形式,列举阐述各模块性能优势;(2)聚焦典型封装结构下,分析概括键合式功率模块的金属键合线长度、宽度和并联根数对寄生电感影响,直接覆铜(DBC)陶瓷基板中陶瓷层的面积、高度对寄生电容的影响,以及采用叠层换流技术优化寄生参数等成果;(3)在封装模块散热方面,综述了双面散热结构的缓冲层厚度和形状对散热和应力形变的影响;(4)汇总了功率模块常见失效图谱和解决措施,为模块的安全使用提供参考。最后探讨了先进烧结银技术的需求和关键问题,并展望了烧结封装技术和材料发展方向。

审核编辑 :李倩

-

封装

+关注

关注

126文章

7894浏览量

142942 -

功率密度

+关注

关注

0文章

90浏览量

16896 -

碳化硅

+关注

关注

25文章

2759浏览量

49044

原文标题:SiC功率模块封装技术及展望!

文章出处:【微信号:today_semicon,微信公众号:今日半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

碳化硅功率器件在能源转换中的应用

碳化硅功率器件的优势和应用领域

碳化硅压敏电阻 - 氧化锌 MOV

碳化硅功率器件封装的关键技术

碳化硅功率模块封装中的4个关键问题

碳化硅功率模块封装中的4个关键问题

评论