最近由于项目需要,要将bit文件固化到zedboard的flash中,使程序上电自启,断电不丢失。

我们知道,一般板级调试的时候都是直接下载bit流到FPGA就行,固化到Flash的话,也是先生成.mcs文件,然后下载到Flash即可。

但是在经过反复尝试之后,发现对zynq系列好像行不通。

why?这得从zynq的启动流程说起。

一、ZYNQ的启动流程

ZYNQ7000 SOC 芯片可以从 FLASH 启动,也可以从 SD 卡里启动, 本节介绍程序 FLASH 启动的方法。Zynq7000 SOC 芯片上电后,最先运行的是ARM端系统(PS)。然后再通过ARM系统软件部分加载FPGA的比特流文件.bit至FPGA(PL),配置FPGA PL端的逻辑功能。ZYNQ 系统的启劢流程如下:

ZYNQ启动分为两个阶段

经过以上两个阶段,PL端配置程序及应用程序才开始运行。

1.1 第一阶段 (BOOT ROM)

-

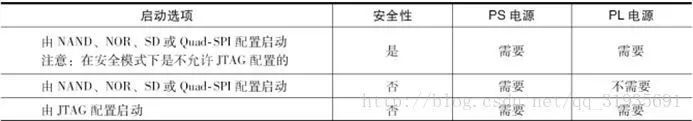

上电后,Zynq7000 SOC 会首先执行片内 Boot ROM 代码,Boot ROM 代码读取 Boot mode 寄存器来判断是哪一种启动方式(SD card/QSPI Flash/JTAG)。

-

确定好哪种启劢方式后,Boot ROM 从相应的启动设备(SD Card/QSPI Flash)加载 First Stage Bootloader (FSBL) 到On Chip Memory(OCM) RAM,并且将执行权交付给 FSBL。

1.2 第二阶段 FSBL (First Stage Bootloader)

使用SDK 工具一步步生成 FSBL 代码和可执行文件,结合代码可知 FSBL 主要做了如下工作:

-

初始化 CPU,初始化串口;

-

禁止 L1 Data Cache;

-

注册 ARM 中断向量;

-

通过 Boot mode 寄存器,判断是哪种启动方式。

1.2.1 QSPI Flash 启动方式:

-

初始化 QSPI Flash 控刢器;

-

从 Flash 拷贝 system.bit 到 FPGA (如果 Flash 中存有 system.bit);

-

从 QSPI Flash 拷贝应用程序的代码到DDR3;

-

调转到应用程序执行;

1.2.2 SD Card 启动方式:

-

初始化 SD 控刢器;

-

从 SD Card 拷贝 system.bit 到 FPGA (如果 BOOT.BIN 中存有 system.bit);

-

从 SD card 拷贝应用程序的代码到 DDR3;

-

跳转到应用程序执行;

1.2.3 JTAG 启动方式,直接退出。

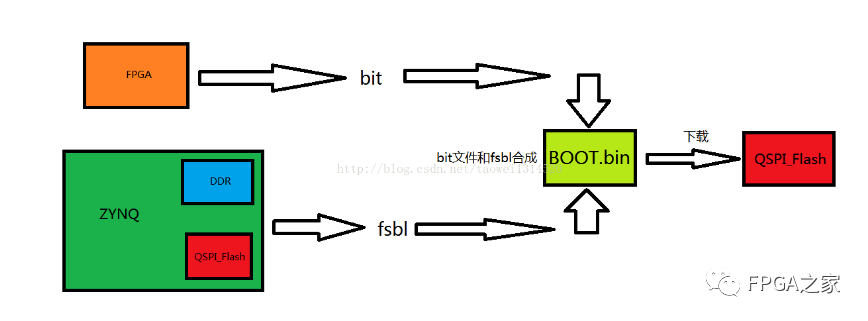

因此,对于Zynq系列的FPGA芯片来说,固化到Flash中的bit文件需要一个引导程序(也就是FSBL),才能被用来配置PL。实际上,FSBL会作为BootLoader和bit文件一起合成一个.bin或者.mcs文件,然后下载到Flash中,过程如下:

二、生成BOOT.bin或者BOOT.mcs

2.1 VIVADO操作

你应该已经有了一个完整的工程,接下来你需要添加并配置PS端,生成新的bit文件:

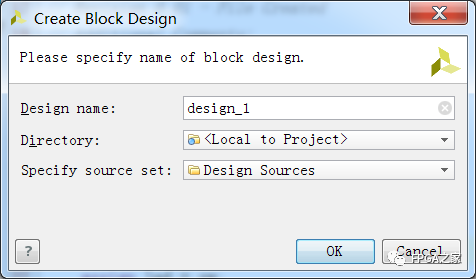

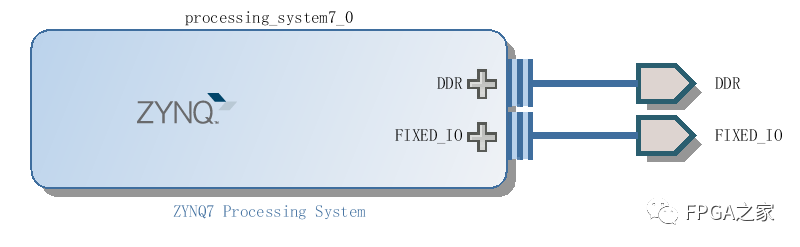

(1)建立一个新的块设计(Create Block Design)

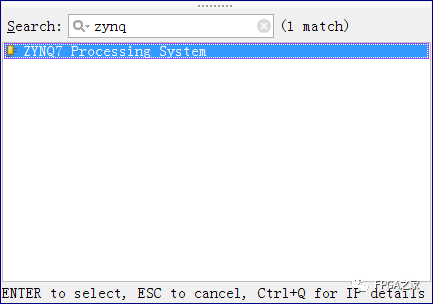

(2)添加ZYNQ7 Processing System

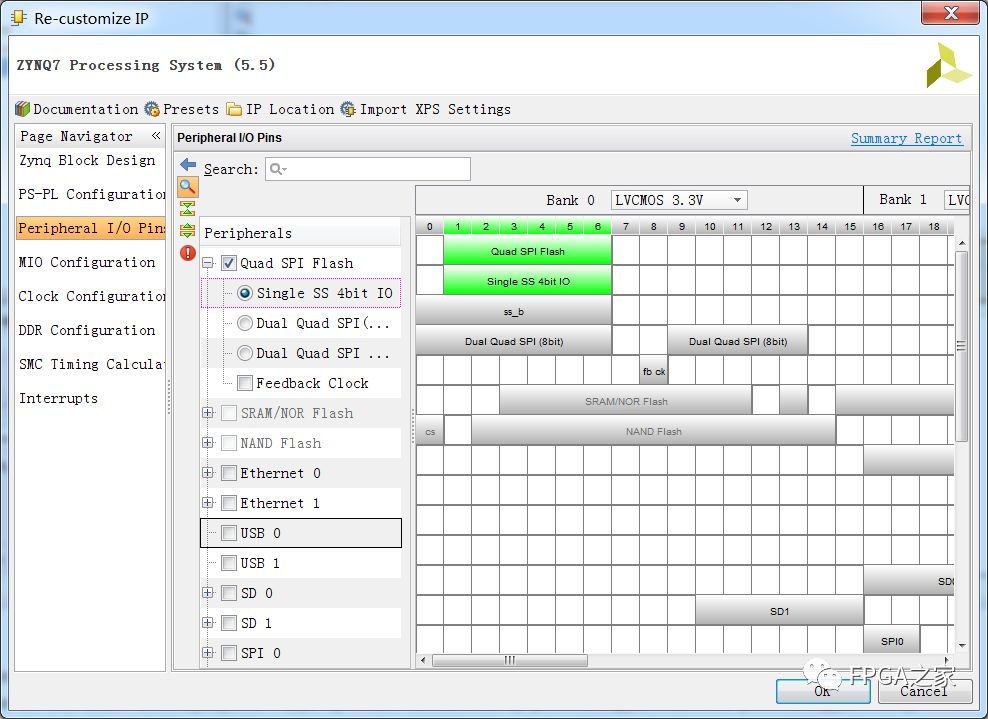

(3)双击所添加的zynq7,配置peripheral I/O,我们只保留Quad SPI Flash

(4)在 Diagram 界面里点击"Run Block Automation"完成对 ZYNQ7 Processing System IP核的配置,生成外部 ZYNQ 系统的外部链接 IO 管脚。

(5)在 Source 窗口中选中 design_1.bd,右键并先后选择Generate Output Projects 和 Create HDL Wrapper 选项,生成顶层文件design_1_wrapper。

(6)在顶层文件中例化我们原来的工程;(特别注意:要将原来工程的外部引脚也例化为现在顶层工程的I/O,并配置好约束)。

(7)重新生成bit流。

(8)Export to Hardware(包含bitstram 文件),Launch SDK,暂时告别VIVADO,进入SDK进行操作。

2.1 SDK操作

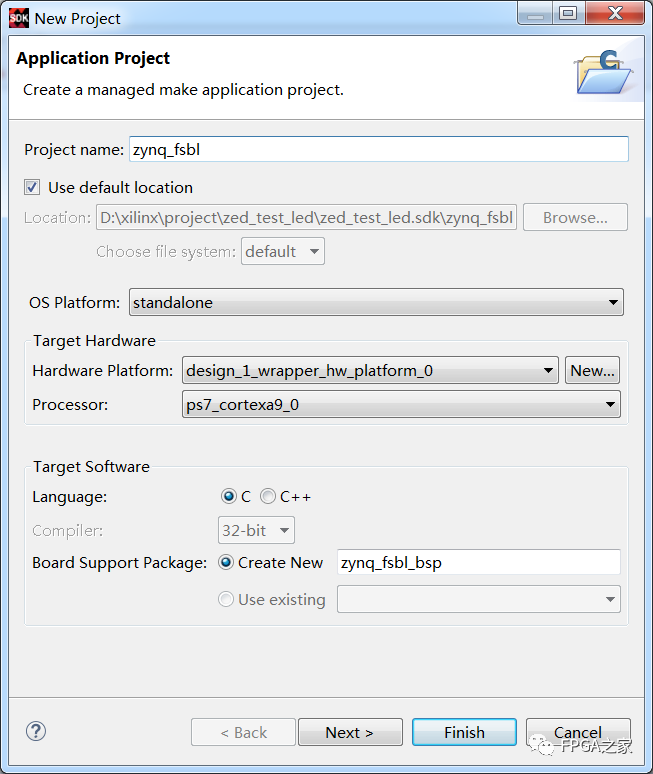

(1)进入SDK 开发环境后,点击菜单 File -> New -> Application Project。

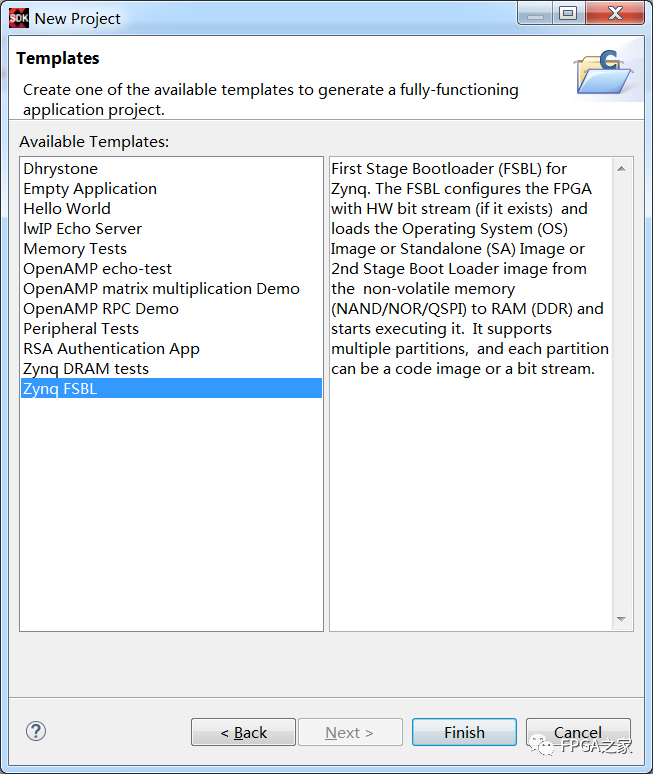

(2)点击next,选择Zynq FSBL

(3)接下去我们要把 FSBL 可执行文件,FPGA PL的bit比特流文件和PS应用程序结合成一个 Bin 文件或Mcs文件。

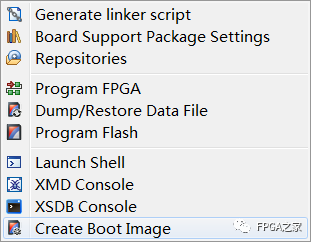

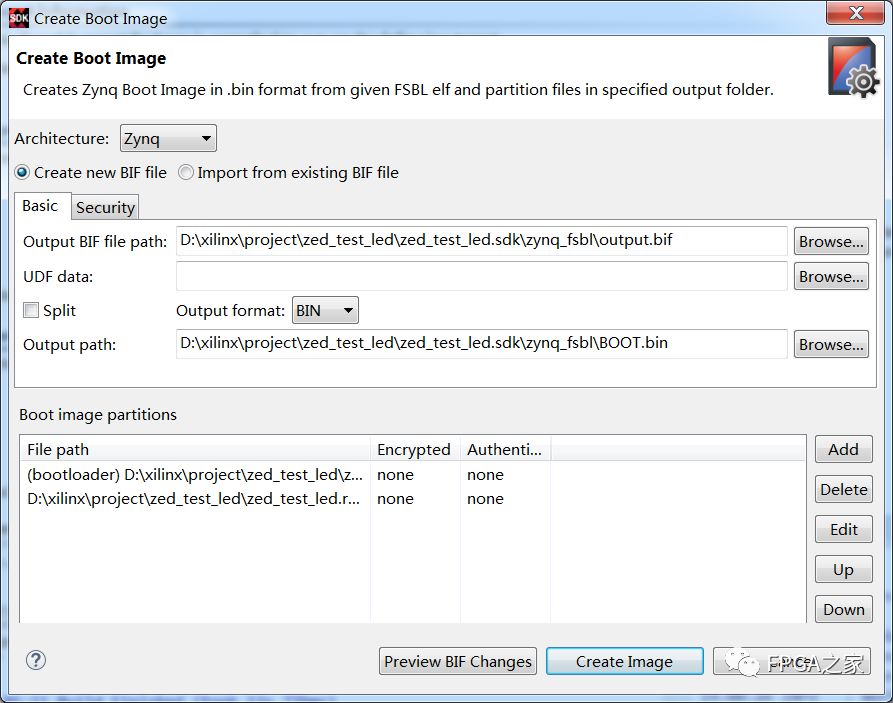

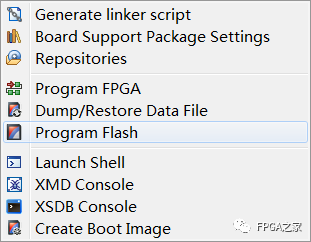

选择菜单 Xilinx Tools->Create Boot Image:

选择output.bif的存放地址,选择生成bin文件还是mcs文件,然后依次添加zynq_fsbl.elf(BootLoader)、bit文件、应用程序elf文件(这个如果没有可以省略),最终生成用于固化的bin或者mcs文件。

(4)将生成的bin或者mcs文件下载到Flash(经过验证,这两种类型的文件都可以)

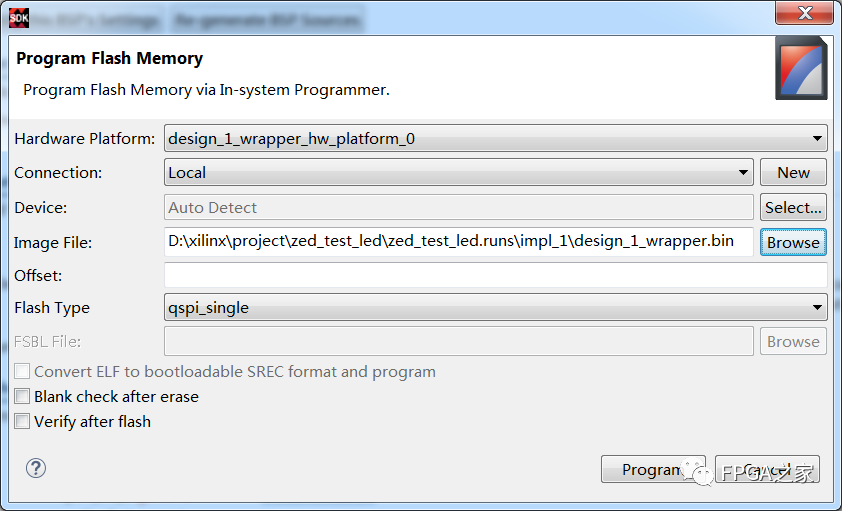

开发板上电,选择菜单 Xilinx Tools->Program Flash:

加载文件:

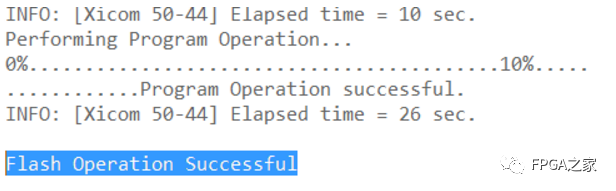

(5)点击Program,出现如下信息,则成功。然后断电,切换板子的启动方式,然后重新上电就会发现板子自动配置完成的灯亮了,搞定!

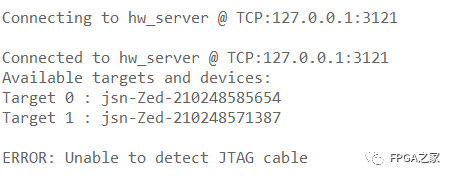

注意:若出现以下信息,排除掉Jtag线缆的问题之后,可能的原因是之前同时连接过多个开发板,导致识别出来的芯片型号有不止一个,然后它就检测到JTAG断开(我就是这个问题)。

解决方法很简单:关掉SDK,重新打开,重新Program Flash即可。

审核编辑 :李倩

-

FPGA

+关注

关注

1631文章

21806浏览量

606688 -

寄存器

+关注

关注

31文章

5377浏览量

121394

原文标题:二、生成BOOT.bin或者BOOT.mcs

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

详解Zynq的两种启动模式

ZYNQ的启动流程

ZYNQ的启动流程

评论