几乎所有的芯片设计、芯片验证工程师,每天都在和VCS打交道,但是由于验证环境的统一化管理,一般将不同的编译仿真选项集成在一个文件里,只需要一两个人维护即可。所以大部分人比较少有机会去深入地学习VCS的仿真flow。基于此,本文将介绍VCS仿真的两种flow,概述这两种flow分别做了哪些事!

VCS是一个高性能、高容量的编译代码仿真器,它将高级抽象的验证技术集成到一个开放的本地平台中。它能够分析、编译和编译Verilog、VHDL、SystemVerilog和OpenVera所描述的design,并且还提供了一组仿真和调试功能来验证design,这些特性提供了源代码级debug和仿真结果。支持原生测试平台、SystemVerilog、验证规划、覆盖率分析和收敛。

除了标准Verilog、VHDL和混合HDL和SystemVerilog编译和仿真功能,VCS包括以下集成的功能和工具集:

SystemC

Verdi

Unified Command-lineInterface (UCLI)

Built-In CoverageMetrics

DirectC Interface

VCS还可以与第三方工具集成,如Specman、Denali和其他加速和仿真系统。

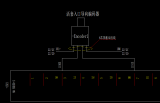

下面介绍VCS的两种仿真flow:two-step flow和 three-step flow

- two-step flow

使用vcs,语法如下:

vcs [compileoptions] Verilog_files

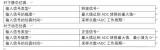

常用选项如下:

-h or -help

列出最常用的VCS编译和运行时选项的描述

-ID

返回有用的信息,如VCS版本和构建日期,VCS编译器版本,以及工作站名称、平台和主机ID

-v filename

指定Verilog库文件,VCS在这个文件中查找模块定义和在源代码中找到的UDP实例

-y directory

指定Verilog库目录,VCS在这个目录的源文件中搜索模块定义和UDP实例。VCS在这个目录中搜索与实例中模块或UDP标识符同名的文件(不是实例名)。如果找到了这个文件,VCS会在文件中搜索模块或UDP定义来解析实例

ps:如果你在不同的库中有多个同名的模块,VCS会选择用第一个-y选项指定的库中定义的模块

+incdir+directory+

指定VCS搜索包含文件的directory目录,可以使用加号(+)字符指定多个目录

+inbext+extension+

指定VCS只在库目录中搜索具有指定文件扩展名的文件,可以指定多个扩展名,用加号(+)分隔扩展名。例如,+libext+.v+ .V+,指定在库中搜索扩展名为.v或.V的文件

+liborder

指定在VCS找到实例的库的剩余部分中搜索未解析的模块实例的模块定义

-full64

支持64位模式下的编译和仿真

-file filename

指定包含文件列表和编译时选项的文件

-verdi

启动verdi

-R

编译后立即启动仿真

-pvalue+parameter_hierarchical_name=value

将指定的参数更改为指定的值

-parameters filename

将文件中指定的参数更改为文件中指定的值

-notice

启用详细诊断消息

-q

quiet模式;抑制消息,例如关于VCS使用的C编译器、VCS解析的源文件、顶层模块或指定的timescale的消息

-V

verbose模式;打印消息,例如编译器驱动程序在运行C编译器、汇编器和链接器时打印它执行的命令

-lfilename

指定VCS记录编译消息的文件,如果还有-R选项,VCS将在同一个文件中记录编译和仿真的消息

+define+macro=value+

将源代码中的文本宏定义为值或字符串,可以在Verilog源代码中使用`ifdef编译器指令来测试这个定义

simulation:在编译过程中,VCS生成一个二进制可执行文件simv,使用simv来运行仿真。根据编译的方式,可用两种模式运行仿真:

Interactivemode

在初始阶段以交互模式(调试模式)编译design。在这个阶段,可以使用GUI或通过命令行调试design问题。通过GUI进行调试可以使用Verdi,通过命令行进行调试可以使用UCLI(Unified command line interface)

batch mode

当大多数design问题解决后,可以使用批处理模式(优化模式)编译design。在这个阶段,可以以最小的debug性能来换取更好的性能来运行回归

使用下面的命令行来仿真设计:

simv_executable [runtime_options]

缺省情况下,VCS生成可执行的二进制文件simv,但也可以在vcs命令行中使用编译时间选项 -o 来生成具有指定名称的二进制可执行文件

-gui

当设置了VERDI_HOME时,此选项启动Verdi

-ucli

该选项在UCLI模式下启动simv

- three-step flow

以上内容介绍了使用两种仿真flow的基本步骤,其余功能需要用的时候再查VCS User Guide就行了。

END审核编辑 :李倩

-

仿真

+关注

关注

55文章

4560浏览量

138801 -

编译器

+关注

关注

1文章

1673浏览量

52055 -

Flow

+关注

关注

0文章

10浏览量

9148

原文标题:浅谈VCS的两种仿真flow

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

探索VCS2381/2382/2383:超低功耗磁开关传感器的卓越之选

TVS vs TSS 两种保护机制的深度博弈

【「龙芯之光 自主可控处理器设计解析」阅读体验】--LoongArch的SOC逻辑设计

用PLC实现卷径计算的两种算法

VCS安装教程及常见问题和解决办法

vcs和vivado联合仿真

ADI GMSL技术两种视频数据传输模式的区别

这两种TVS有啥不同?

两种散热路径的工艺与应用解析

CMOS 2.0与Chiplet两种创新技术的区别

两种驱动方式下永磁直线开关磁链电机的研究

两种感应电机磁链观测器的参数敏感性研究

铷原子钟与CPT原子钟:两种时间标准的区别

使用VCS两种仿真flow的基本步骤

使用VCS两种仿真flow的基本步骤

评论