前言

测试原理

C-V测量广泛用于测量半导体参数,研发端的工程师往往采用C-V测量技术评估新材料、开发前的验证评估工作,测试端的工程师会对一些被动元器件和功率器件、对供货商的材料进行资格检验,检测工艺参数。

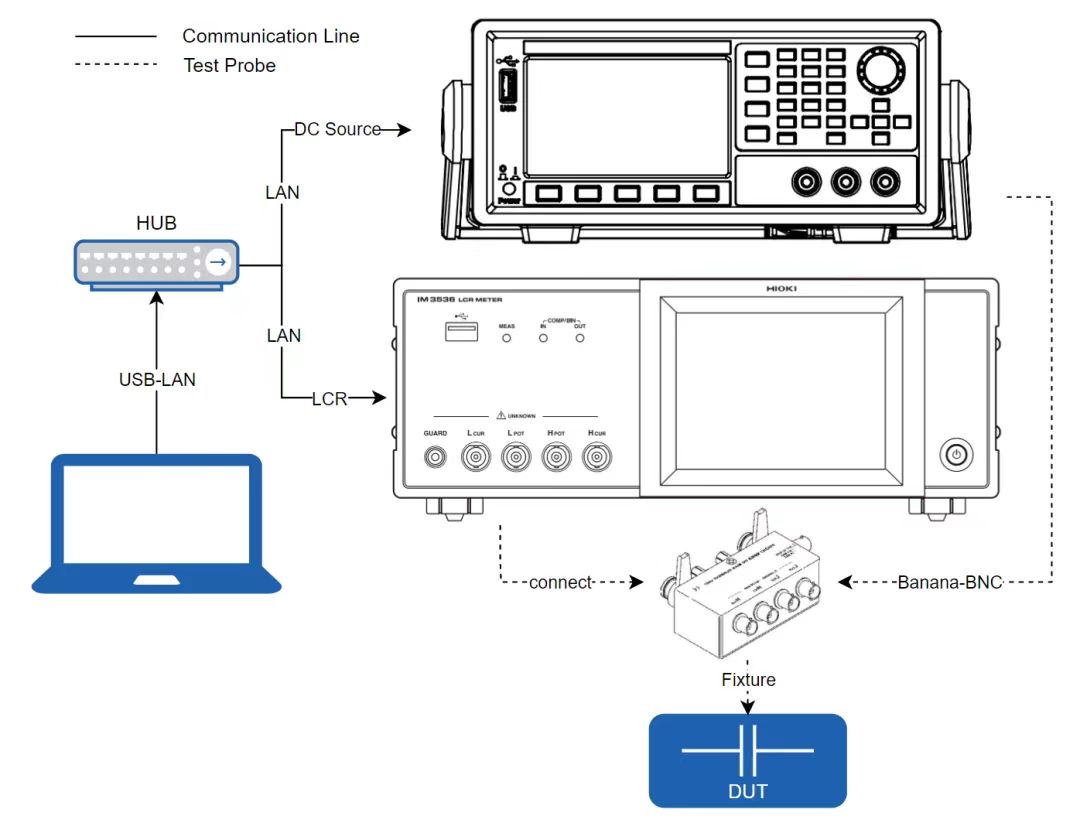

HIOKI日置C-V测试系统的回路结构图如下所示,利用LCR表的四端子测试方法,将电压源负端与LCR的GUARD端子相连,并由偏置单元施加到被测物两端。通过交流信号注入法来获取不同偏置电压下的阻抗、相位、电容值、损耗因子等相关电参数,并通过PC软件描绘出特性曲线。

直流电压偏置电路

测试应用

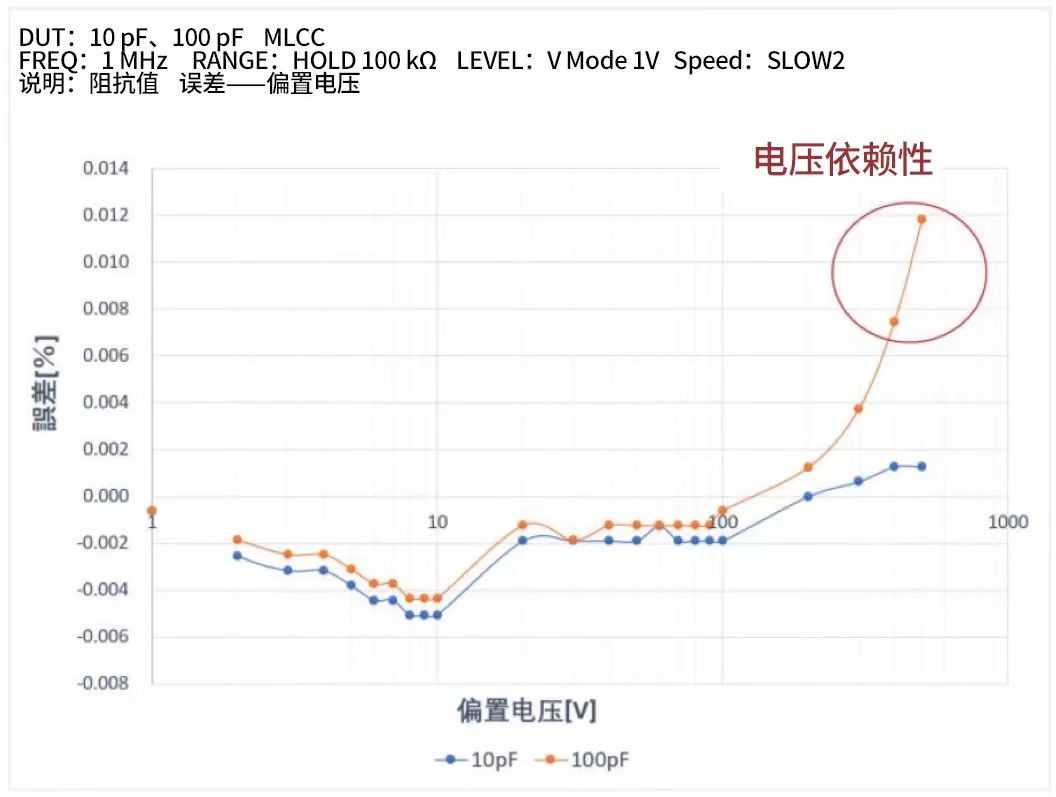

MLCC贴片电容自身的直流偏压特性(DC Bias Characteristics)—— 在MLCC两端施加直流电压时,直流偏压对极化机制的钳制作用使偶极子的自由翻转变得更加困难,相比未施加直流电压时,电压的升高使得其介电常数逐渐变小,导致在两端直流电压升高的过程中,电容值呈下降趋势。

大容量的陶瓷电容的标称容值随着外部直流工作点的变化而明显地变化(例如DCDC的输出滤波电容等),故在设计电路时,是需要考虑和计算验证的。

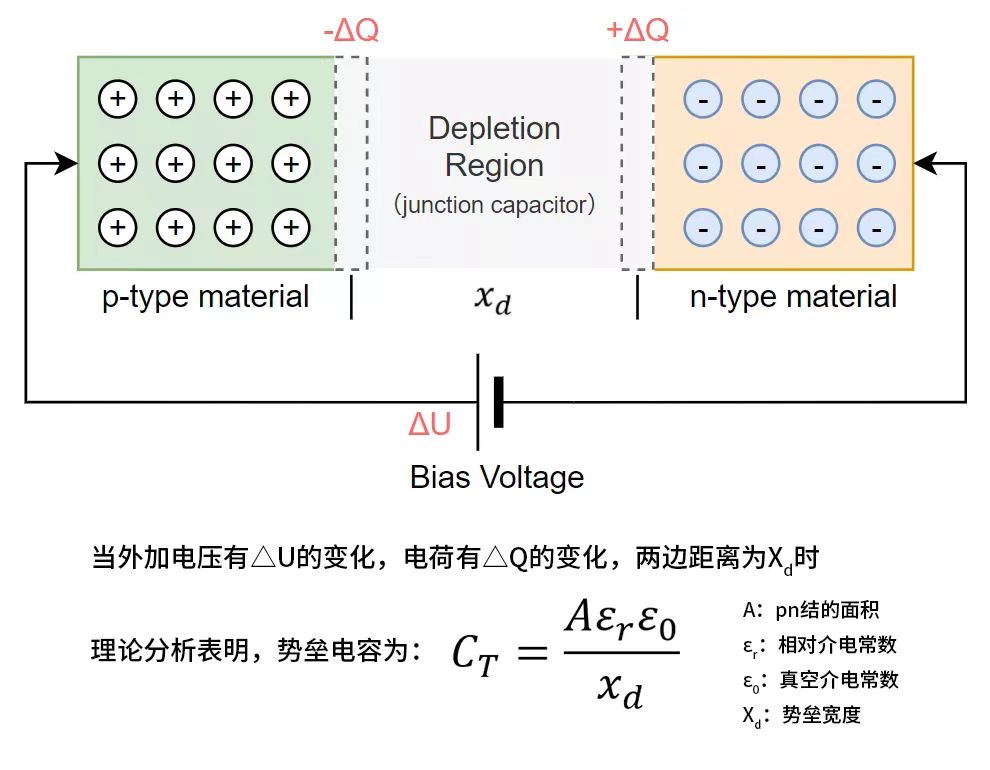

应用②:二极管结电容

结电容是二极管的一个寄生参数,由内部载流子的物理特性而形成的电容效应,可以看作是并联在二极管上的等效电容。结电容分为势垒电容与扩散电容构成。PN结外施加正偏电压时,结电容主要是扩散电容,PN结施加反偏电压时,结电容主要是势垒电容。在高频的电路设计中,往往要根据实际情况需要考虑结电容带来的影响。

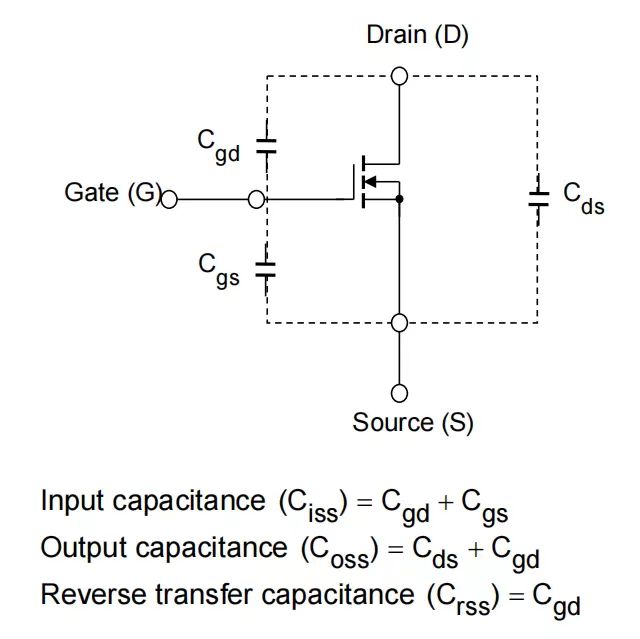

一般MOSFET的Datasheet中与寄生电容相关的参数为表中的Ciss、Coss、Crss,这三项是影响开关特性的重要参数,厂家将其分类到动态特性(Dynamic Characteristic)中,并标注相关测试条件供工程师参考。上述寄生电容对漏极-源极间电压VDS具有依赖性,当VDS增加时,C值有下降的趋势。HIOKI日置的C-V解决方案可以描绘出各寄生参数关于VDS的特性曲线。

下面简单介绍MOSFET的一般动作过程:可以简单的理解为驱动源对MOSFET的输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后,MOS管逐渐导通。随后Vds开始下降,Id开始爬升,MOS管进入饱和区。但由于米勒效应的存在,Vgs会持续一段时间不再上升,尽管Id已经达到峰值,Vds还在继续下降,直到米勒电容充满电,Vgs又回升到驱动电压的值,此时Vds彻底归零,开通结束。

以上的动态过程影响了MOS的动作时间、驱动能力和开关损耗等多方面特性,在驱动回路的设计中往往要对此进行评估和考量。

(图1)电容等效电路

(图2)电容与 VDS

图片来源:https://toshiba-semicon-storage.com/cn/semiconductor/knowledge/faq/mosfet.html

系统构成

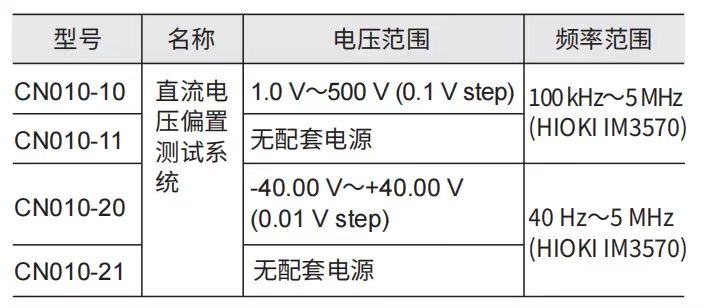

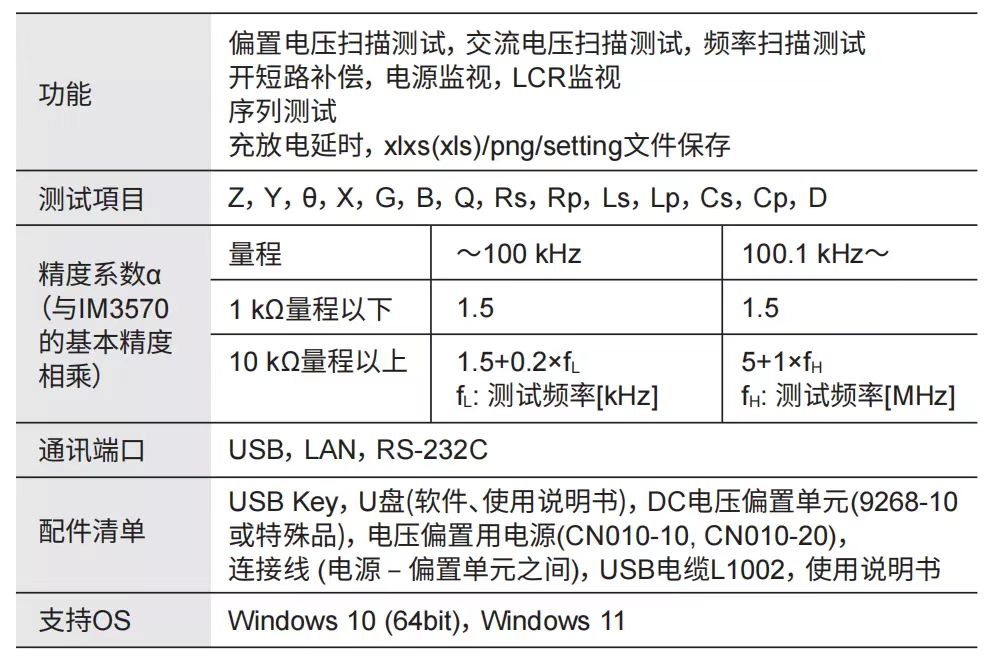

CN010电压偏置测试系统由HIOKI日置LCR测试仪/阻抗分析仪、电压偏置单元、电源及通讯设备构成。具体可参考下文的参数规格。

参数规格

产品参数

结语

电压偏置测试系统CN010拥有丰富的选件,覆盖广泛测试需求的硬件系统,通过整体的性能评价和预先验证,为客户提供可靠准确的测试方案。同时,其友好的图标显示界面以及即时的数据保存,更可以帮助用户提高开发效率。

-

半导体

+关注

关注

334文章

27277浏览量

217983 -

HIOKI

+关注

关注

0文章

5浏览量

8777 -

测试系统

+关注

关注

6文章

817浏览量

62110 -

MOS

+关注

关注

32文章

1269浏览量

93675

发布评论请先 登录

相关推荐

ADS131E06输入信号匹配网络的共模偏置电压怎么处理?

VCA810的直流偏置远大于芯片资料上的偏置电压,为什么?

如何为LCR测试仪添加直流偏置?

LMH6552系统上电后,对输入的交流信号测试时,会有直流偏置电平出现,为什么?

使用OPA836做单电源放大电路时,什么原因会导致偏置电压发生变化?

OPA541 PSpice仿真输出有偏置电压怎么解决?

异步置零和同步置零的区别在哪里

偏置电路的作用是什么呢

日置/HIOKI电流探头CT6700的产品特点及其应用领域

HIOKI日置电压偏置测试系统CN010

HIOKI日置电压偏置测试系统CN010

评论