电子发烧友网报道(文/黄山明)近日,华为密集公布了多项技术专利,其中引人注意的是华为再次公布了两项与芯片堆叠有关的专利。为何说再次,因为就在一个月前,华为同样公开了“一种芯片堆叠封装及终端设备”的专利。多项与芯片堆叠相关专利的公开,或许也揭露了华为未来在芯片技术上的一个发展方向。

华为芯片堆叠技术之路

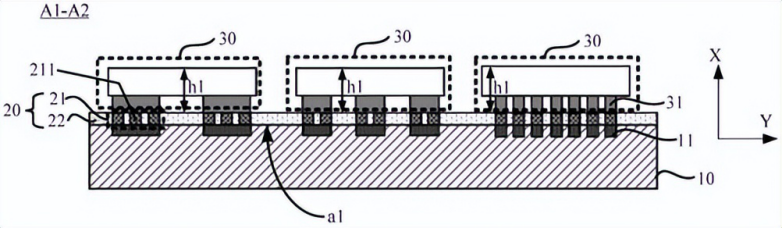

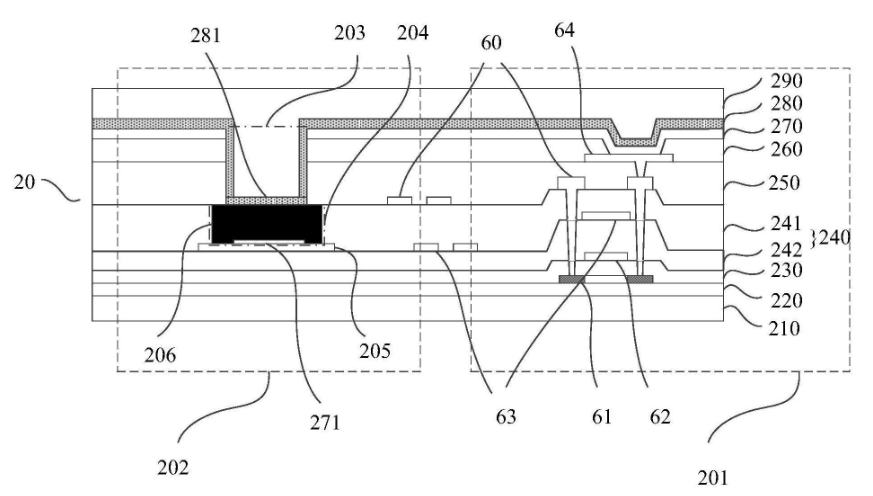

本次华为所公布的两项芯片堆叠相关专利非常有意思,一项是“一种多芯片堆叠封装及制作方法”(申请公布号:CN114287057A),用来解决多芯片的应力集中问题,能够以进行更多层芯片的堆叠。

另一项为“芯片堆叠封装结构及其封装方法、电子设备”(申请公布号:CN114450786A),用于解决如何将多个副芯片堆叠单元可靠的键合在同一主芯片堆叠单元上的问题。

图源:国家知识产权局

如果往前翻,可以发现早在2012年,华为便已经对芯片堆叠技术进行专利公开,该专利为“芯片堆叠封装结构”(申请公布号:CN102693968A),主要设计芯片封装技术领域,实现芯片的高密度堆叠,提高芯片堆叠封装结构的散热效率。

其后几年,华为也在不断对外公开其芯片堆叠的相关技术,足以证明长期以来华为都在这项技术上深耕研发。

众多厂商竞逐芯片堆叠技术

从国家知识产权局所公布的专利来看,在芯片堆叠技术上并非华为的专场,众多半导体大厂都在进行相关研发探索。如三星电子、赛灵思、博世、长鑫存储、长江存储等,而芯片堆叠技术为何会受到如此多厂商的青睐?

芯片堆叠,也就是封装堆叠,或者一个更广为人知的称呼是3D封装,这项技术的确是未来半导体发展的重要方向。

为何如此说?这就需要谈到目前芯片工艺制程发展了。随着芯片工艺制程的快速发展,其效益却面临着边际递减的问题,也就是说先进工艺制程可以让芯片的性能更强、功耗更低,但却无法使得芯片变得更便宜。

一个直观的感受是,如今高端旗舰手机价格越来越昂贵了,而其中成本的大头来自手机SoC,5nm的芯片要比7nm贵的多。也许不少消费者认为理所应当,但在过去可不是如此。

在芯片工艺制程发展之初,先进制程不仅能带来更强劲的性能,让芯片变得更小,同时也能让晶体管成本下降。但从28nm以后,这个趋势被打破了,这也是为何许多对性能与功耗要求不高的芯片仍然采用28nm制程,因为这样具有最佳性价比。

那么不想增加成本用更先进的制程,又想拥有更强的性能,有没有方法实现呢?当然有,那就是采用芯片堆叠技术。比如英国的AI芯片公司Graphcore发布了一款IPU产品Bow,采用台积电7nm工艺生产,经过台积电研发的3D WoW硅晶圆堆叠技术封装后,性能提升了40%,功耗降低16%。

这是什么概念,要知道台积电宣传时的5nm工艺相比7nm在同等功耗下提升15%的性能,而在同等功耗下则可以提升30%的性能,对比来看,芯片堆叠技术反而表现更强。

台积电的这项3D WoW硅晶圆堆叠技术,自2018年被提出,可以认为是类似于3D NAND闪存多层堆叠一样,将两层Die以镜像方式垂直堆叠起来,以更先进的封装技术提升芯片性能。

有了芯片堆叠技术,就能够让厂商以成熟工艺来获得更高的性能,同时还能降低成本,毕竟成熟工艺良率更高,产能更大。

芯片堆叠技术能否帮助华为渡过燃眉之急

就在不久前举办的华为2021年业绩发布会上,时任华为轮值董事长的郭平表示,未来华为可能会采用多核结构的芯片设计方案,以提升性能。同时,采用面积换性能,用堆叠换性能,使得不那么先进的工艺也能持续让华为在未来的产品里面,能够具有竞争力。

其中的面积换性能、堆叠换性能,指的大概就是芯片堆叠技术了。显然对于这项技术,华为予以厚望。

同时在上个月召开的华为折叠屏及全场景新品发布会中,华为常务董事、终端BG CEO、智能汽车解决方案BU CEO余承东更是公开表示,当前华为手机的供应得到了极大地改善,去年华为手机供应很困难,而今年华为手机开始回来了,所以大家想买华为产品,华为手机都能买到,这是一个最大的好消息。

如果余承东没有说“大话”,那么可以大胆的推测,华为在今年开始逐步解决芯片供给问题,而解决供应问题的一项方法便是采用芯片堆叠技术。

就如同Graphcore的AI芯片Bow一样,能够使7nm芯片通过堆叠技术之后性能要强于5nm。苹果公司在今年的春季发布会上,便带来了一款名为“M1 Ultra”的芯片,该苹果采用特殊的封装工艺,将两块M1 Max芯片串联到了一起,从而实现了90%的性能提升。

显然,华为也可以通过类似方法让低制程芯片也焕发出新的生机,从而得到更高的性能表现,实现让华为的产品具备一定市场竞争力的承诺。在一定程度上来说,使用芯片堆叠技术,的确能够帮助华为解决无法获得先进制程芯片下,产品竞争力缺失的问题。

写在最后

需要注意的是,芯片堆叠技术并非万能。诚然,在一代制程差距内,通过芯片堆叠技术可以让低制程芯片在性能接近甚至超越高制程芯片,并且还能拥有良品率高、成本低等优势,但这也是有极限的。

比如7nm通过芯片堆叠技术可以拥有5nm芯片的性能表现,而14nm芯片则需要6颗叠在一起才能在晶体管上比得上一颗5nm芯片。这样一来,不仅是体积大增,同时由于线宽过小,会导致极间漏电流增大,逻辑错误增加,极间电容因为布线增多也会大幅增加,从而导致整体功耗增加数倍。而功耗的增加也导致发热情况非常严重,华为的2012年的专利便已经意识到芯片堆叠的发热问题。

即便这些问题都能够解决,但更关键的问题是,即便通过芯片叠加,使晶体管数量能够比肩高制程芯片,但算力利用率显然不是简单的1+1=2,大部分情况下最多只能得到1.3左右,即便是苹果,其性能也是在1.8左右。这项技术想要真正走向成熟,还有不小的路程。

一个有趣的现象是,华为近几款智能手机都在向折叠屏发展,有可能也是为以后芯片堆叠所做的准备。

-

华为

+关注

关注

216文章

34435浏览量

251729 -

专利

+关注

关注

3文章

586浏览量

39209 -

芯片堆叠

+关注

关注

0文章

18浏览量

14582

发布评论请先 登录

相关推荐

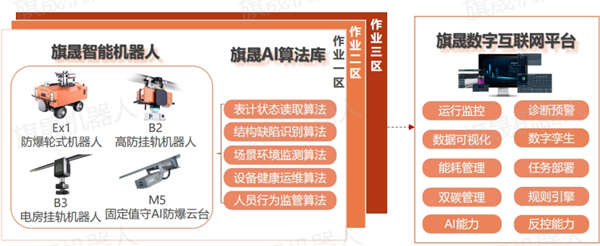

油气化工事故频发“痛点”何解?旗晟智能巡检方案给出答案

最新公布!华为新专利,脑机接口芯片曝光...大脑设备直接通信?? #芯片 #华为 #HGSEMI_华冠半导体

双芯片磁性位置传感器中堆叠芯片和并排芯片实施方案之间的比较

【好书推荐】RT-Thread设备驱动开发指南

华为气球飞行机器人专利公布 可提高安全性及续航等

华为公布一项名为“钠电池复合正极材料及其应用”的发明专利

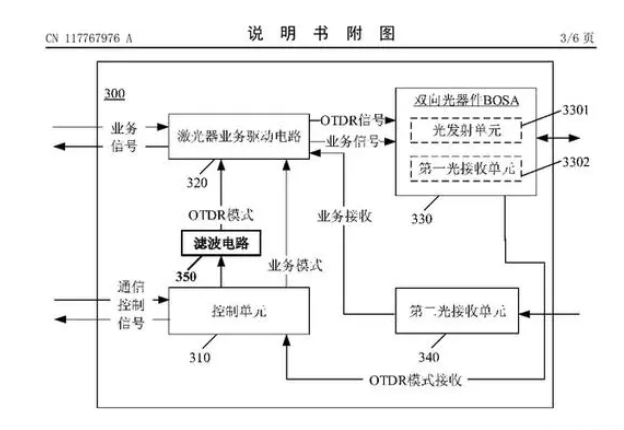

华为公布创新光通信专利

智芯公司3项专利成果获评第二届能源行业高价值专利(技术)成果

华为与vivo、亚马逊签署专利交叉许可协议

华为显示面板专利公布,聚焦介质层、平坦化层、像素界定层及电路设计

华为公布芯片堆叠专利,能否解缺芯燃眉之急

华为公布芯片堆叠专利,能否解缺芯燃眉之急

评论