1、SPI协议简介

1.1 SPI协议概括

SPI,是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,比如MSP430单片机系列处理器。

1.2 SPI优点

1):支持全双工通信

2):通信简单

3):数据传输速率快

1.3 缺点

没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据

可靠性上有一定的缺陷。

2、 特点

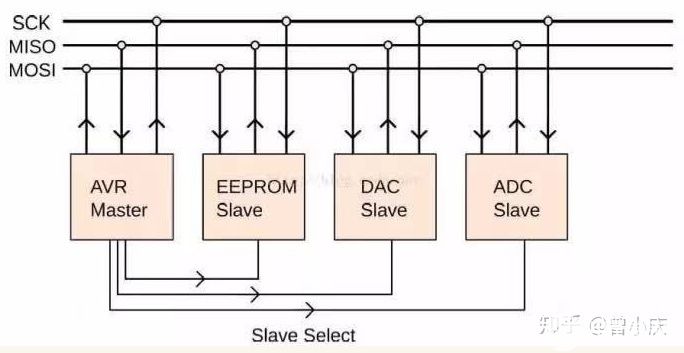

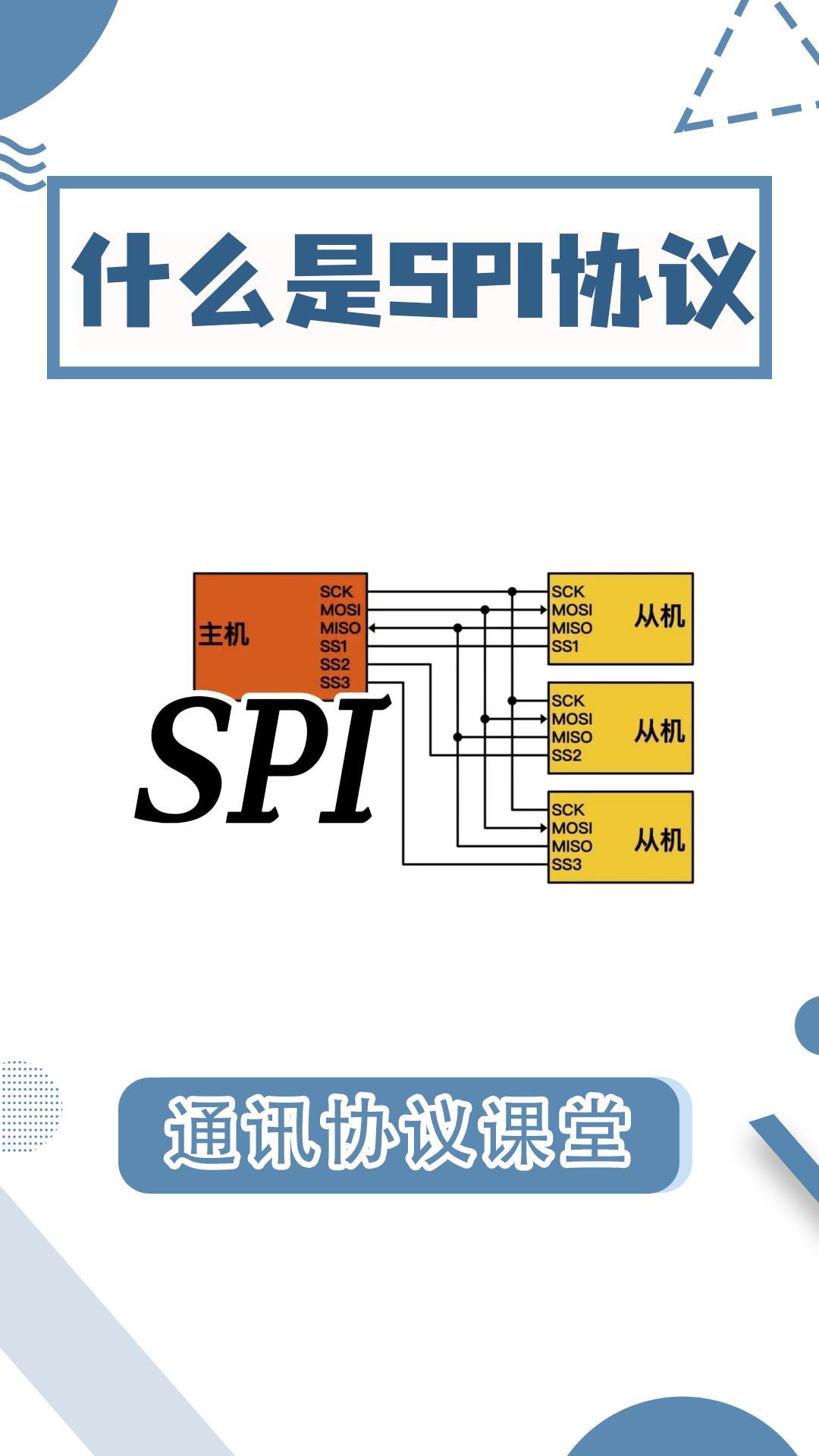

2.1 采用主-从模式(Master-Slave) 的控制方式

SPI 规定了两个 SPI 设备之间通信必须由主设备 (Master) 来控制次设备 (Slave)。 一个 Master 设备可以通过提供 Clock 以及对 Slave 设备进行片选 (Slave Select) 来控制多个 Slave 设备,SPI 协议还规定 Slave 设备的 Clock 由 Master 设备通过 SCK 管脚提供给 Slave 设备, Slave 设备本身不能产生或控制 Clock,没有 Clock 则 Slave 设备不能正常工作。

2.2 采用同步方式(Synchronous)传输数据

Master 设备会根据将要交换的数据来产生相应的时钟脉冲(Clock Pulse),时钟脉冲组成了时钟信号(Clock Signal) ,时钟信号通过时钟极性 (CPOL) 和 时钟相位 (CPHA) 控制着两个 SPI 设备间何时数据交换以及何时对接收到的数据进行采样,来保证数据在两个设备之间是同步传输的。

2.3 数据交换(Data Exchanges)

SPI 设备间的数据传输之所以又被称为数据交换,是因为 SPI 协议规定一个 SPI 设备不能在数据通信过程中仅仅只充当一个 "发送者(Transmitter)" 或者 "接收者(Receiver)"。在每个 Clock 周期内,SPI 设备都会发送并接收一个 bit 大小的数据(不管主设备好还是从设备),相当于该设备有一个 bit 大小的数据被交换了。一个 Slave 设备要想能够接收到 Master 发过来的控制信号,必须在此之前能够被 Master 设备进行访问 (Access)。所以,Master 设备必须首先通过 SS/CS pin 对 Slave 设备进行片选, 把想要访问的 Slave 设备选上。 在数据传输的过程中,每次接收到的数据必须在下一次数据传输之前被采样。如果之前接收到的数据没有被读取,那么这些已经接收完成的数据将有可能会被丢弃,导致 SPI 物理模块最终失效。因此,在程序中一般都会在 SPI 传输完数据后,去读取 SPI 设备里的数据, 即使这些数据(Dummy Data)在我们的程序里是无用的(虽然发送后紧接着的读取是无意义的,但仍然需要从寄存器中读出来)。

2.5 SPI只有主模式和从模式之分

SPI没有读和写的说法,因为实质上每次SPI是主从设备在交换数据。也就是说,你发一个数据必然会收到一个数据;你要收一个数据必须也要先发一个数据。

3、 工作机制

3.1 概述

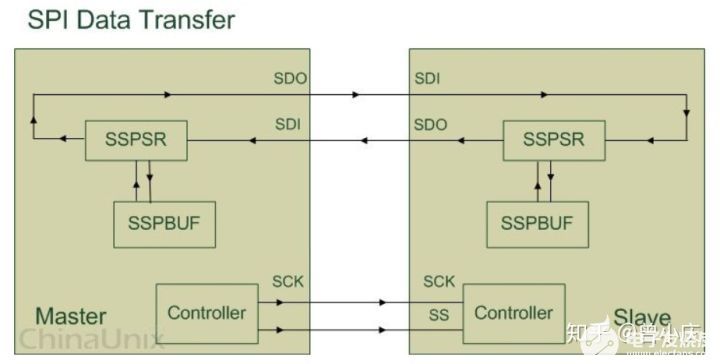

上图只是对 SPI 设备间通信的一个简单的描述, 下面就来解释一下图中所示的几个组件:

- SSPBUF:泛指 SPI 设备里面的内部缓冲区,一般在物理上是以 FIFO 的形式,保存传输过程中的临时数据;

- SSPSR:泛指 SPI 设备里面的移位寄存器,它的作用是根据设置好的数据位宽(bit-width) 把数据移入或者移出 SSPBUF;

- Controller:泛指 SPI 设备里面的控制寄存器,可以通过配置它们来设置 SPI 总线的传输模式。

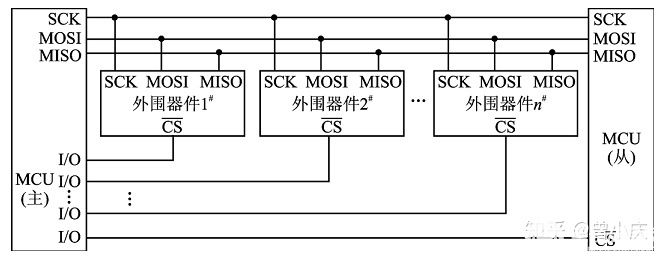

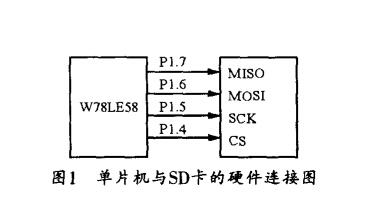

通常情况下,我们只需要对上图所描述的四个管脚(pin) 进行编程即可控制整个 SPI 设备之间的数据通信:

- SCK:主要的作用是 Master(主)设备往 Slave(从)设备传输时钟信号, 控制数据交换的时机以及速率;

- SS/CS:用于 Master(主)设备片选 Slave (从)设备,使被选中的 Slave(从)设备能够被 Master(主)设备所访问;

- SDO/MOSI:在 Master(主)上面也被称为 Tx-Channel,作为数据的出口,主要用于 SPI 设备发送数据;

- SDI/MISO:在 Master(主)上面也被称为 Rx-Channel,作为数据的入口,主要用于SPI 设备接收数据;

SPI 设备在进行通信的过程中,Master 设备和 Slave 设备之间会产生一个数据链路回环(Data Loop),就像上图所画的那样, 通过 SDO 和 SDI 管脚, SSPSR 控制数据移入移出 SSPBUF,Controller 确定 SPI 总线的通信模式,SCK 传输时钟信号。

SDI(数据输入)、SDO(数据输出)、SCK(时钟)、CS(片选)

(1)、SDO/MOSI – 主设备数据输出,从设备数据输入;

(2)、SDI/MISO – 主设备数据输入,从设备数据输出;

(3)、SCK – 时钟信号,由主设备产生;

(4)、CS/SS – 从设备使能信号,由主设备控制。当有多个从设备的时候,因为每个从设备上都有一个片选引脚接入到主设备机中,当我们的主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低或者是拉高。

3.2 SPI相关的缩写或说法

SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下:

- CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性

- CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位

- SCK=SCLK=SPI的时钟

- Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿(falling edge)对于一个时钟周期内,有两个edge,分别称为:

- Leading edge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候;

- Trailing edge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

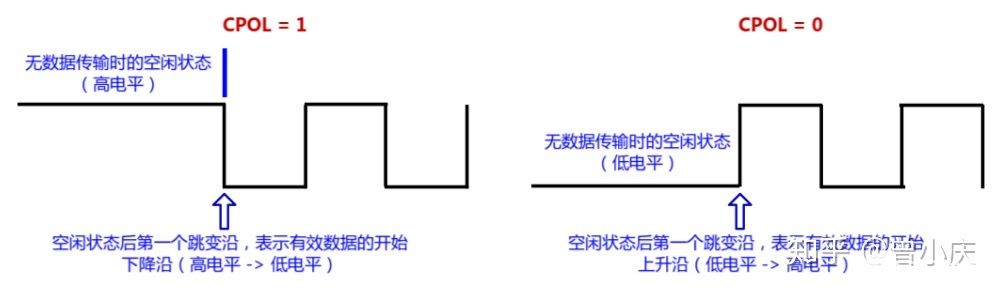

3.3 SPI总线的极性和相位

CPOL配置SPI总线的极性,CPHA配置SPI总线的相位。

3.3.1 SPI总线的极性

极性,会直接影响SPI总线空闲时的时钟信号是高电平还是低电平。

CPOL = 1:表示空闲时是高电平;

CPOL = 0:表示空闲时是低电平。

由于数据传输往往是从跳变沿开始的,也就表示开始传输数据的时候,是下降沿还是上升沿。如下图:

3.3.2 SPI总线的相位

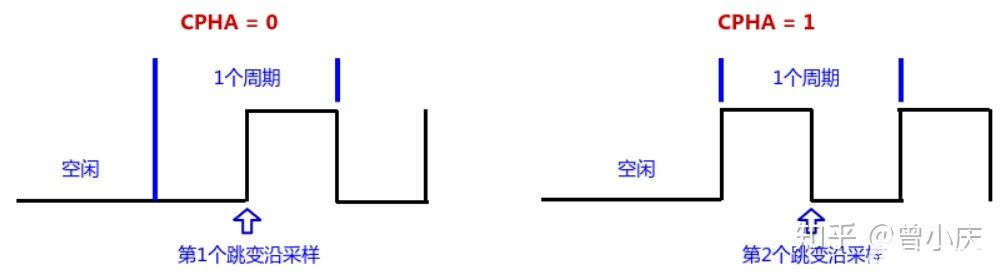

一个时钟周期会有2个跳变沿。而相位,直接决定SPI总线从那个跳变沿开始采样数据。

CPHA = 0:表示从第一个跳变沿开始采样;

CPHA = 1:表示从第二个跳变沿开始采样。

至于跳变沿究竟是上升沿还是下降沿,这取决于 CPOL。记住, CPHA 只决定是哪个跳变沿采样。

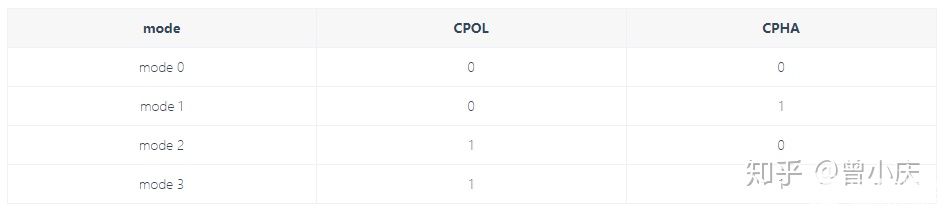

3.4 SPI总线传输的四种模式

CPOL 和 CPHA 的不同组合,形成了SPI总线的不同模式。

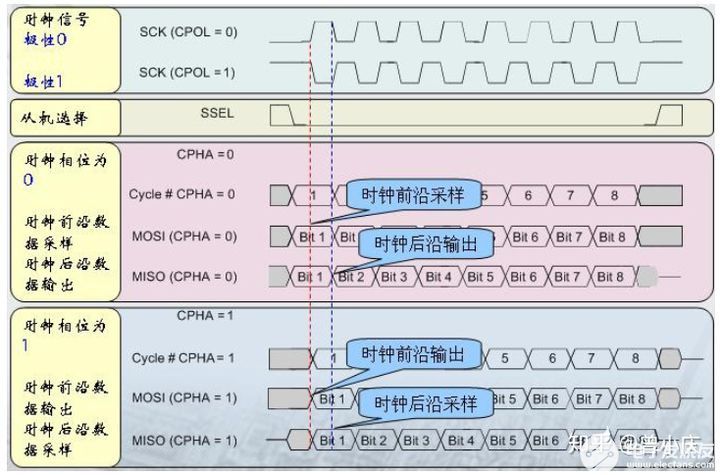

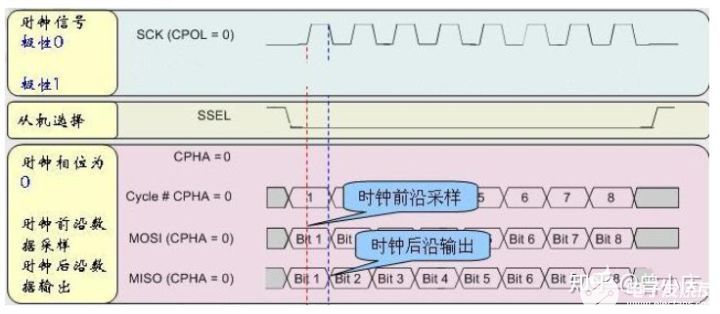

时钟极性CPOL是用来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA

是用来配置数据采样是在第几个边沿:

CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时。

CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时。

CPHA=0,表示数据采样是在第1个边沿,数据发送在第2个边沿。

CPHA=1,表示数据采样是在第2个边沿,数据发送在第1个边沿。

例如:

CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在上升沿,数据发送是在下降沿。

CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是

SCLK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采集是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是

SCLK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

需要注意的是:我们的主设备能够控制时钟,因为SPI通信并不像UART或者IIC通信那样有专门的通信周期,有专门的通信起始信号,有专门的通信结束信号;所以SPI协议能够通过控制时钟信号线,当没有数据交流的时候我们的时钟线要么是保持高电平要么是保持低电平。

-

SPI

+关注

关注

17文章

1900浏览量

102204 -

SPI协议

+关注

关注

0文章

24浏览量

8871

发布评论请先 登录

Java的SPI机制详解

软件模拟SPI协议

spi协议介绍

FPGA实现的SPI协议(一)----SPI驱动

关于SPI通讯的精讲 SPI协议的特点和工作机制

关于SPI通讯的精讲 SPI协议的特点和工作机制

评论