SDRAM凭借其极高的性价比,广泛应用于高速数据存储、实时图像处理等设计当中,但是相对于SRAM、FIFO等其他存储器件,SDRAM的控制相对复杂。虽说是复杂,但也不代表没办法实现,仔细梳理一下,发现SDRAM的控制其实也没这么难。本文就SDRAM的基本概念以及其工作流程做简要介绍。

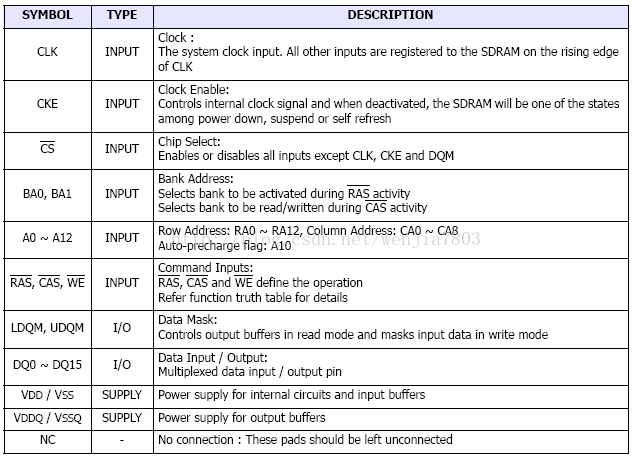

SDRAM 的基本信号:

SDRAM 的基本信号(电源以及地线在这里不讨论)可以分成以下三类,分别是控制信号、地址选择信号以及数据信号:

(1)控制信号:包括片选(CS)、同步时钟(CLK)、时钟有效(CLKE)、读写选择(/WE)、

数据有效(DQM)等;

(2)地址选择信号:包括行地址选择(/RAS)、列地址选择(/CAS)、行/列地址线(A0-A12)分时复用、Bank 块地址线(BA0-BA1);

(3)数据信号:包括双向数据端口(DQ0-DQ15)、接收数据有效信号(DQM)控制等。DQM 为低时,写入/读出有效。

图1 SDRAM 管脚基本信息

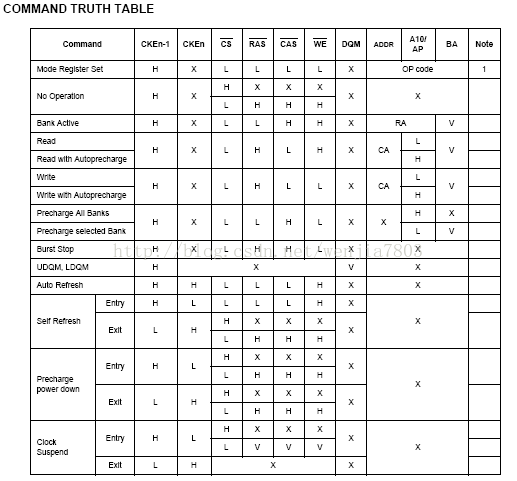

SDRAM相关指令以及关键参数解析

图2 SDRAM相关指令

上图中,把SDRAM用到的所有指令都罗列出来了,其实我们在运用SDRAM的时候,只用到其中部分指令。例如其中write/write with autoprecharge,这两个指令我们都可以对SDRAM进行写操作,只是说在” writewith autoprecharge”指令,我们每写完一个突发长度的数据之后,SDRAM会自动跳出这个状态进行刷新,而在”write”指令,是需要给相应的指令之后才会跳出”WRITE”状态的,所以为了提高SDRAM的运行速度,我们一般采用write指令来提高速度。当然”read”和”read with autoprecharge”这两个指令的区别也是这样的。

常用指令:

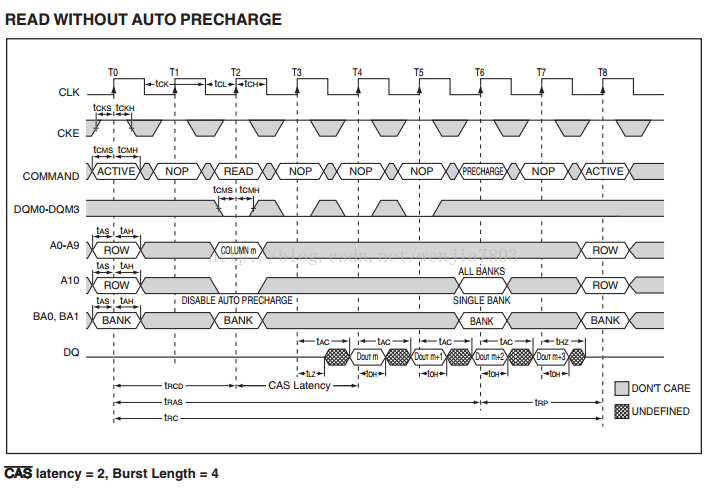

读(read)

在发送列读写命令时必须要与行有效命令有一个间隔,这个间隔被定义为tRCD,即

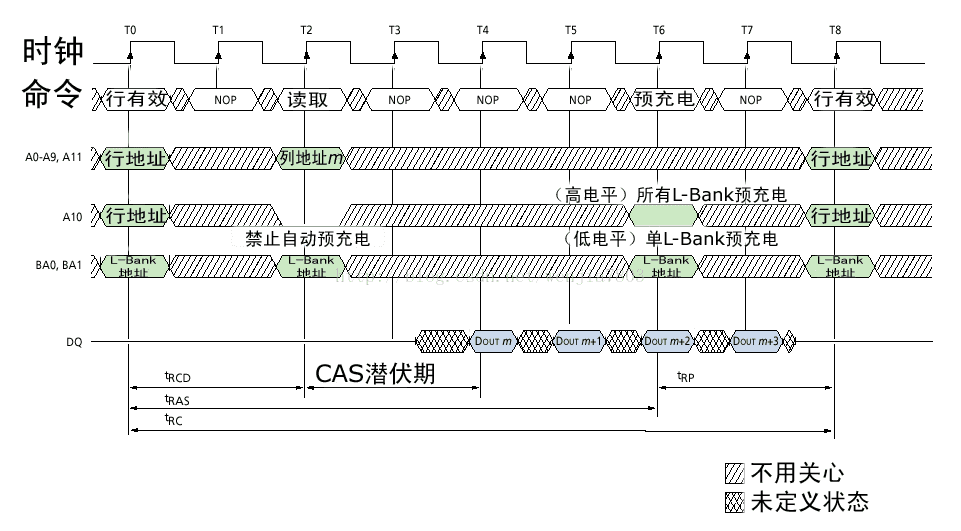

RAS to CAS Delay(RAS 至CAS 延迟),大家也可以理解为行选通周期,这应该是根据芯片存储阵列电子元件响应时间(从一种状态到另一种状态变化的过程)所制定的延迟。下图3中给出了,SDRAM读的相关时序。

图3 SDRAM读时序

SDRAM读时序,简单概括起来就是:1.激活行--à2.选通列-à3.预充电,关闭所在行--à下一次指令。

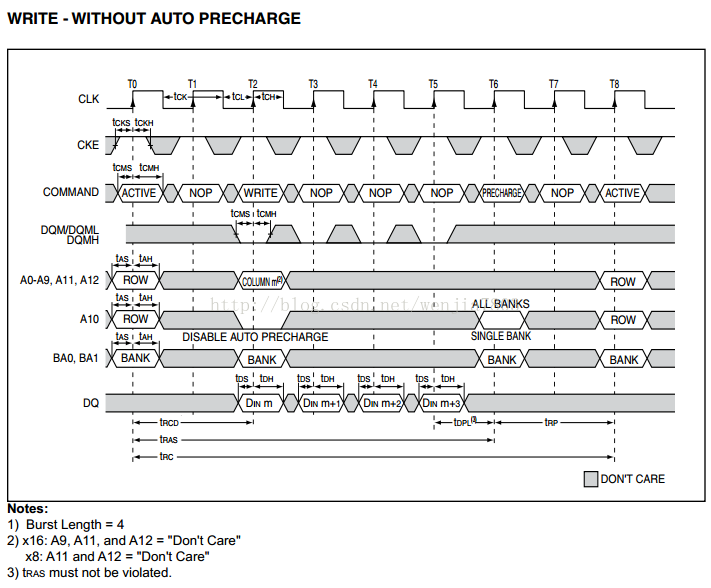

写(write)

图4 SDRAM写时序

预充电(precharge)

由于SDRAM 的寻址具有独占性,所以在进行完读写操作后,如果要对同一L-Bank 的另一行进行寻址,就要将原来有效(工作) 的行关闭,重新发送行/列地址。L-Bank 关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。在发出预充电命令之后,要经过一段时间才能允许发送RAS 行有效命令打开新的工作行,这个间隔被称为tRP(Precharge command Period,预充电有效周期)。和tRCD、CL 一样,tRP的单位也是时钟周期数,具体值视时钟频率而定。

自动刷新(auto refresh)

之所以称为DRAM,就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是DRAM 最重要的操作。刷新操作与预充电中重写的操作一样,都是用S-AMP 先读再写。但为什么有预充电操作还要进行刷新呢?因为预充电是对一个或所有L-Bank 中的工作行操作,并且是不定期的,而刷新则是有固定的周期,依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。

关键参数:

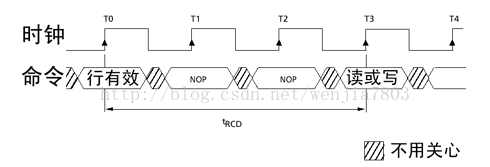

tRCD:

从行有效到读/写命令发出之间的间隔被定义为tRCD,即RAS to CAS Delay(RAS至CAS延迟,RAS就是行地址选通脉冲,CAS就是列地址选通脉冲),大家也可以理解为行选通周期。广义的tRCD以时钟周期(tCK,Clock Time)数为单位,比如tRCD=2,就代表延迟周期为两个时钟周期,具体到确切的时间,则要根据时钟频率而定。

图5 tRCD=3

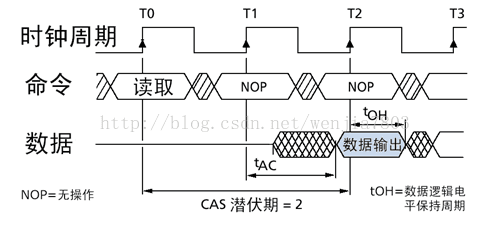

CL:

相关的列地址被选中之后,将会触发数据传输,但从存储单元中输出到真正出现在内存芯片的 I/O 接口之间还需要一定的时间(数据触发本身就有延迟,而且还需要进行信号放大),这段时间就是非常著名的 CL(CAS Latency,列地址脉冲选通潜伏期)。CL 的数值与 tRCD 一样,以时钟周期数表示。如DDR-400,时钟频率为 200MHz,时钟周期为 5ns,那么 CL=2 就意味着 10ns 的潜伏期。不过,CL 只是针对读取操作,对于 SDRAM,写入是没有潜伏期的。

图6 CL=2

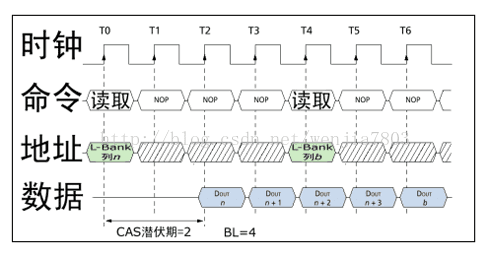

BL:

突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths,简称BL)。在进行突发传输时,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址(SDRAM与DDR SDRAM的突发传输对列寻址的操作数量有所不同,在此不再细说)。这样,除了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是tRCD+CL)外,其后每个数据只需一个周期的即可获得。

图7 突发BL=4

tRP:

由于SDRAM 的寻址具有独占性,所以在进行完读写操作后,如果要对同一L-Bank 的另一行进行寻址,就要将原来有效(工作) 的行关闭,重新发送行/列地址。L-Bank 关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。在发出预充电命令之后,要经过一段时间才能允许发送RAS 行有效命令打开新的工作行,这个间隔被称为tRP(Precharge command Period,预充电有效周期)。

图8 tRP=2

SDRAM的工作流程

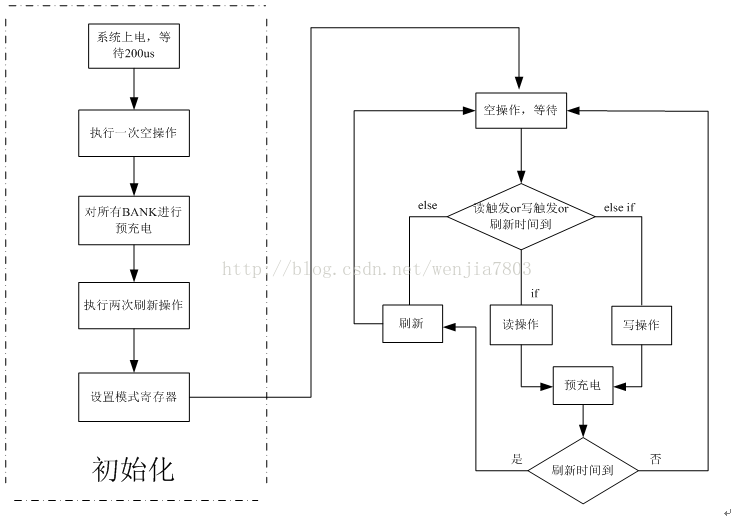

图9 SDRAM基本工作流程

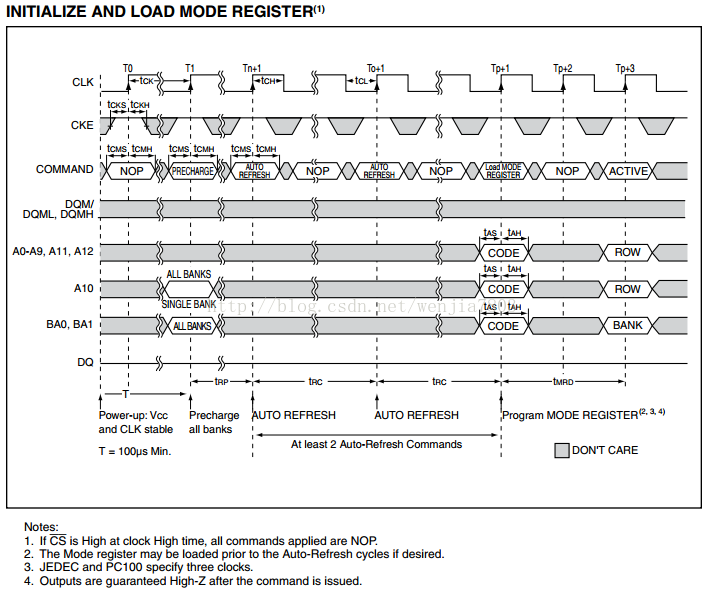

启动初始化:

1、同时启动设备核心电源VDD和设备I/O电源VDDQ。声明并维持CKE引脚为高电平(CKE引脚为Clock Enable,时钟使能信号,高电平表示启动内部时钟信号)。

2、等到VDD和VDDQ稳定后并且CKE设为高电平,应用稳定时钟。

3、等待200μs执行空操作命令。

4、precharge:预充电命令。SDRAM执行一条预充电命令后,要执行一条空操作命令,这两个操作会使所有的存储单元进行一次预充电,从而使所有阵列中的器件处于待机状态。引脚A10(=AP Auto Precharge)可以对预充电的模式进行选择,当A10=LOW时,给单个bank pre-charge,bank由BA0和BA1引脚进行选择;当A10=HIGH时,给所有的bank进行precharge。

5、auto-refresh:自刷新命令。SDRAM要执行两条自刷新命令,每一条刷新命令之后,都需要执行一条空操作命令。这些操作会使 SDRAM内部的刷新及计数器进入正常运行状态,以便为SDRAM模式寄存器编程做好准备。

6、load mode register:设置模式寄存器。Mode Register一般被用于定义SDRAM运行的模式,寄存器里一般设置了读取延迟,burst长度,CAS,burst类型,操作模式,还有是设置SDRAM是工作在单个读写操作还是burst操作下。Mode Register通过LOAD MODE REGISTER命令进行编程,这组信息将会一直保存在Mode Register中直到内存掉电之后才会消失。而这个寄存器的设置也是通过地址线来设置的,所以在发出Load Mode Register命令后要做一个操作是使得在SDRAM的地址线上的值就是你要设置的值。注意!这个操作是8位的操作。Mode Register中的M0-M2是用来定义突发长度(burst length)的,M3定义突发类型(sequential或者interleaved),M4-M6定义CAS延迟,M7和M8定义运行模式,M9定义写入突发模式(write burst mode),M10和 M11目前保留。Mode Register必须在所有的bank都处于idle状态下才能被载入,在所有初始化工组都进行完毕之前,控制器必须等待一定的时间。在初始化过程中发生了任何非法的操作都可能导致初始化失败从而导致整个计算机系统不能启动。

设置完模式寄存器之后就进入了正常读写操作模式。

图10SDRAM初始化

SDRAM的基本读写操作

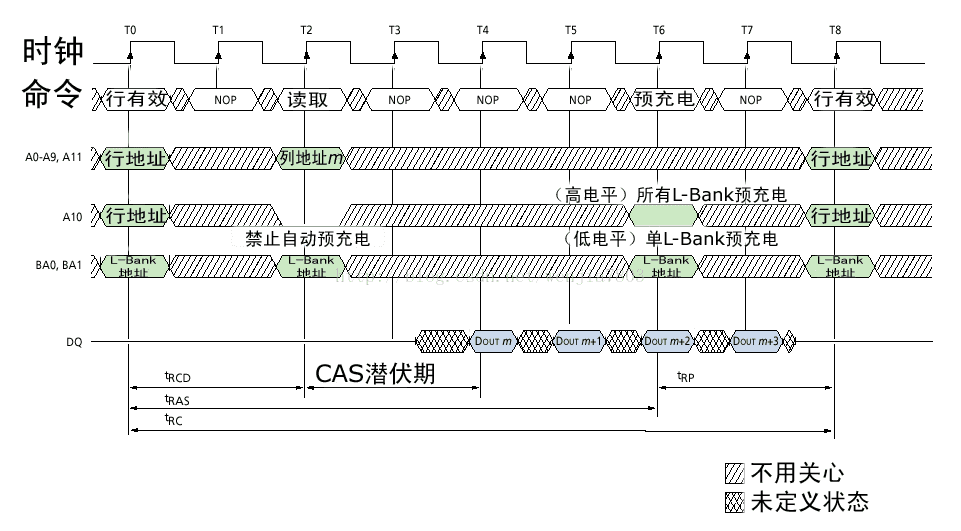

SDRAM的基本读操作需要控制线和地址线相配合地发出一系列命令来完成。先发出BANK激活命令(ACTIVE),并锁存相应的BANK地址(BA0、 BA1给出)和行地址(A0~A12给出)。BANK激活命令后必须等待大于tRCD(SDRAM的RAS到CAS的延迟指标)时间后,发出读命令字。CL(CAS延迟值)个工作时钟后,读出数据依次出现在数据总线上。在读操作的最后,要向SDRAM发出预充电(PRECHARGE)命令,以关闭已经激活的页。等待tRP时间(PRECHAREG命令后,相隔tRP时间,才可再次访问该行)后,可以开始下一次的读、写操作。SDRAM的读操作只有突发模式(Burst Mode),突发长度为1、2、4、8可选。

图11SDRAM基本读操作

SDRAM的基本写操作也需要控制线和地址线相配合地发出一系列命令来完成。先发出BANK激活命令(ACTIVE),并锁存相应的BANK地址(BA0、BA1给出)和行地址(A0~A12给出)。BANK激活命令后必须等待大于tRCD的时间后,发出写命令字。写命令可以立即写入,需写入数据依次送到DQ(数据线)上。在最后一个数据写入后延迟tWR时间。发出预充电命令,关闭已经激活的页。等待tRP时间后,可以展开下一次操作。写操作可以有突发写和非突发写两种。突发长度同读操作。

SDRAM刷新过程:

由于SDRAM是利用其内部的电容来存储数据,所以需要不断进行刷新(Refresh)才能保留住数据。刷新操作有固定的周期,以行为单位进行刷新,依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。与所有L-Bank预充电不同的是,这里的行是指所有L-Bank中地址相同的行,而预充电中各L-Bank中的工作行地址并不是一定是相同的。存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。这样刷新速度就是:行数量/64ms。刷新命令一次对一行有效,发送间隔也是随总行数而变化。

刷新操作分为两种:自动刷新(Auto Refresh,简称AR)与自刷新(Self Refresh,简称SR)。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。

对于AR,SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说CAS在RAS之前有效。所以,AR又称CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新过程中,所有L-Bank都停止工作,而每次刷新所占用的时间为9个时钟周期(PC133标准),之后就可进入正常的工作状态,也就是说在这9个时钟期间内,所有工作指令只能等待而无法执行。64ms之后则再次对同一行进行刷新,如此周而复始进行循环刷新。显然,刷新操作肯定会对SDRAM的性能造成影响,也是DRAM相对于SRAM(静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。

SR则主要用于休眠模式低功耗状态下的数据保存,这方面最著名的应用就是STR(Suspend to RAM,休眠挂起于内存)。在发出AR命令时,将CKE置于无效状态,就进入了SR模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在 SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

审核编辑 :李倩

-

控制器

+关注

关注

113文章

16518浏览量

180017 -

SDRAM

+关注

关注

7文章

434浏览量

55459

原文标题:FPGA学习-细说SDRAM控制器

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EE-178:ADSP-TS101S TigerSHARC片上SDRAM控制器

EE-127:ADSP-21065L片内SDRAM控制器

DDR4 SDRAM控制器的主要特点

PLC控制器的工作原理和运作方式详解

PID控制器与PWM控制器的区别

PID控制器与开关控制器的区别

测功机控制器测量仪详解

SDRAM控制器详解

SDRAM控制器详解

评论