有些应用中,需要降低Xilinx MPSoC的功耗。缺省设置中,R5/GPU都被使能。如果需要省电,可以在Vivado里关闭R5/GPU。步骤如下:

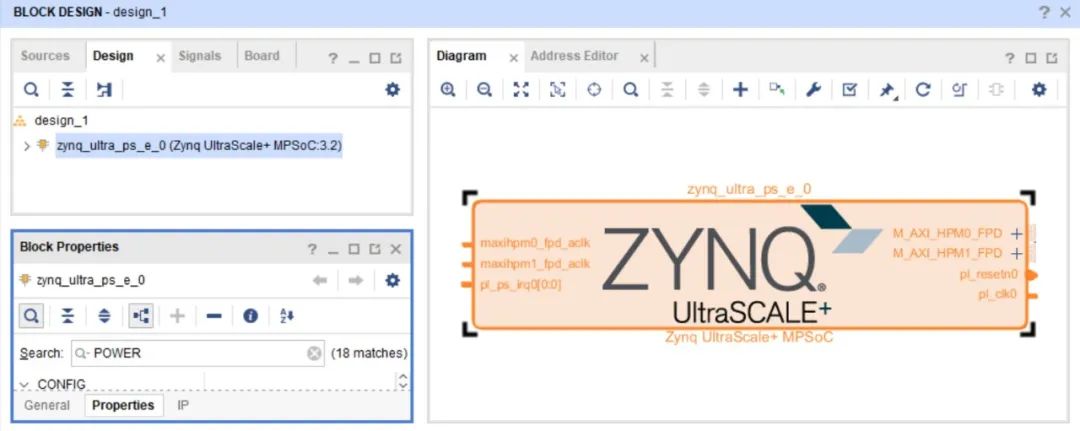

1.选中 MPSoC IP,在右键菜单中选择Block Properties.

2.在窗口Block Properties中,选择Properties.

3. 在窗口中,展开 “Config”.

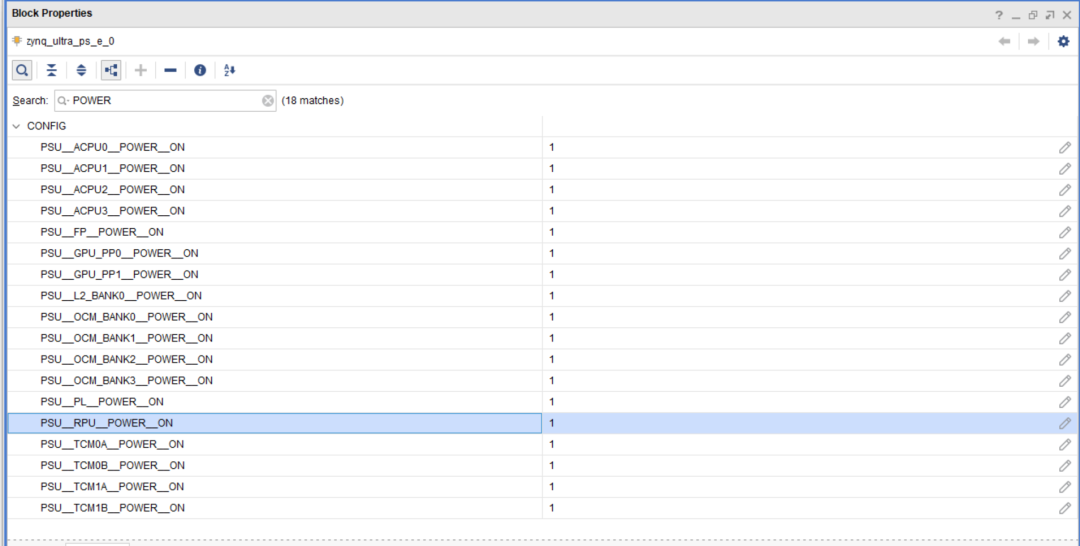

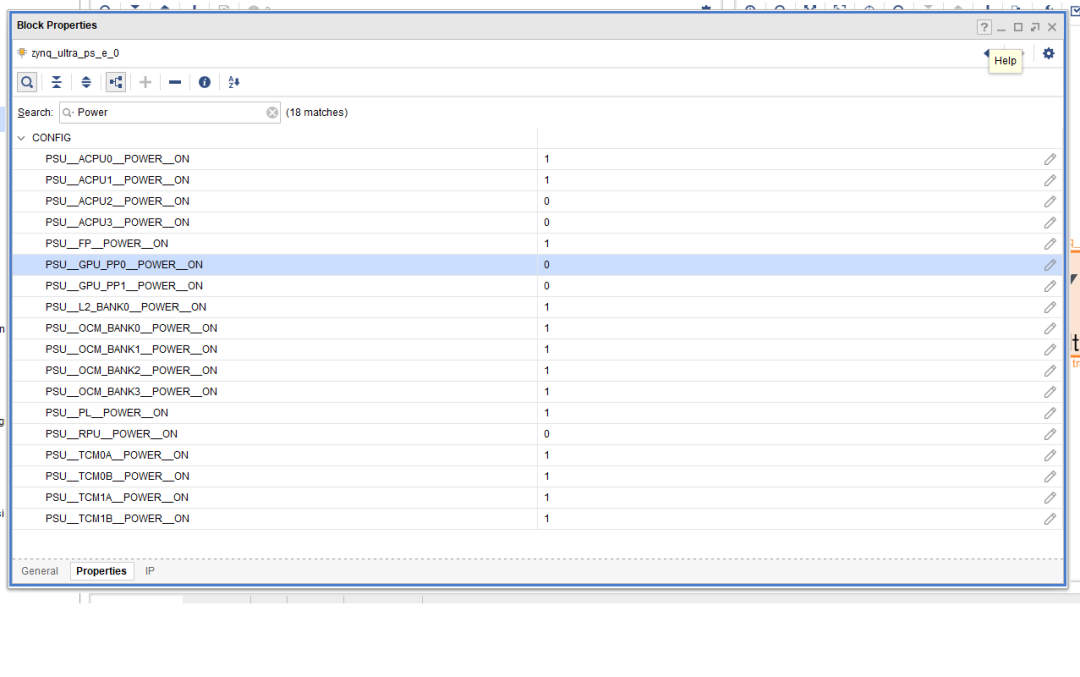

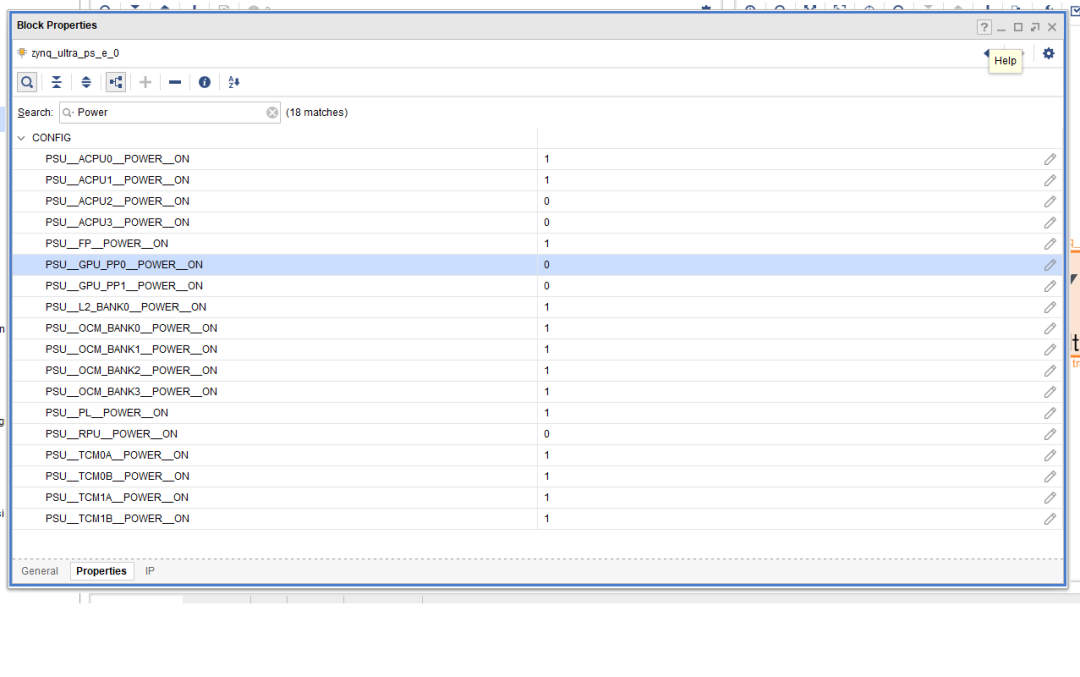

4. 在搜索框中输入 “Power”, 出现PSU_RPU_POWER_ON等选项。如果值是1,表示被使能;如果值是0,表示被关闭。如果要关闭,点击最左边的编辑图标,输入0。

编辑前Power选项

编辑后Power选项

在Vivado里编辑完成后,执行“Generate Output Products”, 在导出Hardware的HDF/XSA文件。

2. JTAG检查R5/A53状态

2. JTAG检查R5/A53状态

在SDK/Vitis里创建FSBL和Standalone程序,启动后,在XSCT命令后窗口下,检查R5/A53状态,可以看到设置为0的R5/A53的状态是No Power。

xsct% connect

tcfchan#2

xsct% target

1 PS TAP

2 PMU

3 PL

4 PSU

5 RPU (Reset)

6 Cortex-R5 #0 (No Power)

7 Cortex-R5 #1 (No Power)

8 APU

9 Cortex-A53 #0 (Running)

10 Cortex-A53 #1 (Power On Reset)

11 Cortex-A53 #2 (No Power)

12 Cortex-A53 #3 (No Power)

3. 代码

代码在psu_init.c里的函数psu_peripherals_powerdwn_data( )里。

/*

POWER DOWN REQUEST INTERRUPT ENABLE

/

/

Register : REQ_PWRDWN_INT_EN @ 0XFFD80218

Power-down Request Interrupt Enable for Dual_R5

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_RPU 1

Power-down Request Interrupt Enable for GPU PP0

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_PP0 1

Power-down Request Interrupt Enable for GPU PP1

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_PP1 1

Power-down Request Interrupt Enable for ACPU2

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_ACPU2 1

Power-down Request Interrupt Enable for ACPU3

PSU_PMU_GLOBAL_REQ_PWRDWN_INT_EN_ACPU3 1

Power-down Request Interrupt Enable Register. Writing a 1 to this locati

on will unmask the Interrupt.

(OFFSET, MASK, VALUE) (0XFFD80218, 0x0000043CU ,0x0000043CU)

/

PSU_Mask_Write(PMU_GLOBAL_REQ_PWRDWN_INT_EN_OFFSET,

0x0000043CU, 0x0000043CU);

/##################################################################### */

/*

POWER DOWN TRIGGER

/

/

Register : REQ_PWRDWN_TRIG @ 0XFFD80220

Power-down Request Trigger for Dual_R5

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_RPU 1

Power-down Request Trigger for GPU PP0

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_PP0 1

Power-down Request Trigger for GPU PP1

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_PP1 1

Power-down Request Trigger for ACPU2

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_ACPU2 1

Power-down Request Trigger for ACPU3

PSU_PMU_GLOBAL_REQ_PWRDWN_TRIG_ACPU3 1

Power-down Request Trigger Register. Writing a 1 to this location will t

rigger a power-down request to the PMU.

(OFFSET, MASK, VALUE) (0XFFD80220, 0x0000043CU ,0x0000043CU)

/

PSU_Mask_Write(PMU_GLOBAL_REQ_PWRDWN_TRIG_OFFSET,

0x0000043CU, 0x0000043CU);

/##################################################################### */

审核编辑 :李倩

-

gpu

+关注

关注

28文章

4694浏览量

128664 -

Vivado

+关注

关注

19文章

807浏览量

66303

原文标题:【干货分享】 在Vivado里关闭R5/GPU,降低Xilinx MPSoC的功耗

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TAS5710的PLL_FLTP和电源VR_ANA的电阻和电容的C9,R5,C10的值是怎么算出来的?

运放电路的反馈回路中的R4和R5是什么意思?

OPA1632负载接在了R3和R5中间,如何计算其传递函数?

采用OPA2377设计跨阻放大器,其中R5,R4,R6构成T型反馈回路,请问电容C4的作用是什么?

佳能EOS R5 Mark II相机配置:45MP堆栈式CMOS传感器+4K120p

超高性价比 ARM Cortex -A53教学实验箱快来提走

适用于ARM Cortex®—A53处理器和FPGA TPS65219 数据表

适用于 ARM Cortex®—A53 处理器TPS65219-Q1数据表

适用于ARM Cortex®—A53处理器A53处理器和FPGA的集成电源管理IC TPS65220数据表

适用于ARM Cortex®—A53处理器和 FPGA的集成电源管理IC TPS65220数据表

适用于ARM Cortex—A53处理器和FPGA TPS65219数据表

适用于ARM Cortex®—A53 处理器TPS65219-Q1数据表

适用于AM64x Arm®Cortex®-A53 处理器的TPS6521855 电源管理 IC数据表

Banana Pi [BPi-R3-Mini] 产品和主线 ImmortalWrt 固件支持

![Banana Pi [BPi-<b class='flag-5'>R</b>3-Mini] 产品和主线 ImmortalWrt 固件支持](https://file1.elecfans.com/web2/M00/B3/B3/wKgZomVoLcaANoFpAABnZ9wQ9hw885.png)

Vivado里关闭R5/A53/GPU

Vivado里关闭R5/A53/GPU

评论