芯片封装的发展趋势

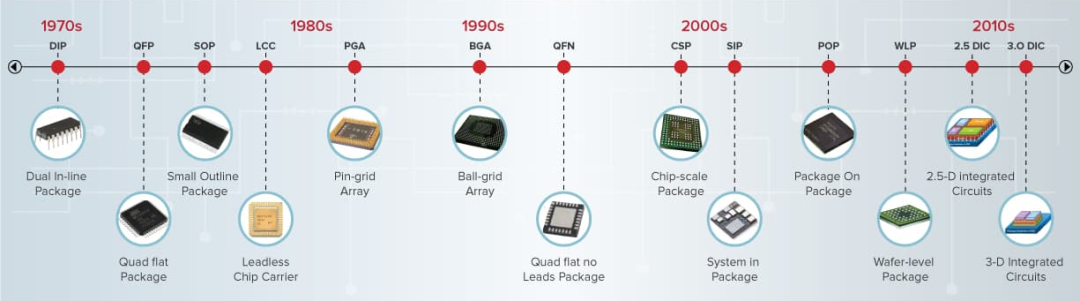

自1965年第一个半导体封装发明以来,半导体封装技术发展迅速,经历了四个发展阶段,已衍生出数千种不同的半导体封装类型。如图1所示这四个阶段依次为:(1)通孔直插时代,DIP封装工艺成熟、操作简单,虽然市场需求呈缓慢下降的趋势,但今后仍有巨大的市场空间;(2)表面贴装时代,两边或四边引线封装技术,如SOP、PLCC、QFP、QFN、DFN 等,此类封装已发展成熟,由于其引脚密度大大增加且可实现较多功能,应用非常普遍,未来总体规模将保持稳定;(3)面积阵列封装时代,封装技术如WLCSP、BGA、LGA、CSP 等,此类封装技术含量较高、集成度更高,市场处于快速增长阶段;(4)2.5D/3D封装时代,如Interposer、TSV、3DIC、INFO、SIP、MCM等先进封装技术,此类封装在提高封装密度和降低功耗方面有着优异表现,将迎来巨大的市场空间。

图1 芯片封装发展趋势

封装仿真设计挑战

封装技术的发展趋势主要向着高密度封装、高可靠性封装和低成本方向发展,而其封装的芯片工作频率越来越高、工作电压越来越低,致使封装的设计难度也越来越大,主要体现在信号完整性设计、电源完整性设计、电磁干扰设计、可靠性设计等,以下会分析其中最典型的三种设计挑战。

高速信号高精度通道建模的挑战

当信号工作频率较低时,由键合线、引脚、框架、焊球、传输线、过孔、焊盘等组成的互连结构只需使用简单的工具计算其集总参数就可完成整条通道的性能评估。随着信号工作频率的提高,信号在通道中传输表现出电磁波特性,工程师必须通过3D全波电磁仿真工具提取整条通道的S参数才能精确评估通道的性能。在当前的封装类型中,高速通道类型较多,比如高速SerDes接口,DDRx接口等,这些高速信号通道在封装内的结构具有走线密度大、结构复杂等特点。为了准确提取通道的S参数,仿真工具必需具有足够精准的求解引擎,同时还要具备任意三维结构的求解能力。

低电压大电流对电源完整性的设计挑战

芯片与系统高密度、小型化的发展需求,导致封装基板与PCB设计空间压缩,没有足够的空间留给电源通道,继而提升了压降和通流的风险。同时也没有足够空间布局去耦电容,信号更易受到电源干扰;其次,芯片与系统低功耗的发展需求,促使低电压、大电流的应用越来越普及,也带来了更大的DC压降和AC噪声;最后,信号速率的提高又要求更加稳定和干净的电源。以上问题都给电源完整性设计带来了极大的挑战,设计者必须借助先进的EDA工具对PDN系统进行精确的评估和优化,以保障系统正常运行。

封装与PCB的协同仿真挑战

通常情况下,封装设计和PCB设计是由两个团队独立完成的,这使得系统最后组装时,尽管封装和PCB都已经经仔细设计,但因为实际应用环境与前期设计环境的差异导致系统工作仍无法达到预期的效果。尤其是封装设计需要考虑多种因素,包括工艺、结构、材料、散热等,如何把握封装结构的各种寄生效应成为制约设计成功的关键因素,这需要准确地抽取封装结构的电气性能。一方面,芯片设计部门和系统设计部门会要求封装部门提供封装的电性能参数,如RLCG 或S 参数模型,结合封装寄生效应进行系统分析;另一方面,封装设计人员也需要根据芯片和系统分析的结果进行设计优化,对寄生效应做出必要的优化,从而最大限度地减少设计迭代,在有限的设计周期内完成高质量的设计。如果能够将封装文件和PCB文件统一到同一工程中进行优化设计,同时评估封装与PCB的综合性能,将有效提高设计仿真效率和产品迭代效率。

芯和半导体封装SI/PI仿真解决方案

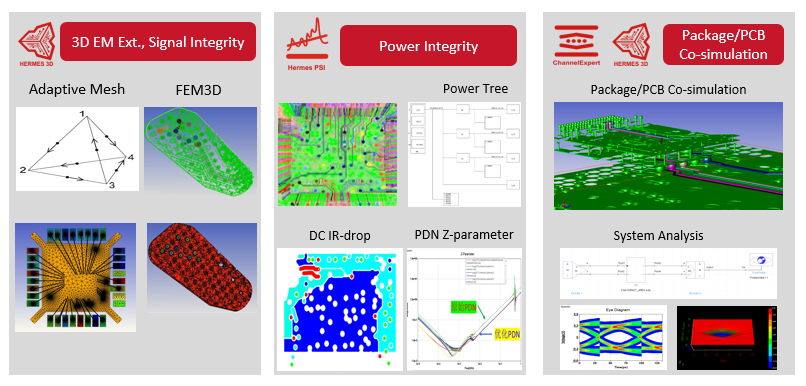

本文讨论的封装类型主要涵盖了基板封装(如FCBGA、PoP、FCCSP、FCLGA、WBBGA、WBLGA、SIP等)、引线框架封装(如QFN、QFP等)和晶圆级封装(如WLCSP、WLFO等)。芯和半导体的的封装SI/PI仿真解决方案包含了Hermes 3D和Hermes PSI两款EDA工具,可以准确提取封装内高速信号通道的S参数,可以准确评估封装内PDN系统的直接压降和交流阻抗,帮忙用户从信号完整和电源完整性两个维度精确评估封装性能。下面我们针对这三点进行深入地探讨:

图2 封装SI/PI仿真解决方案

高速信号通道S参数提取方法

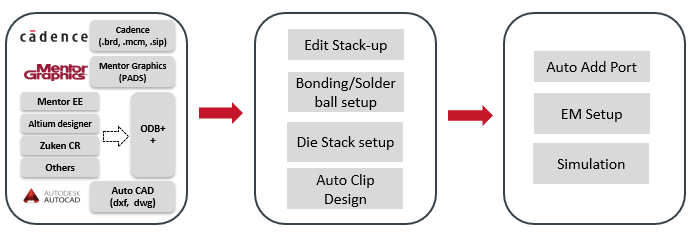

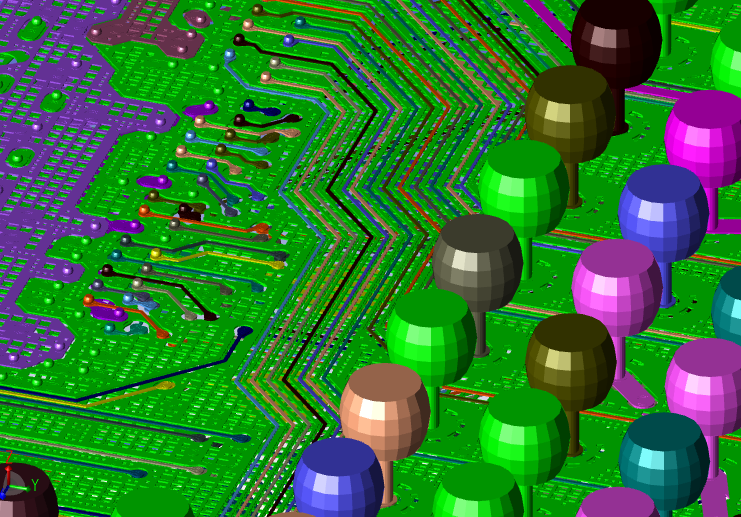

封装内高速信号通道存在焊球、键合线、引脚、框架等复杂结构,布线空间有限,通道内的参考平面不完整等因素,这些造成封装仿真建模难度大、电磁环境复杂的特点。芯和半导体的Hermes 3D是一款三维全波电磁仿真工具,它可以支持主流ECAD工具输出的版图文件自动导入,无需手动创建3D模型。针对模型切割和添加端口这两个操作,Hermes 3D都提供的自动流程大幅提高了工程师的建模效率。Hermes 3D采用自适应网格剖分技术和有限元算法,可以确保对任意三维结构在任意频段都具备较高的求解精度。

图3 Hermes 3D S参数提取流程

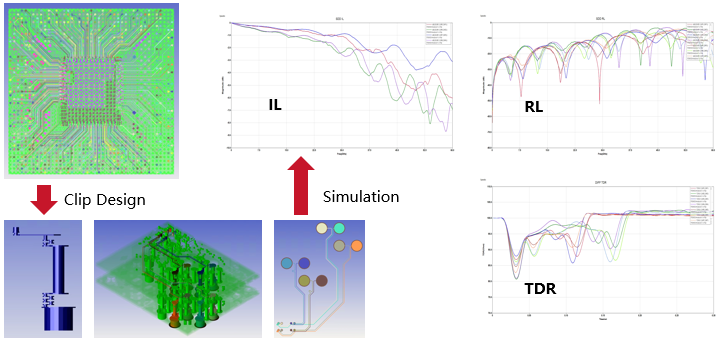

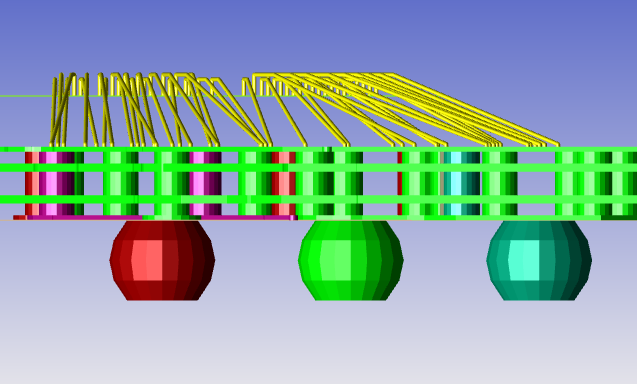

图4是以FCBGA封装中的PCIE接口为例,对高速信号通道S参数提取方法做详细展示。本次案例提取4对PCIE走线,提取频段设置为0~60GHz。

图4 FCBGA PCIE接口仿真示例

另外,WBBGA封装、晶圆级封装和框架类封装的高速信号通道S参数提取案例如图5、图6和图7所示。

图5 WBBGA封装建模仿真示例

图6 INFO封装建模仿真示例

图7 QFN封装建模仿真示例

封装电源完整性评估方法

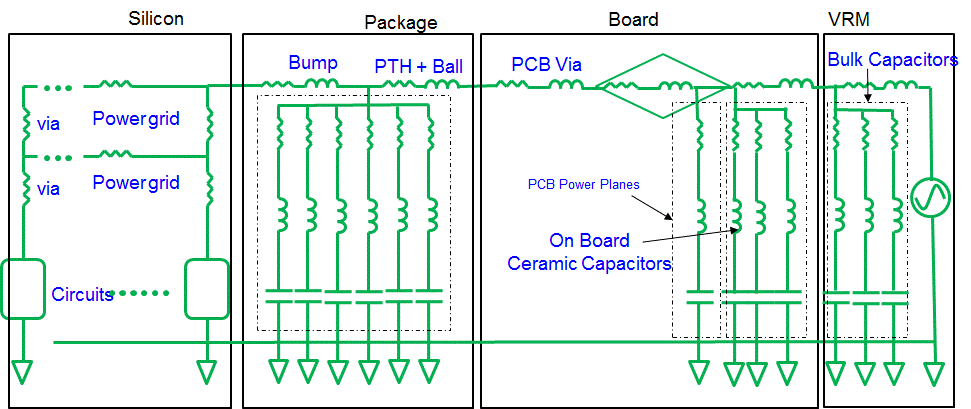

稳定、干净的电源是芯片工作的基本保障。在实际电路中,电源走线、地走线、去耦电容等构成的PDN网络,由于其自身RLC寄生参数的存在,会产生直流压降与交流噪声。图8 显示了一个完整PDN网络模型,在整个PDN网络中,芯片、封装、PCB、VRM都会影响PDN的性能。PDN网络优化是一个系统工程,通常兆赫兹级别的去耦由PCB上的Bulk电容和陶瓷电容来负责,百兆赫兹频段的去耦由封装基板的滤波电容来负责,吉赫兹以上的高频噪声去耦由芯片内部负责。

图8 PDN网络模型

芯和半导体的Hermes PSI是一款专注封装与板级电源完整性分析的工具,包括直流压降分析和交流阻抗分析两大功能模块。直流压降分析可以供工程师快速分析电源的直流效应,以检查直流电压降、电流走向及电流密度分布情况,优化电源路径中可能存在的瓶颈。交流阻抗分析可以计算封装基板与PCB的PDN阻抗,自动优化去耦电容。

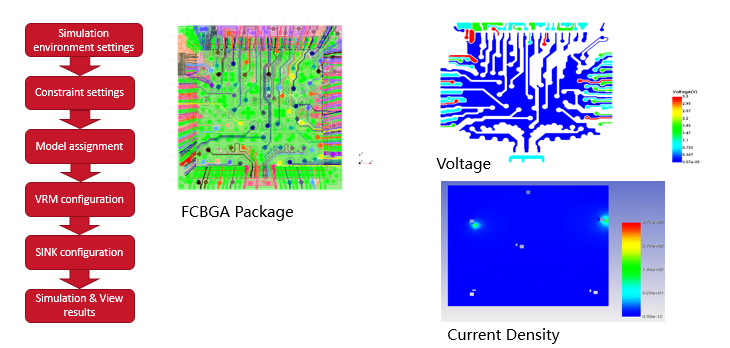

图9是使用Hermes PSI对FCBGA封装基板进行直流压降分析的完整流程和仿真结果。

图9 封装基板直流压降分析流程

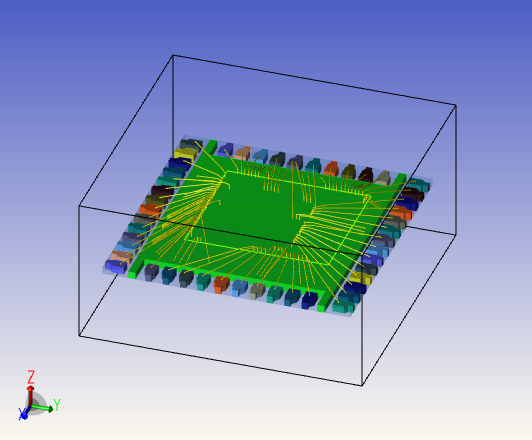

封装与PCB协同仿真方法

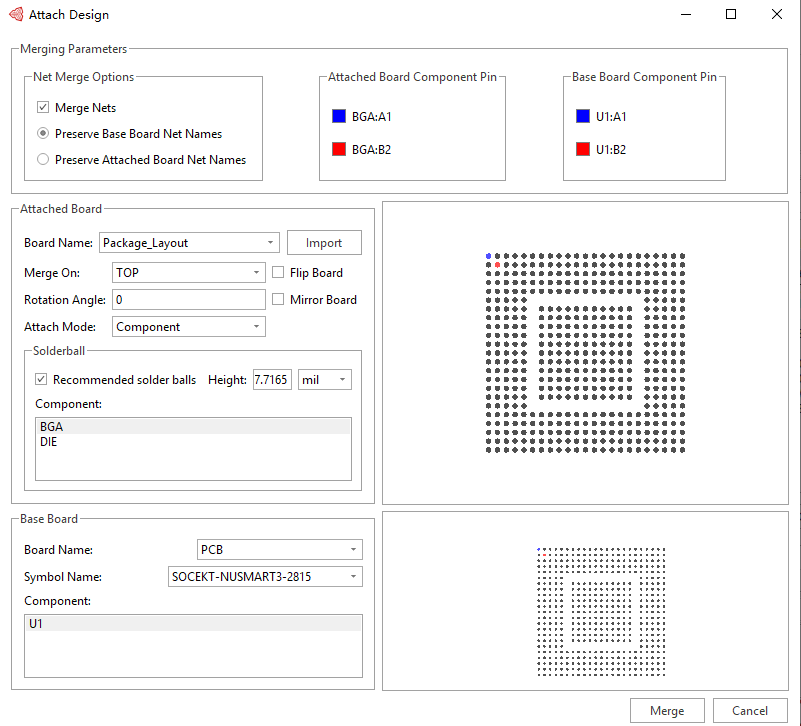

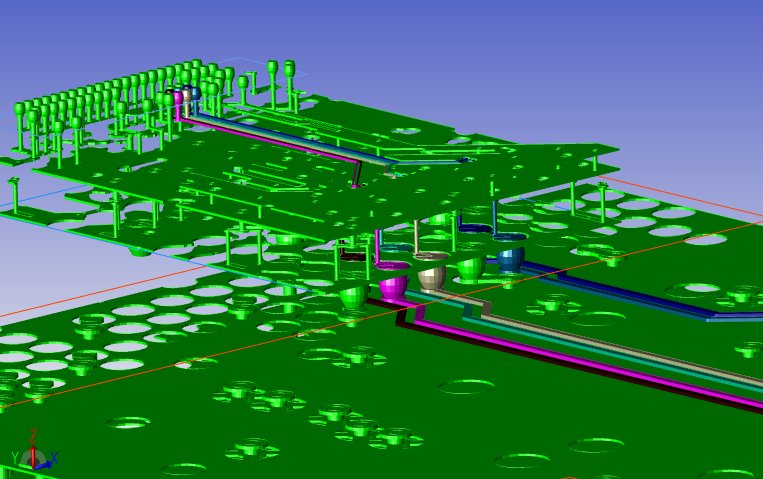

Hermes 3D可以将封装基板文件和PCB文件同时导入。设计者通过Attach Design流程,如图10,将仿真文件与PCB文件通过焊球连接,创建完整的通道模型。工程师可以同时评估封装和PCB的电气性能,使得仿真环境更加接近真实的系统应用环境。

图10 封装与PCB协同建模

图11 封装与PCB协同仿真示例

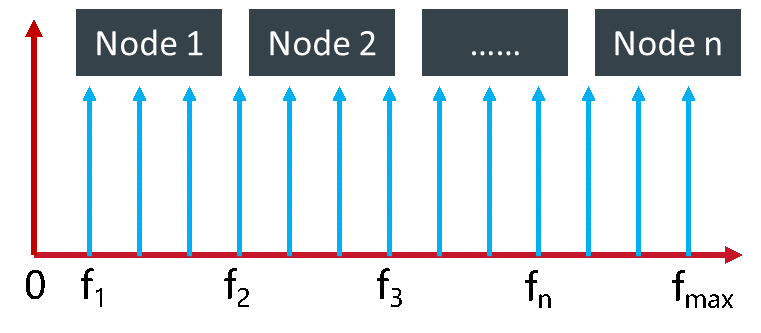

另外,封装与PCB放在同一个系统来仿真,必然带来计算量激增,仿真周期将会被拉长。在Hermes 3D中,仿真支持多机多核并行求解技术,该技术将宽带扫频频点分配到多个处理器或计算机求解,自动生成扫频结果,减少了宽带频域求解的总仿真时间,大幅提高仿真效率。

图12 频谱分解技术

总结本文从封装的发展趋势入手,介绍了封装仿真设计时所面临的多种挑战,即高速信号高精度通道的建模挑战,低电压大电流对电源完整的设计挑战,封装与PCB的协同仿真挑战。芯和半导体针对这些挑战提供了一套完整SI/PI仿真解决方案:Hermes 3D借助自适应网格剖分和有限元算法这两大核心技术可以准确提供封装内高速信号通道的S参数;Hermes PSI集成直流压降分析模块和AC阻抗分析模块可以有效应对低电压大电流场景的电源完整性评估与优化;为了使仿真场景更加贴近系统实际应用场景,Hermes 3D可以同时导入封装基板文件和PCB文件进行协同仿真,HPC技术的加持可以大幅提高Hermes 3D求解大模型的能力。

原文标题:【解决方案】封装SI/PI仿真解决方案

文章出处:【微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

封装

+关注

关注

127文章

7954浏览量

143135 -

仿真设计

+关注

关注

3文章

95浏览量

16827 -

芯和半导体

+关注

关注

0文章

108浏览量

31448

原文标题:【解决方案】封装SI/PI仿真解决方案

文章出处:【微信号:Xpeedic,微信公众号:Xpeedic】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

封装设计与仿真工具现状及发展趋势

TPMS技术与发展趋势

PCB发展趋势,六大趋势

集成电路的发展趋势与设计挑战

SiP(系统级封装)技术的应用与发展趋势

先进封装技术的发展趋势

嵌入式芯片封装发展趋势解析

Multicom发展趋势如何?它面临哪些挑战?

嵌入式芯片封装的发展趋势是什么

一文知道封装测试行业发展趋势

嵌入式芯片封装发展趋势解析

芯片封装的发展趋势 封装仿真设计挑战及解决方法

芯片封装的发展趋势 封装仿真设计挑战及解决方法

评论