节能举措,如企业服务器和云数据中心电源的“80+ Titianium”,以及外部电源适配器的欧盟行为准则(CoC) Tier 2,正使电源设计人员转而选择GaN开关技术,以实现更高能效的设计。由于GaN并不是现有硅技术的直接替代品,为了获得最大的优势,驱动器和布板必须与新技术相匹配。

对比GaN和硅开关

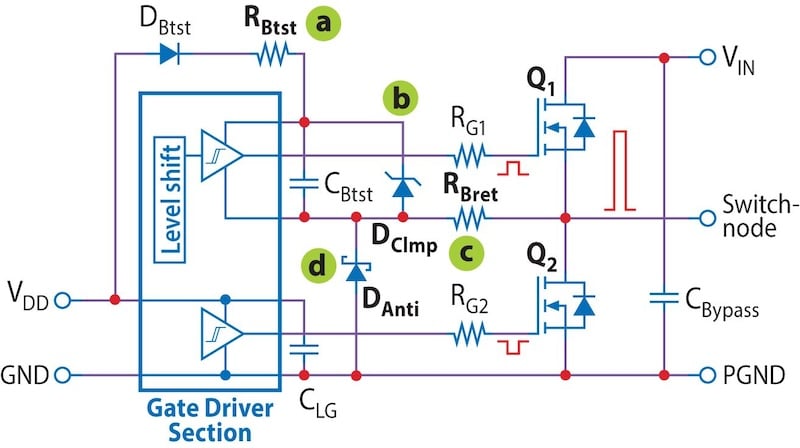

GaN是高速器件,因其电容很低,且可在没有反向恢复电荷的情况下反向导电(第三象限),这在硬开关应用中是个真正的优势。因此,损耗较低,但也有一些缺点。一是器件没有雪崩电压额定值,门极驱动相当关键,绝对最大额定电压典型值仅为+/-10V,而Si器件为+/-20V。另外,增强型(E-mode)GaN通常是关断的器件,其1.5V左右的门极导通阈值也低于Si的约3.5V。关键的是,能否实现低损耗、高功率密度和高可靠性的预期优势,取决于具有强固保护特性的优化门极驱动电路。

GaN门极驱动对性能至关重要

为了充分增强,E-mode GaN开关需要驱动到约5V,但不很高;除了保持在绝对最大限值内,门极电路中的功耗随门极驱动电压和频率的变化而变化。在器件电容和门极电荷较低的情况下,平均驱动功率可以很低。但由于开关是纳秒级的,峰值电流可以很高,为安培级,因此驱动电路需要匹配这速度,但仍然能够提供大量的电流。

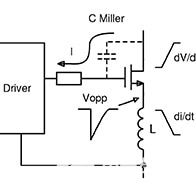

理论上,GaN器件在VGS= 0安全关断,但是如果没有从驱动器返回到开关源的闭合“开尔文”连接,则所得到的连接电感在器件开关时引起电压尖峰(图1)。这与门极驱动器相对,最佳地降低驱动电压裕量,和最坏的导致寄生导通从而具有潜在的破坏性结果。门极可负驱动以抵消效应,但是通过谨慎的布局和便于开尔文连接的驱动器可以避免这种复杂性。“Miller”电容可引起类似的效应,但对于GaN,这可忽略不计。

图1:源极和门极驱动共有的电感会引起电压瞬变

高边门极驱动的挑战

一些转换拓扑采用‘高边’开关,其门极驱动器返回是高压开关节点。驱动器必须电平移位,并且不受从输出到输入的dv/dt影响,对于GaN,dv/dt可能是100 V/ns以上。此外,在这种情况下,需要很好的控制通过驱动器的传播延迟,以便匹配低边和高边信号,避免发生灾难性的“击穿”,同时尽可能保持最小的死区时间。甚至低边驱动器有时也需要信号和接地电源之间一定的电平移位,以避免从驱动器输出级到输入端的噪声耦合,这耦合可能会导致异常运行或最坏的设备故障。

有源钳位反激应用示例

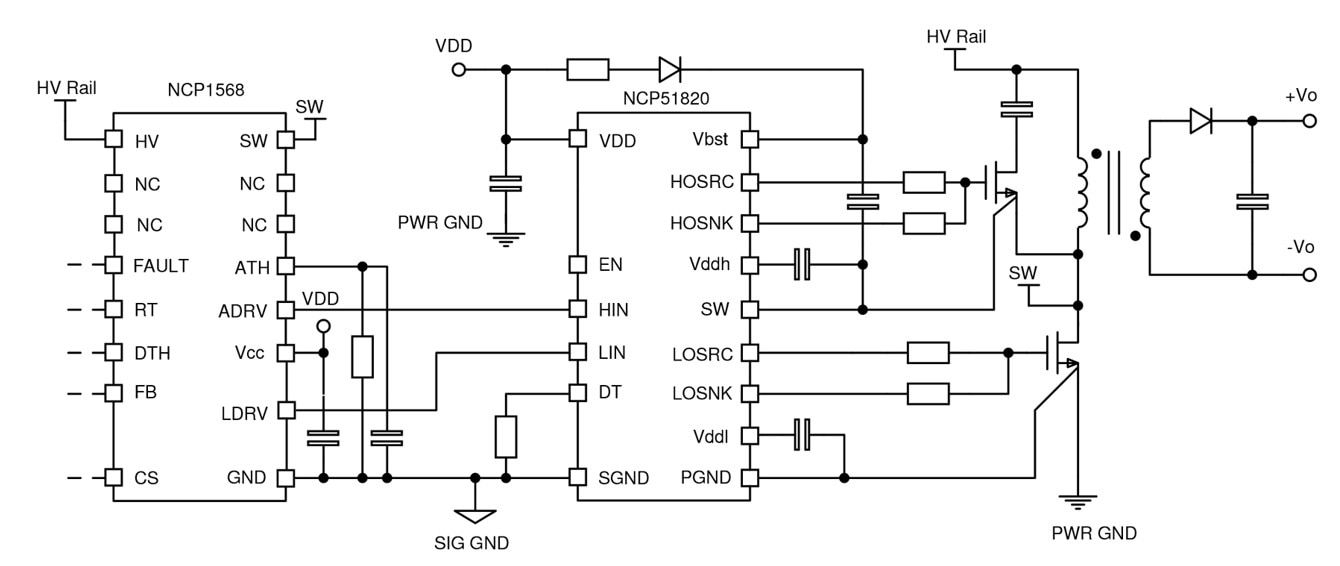

图2:GaN有源钳位反激转换器概览

图2显示安森美半导体的NCP51820 GaN门极驱动器及NCP1568有源钳位反激控制器。该驱动器采用具有调节的+5.2V幅值的门极驱动器用于高边和低边输出最佳增强型GaN。其高边共模电压范围-3.5V到+650V,低边共模电压范围为-3.5至+3.5V,dv/dt抗扰度200 V/ns,采用了先进的结隔离技术。如果在低边器件源极有一个电流检测电阻器,低边驱动电平移位使开尔文连接更容易。驱动波形的上升和下降时间为1ns,最大传播延迟为50 ns,且提供独立的源汲输出,以定制导通和关断边沿率,达到最佳的EMI/能效。

LLC转换器应用示例

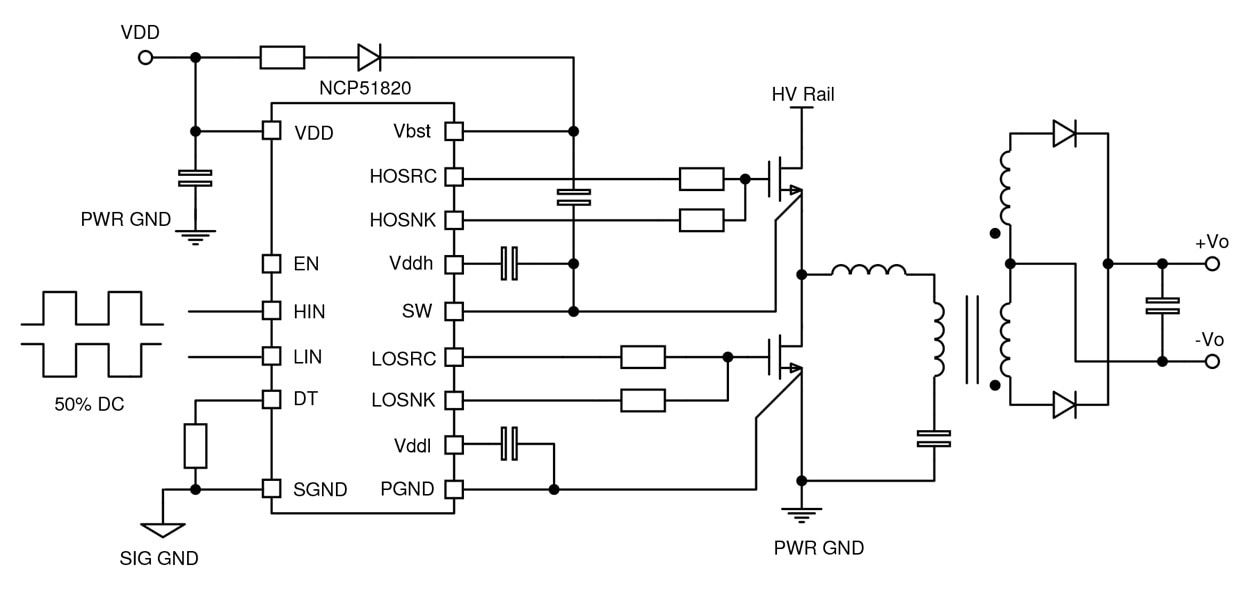

该LLC转换器(图3)的一个特点是驱动波形为50%的占空比。因此,控制死区时间以不发生重叠至关重要。

图3:基于GaN的LLC转换器概览

所示的安森美半导体NCP51820驱动器确保门极驱动不重叠。该器件还含一个使能输入和全面的保护,防止电源欠压和过温。它采用PQFN、4×4mm 的15引线封装,使短、低电感连接到GaN器件的门极。

布板至关重要

在所有应用中,布板是成功的关键。门驱动回路必须最小化和匹配,驱动器和GaN器件应置于PCB同侧,并使用接地/电源面。

对于GaN开关,需要仔细设计其门极驱动电路,以实现更高能效、功率密度及可靠性。此外,谨慎的布板,使用专用驱动器如安森美半导体的NCP51820,及针对高低边驱动器的一系列特性,确保GaN器件以最佳性能工作。

审核编辑:郭婷

-

驱动器

+关注

关注

52文章

8236浏览量

146357 -

控制器

+关注

关注

112文章

16361浏览量

178031 -

安森美半导体

+关注

关注

17文章

565浏览量

61001

发布评论请先 登录

相关推荐

用UCC27611搭建的驱动GaN FET电路,FET的Drain极加电时,UCC27611输出端检测到干扰波,为什么?

纳芯微提供全场景GaN驱动IC解决方案

晶闸管电路对门极信号有什么要求

限幅电路利用了二极管的什么特性

Power Integrations推出SCALE-iFlex XLT系列门极驱动器

Power Integrations推出SCALE-iFlex XLT系列双通道即插即用型门极驱动器

调整MOSFET栅极驱动器以用于GaN FETs

适配MOSFET栅极驱动器以驱动GaN FETs

通过GaN特性优化门极驱动电路

通过GaN特性优化门极驱动电路

评论