逐次逼近寄存器模数转换器 (SAR-ADC) 通常是中等分辨率应用的首选架构。市场上的 SAR 产品可以在高达几兆赫兹的最大采样率下运行。然而,设计人员将其应用需求与速度慢得多的 SAR-ADC 相匹配,以努力降低成本和布局问题。在市场上,SAR-ADC 的分辨率范围从 8 位到 18 位。

这种类型的设备外形小巧,功耗低,这对于电池供电的应用至关重要。在本文中,我们研究了 SAR-ADC 的内部工作原理和转换器的驱动器要求。

SAR-ADC 的工作原理

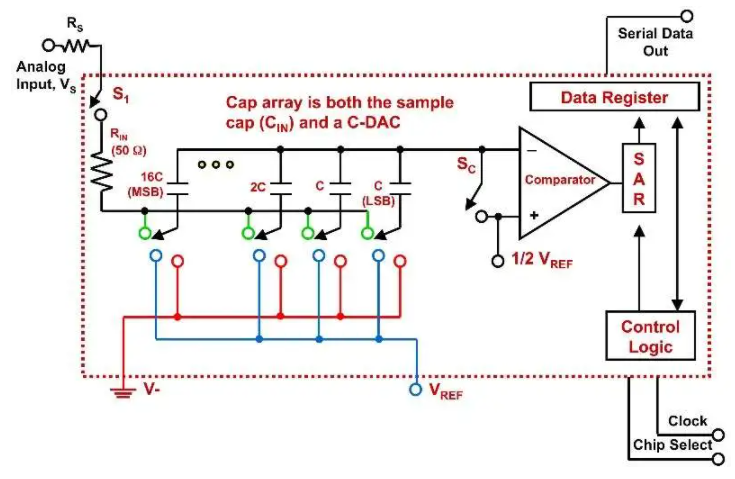

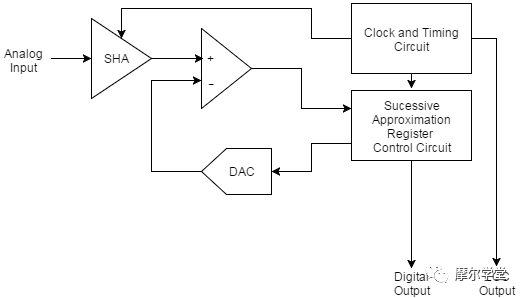

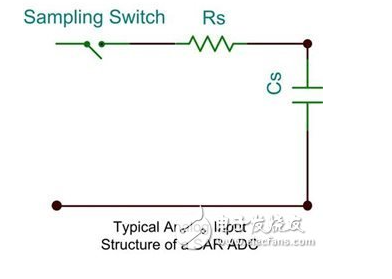

SAR-ADC(图 1)捕获模拟电压信号,将该信号转换为数字字。模拟信号由外部采样/保持设备或 SAR-ADC 的内部采样/保持功能捕获。SAR-ADC 将此输入电压与转换器外部或内部参考电压 (VREF) 的已知部分进行比较。该基准设置转换器的满量程输入电压范围。现代 SAR-ADC 使用电容式数模转换器 (C-DAC) 来连续比较位组合并将适当的位设置或清除到数据寄存器中。

图 1. 这是现代 SAR-ADC 16 位转换器的内部采样机制模型。在 VS 处获取信号后,片选从高电平变为低电平并打开输入开关 (S1)。

在 SAR 转换器的输入端,输入信号首先经过一个开关。请注意,闭合开关会产生与电容阵列串联的开关电阻 (RIN)。这些电容器的顶部连接到比较器的反相输入。底部可以连接到输入电压、电压参考 (VREF) 或接地 (V–)。最初,底部连接到输入信号 VS。一旦电容阵列完全获取输入信号,输入开关 (S1) 打开,转换器开始转换过程。

在转换过程中,MSB 电容器的底部连接到 VREF,而其他电容器连接到 V–(或系统接地)。这个动作在所有电容器之间重新分配电荷。比较器的反相输入根据电荷平衡上下移动电压。如果 SC 上的电压大于 VREF 的一半,则转换器将“0”分配给 MSB,并将该值从串行端口发送出去。如果该电压小于 VREF 的一半,转换器从串行端口发送一个“1”,转换器将 MSB 电容器连接到 V–。在 MSB 分配之后,此过程对 MSB-1 电容器重复。请注意,图 1 未显示 MSB-1 电容器,但其值为 8C。

发生 SAR-ADC 转换过程所需的时间包括采集时间和转换时间。在整个转换过程结束时,SAR-ADC 进入睡眠模式。

驱动您的 SAR-ADC

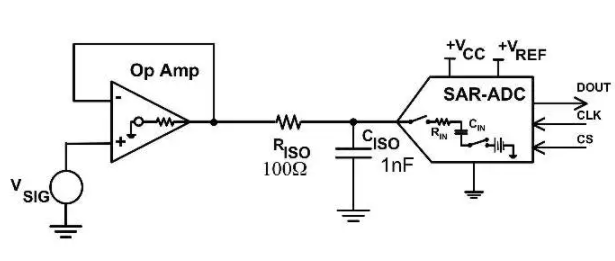

图 2中优化的 ADC 驱动器电路 使用运算放大器 (op amp) 将 SAR-ADC 与高阻抗输入源 VSIG 分离。以下 R/C 低通电路(RISO 和 CISO)执行返回运算放大器并转发到 SAR-ADC 的功能。RISO 通过将放大器的输出级与 CISO 隔离来保持放大器的稳定。CISO 为 SAR-ADC 提供了一个近乎完美且稳定的输入源。该 CISO 跟踪电压的输入信号,并在转换器的采集时间内提供适当的 SAR-ADC 电荷。

图 2. SAR-ADC 应用设计需要一个驱动电路(运算放大器、RISO 和 CISO),以确保 ADC 在转换器的采集期间具有稳定的输入信号。

在设计 SAR-ADC 电路时,首先要确定输入信号的带宽和满量程范围。然后,您选择的 SAR-ADC 应该与每个 nyquist 的输入信号带宽相匹配。该转换器还应具有适合您系统的分辨率。在本设计中,关键的 SAR-ADC 规格是电容阵列的累积值 CIN(相当于 SAR-ADC 的输入电容)、转换器的满量程输入范围和采集时间 (tAQU)。

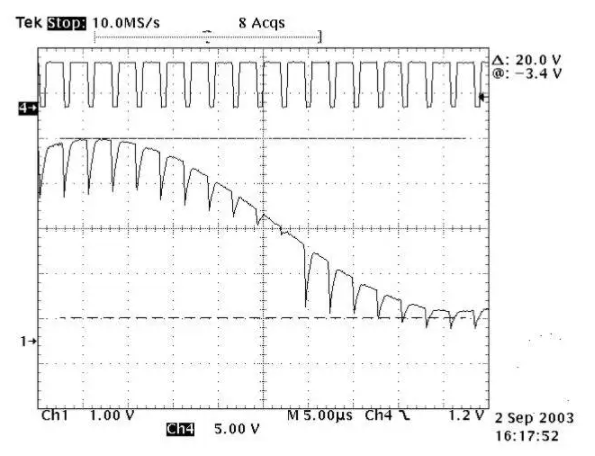

现在我们继续通过确定它们的值来定义 RISO 和 CISO。图 3 的示波器捕获显示了 SAR-ADC (ADS8326) 的输入电荷注入瞬态。在此测量中,放大器缓冲器和 SAR-ADC (Ch1) 之间有一个 10 kOhm 电阻。开始转换或片选信号出现在顶部曲线 (Ch4) 上。请注意,提供给 SAR 转换器的输入阻抗绝不应该高达 10 kOhm?但这让我们可以看到这个 SAR-ADC 输入端的高频电流尖峰。

图 3. 10 kOhm 电阻器捕获 16 位 SAR-ADC (Ch1) 输入处的电荷注入幅度。CS 引脚启动每次发生的杂散,杂散发生在 ADC 的采集周期 (Ch4)。

SAR-ADC 输入处的电荷注入发生在转换器获取输入信号时。这些高频尖峰对驱动运算放大器提出了非常苛刻的负载。

如图1 所示,SAR 转换器很少有内置输入缓冲放大器。该电路需要一个具有无失真、轨到轨输入级的运算放大器(请参见 OPA364 数据表,第 8 页)。该放大器的输出级跨度为正电源以下 100 mV 至 100 mV。

RISO 和 CISO(图 2)的功能是为这种电荷注入提供一个到地的路径,并将运算放大器的输出与这些瞬态隔离。RISO 和 CISO 有效地完成了将放大器与容性负载隔离并从 SAR-ADC 吸收电荷尖峰的任务。然而,这两个组件也会改变放大器的开环增益响应,如波特图所示。

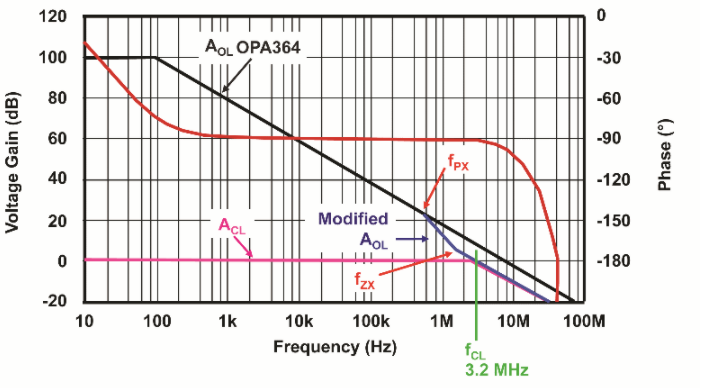

图 4 显示了一个示例运算放大器,该系统的波特图。查看左侧 y 轴如何绘制放大器的开环和闭环增益。右侧 y 轴绘制放大器的开环相位响应。x 轴绘制频率。

图 4. 带有 RISO|CISO 负载的 OPA364 开环增益/相位与频率的关系。

该放大器 (OPA364) 的开环增益曲线在 10 Hz 时具有 100 dB 的增益。随着频率的增加,该增益曲线(~100 Hz)变为 –20 dB/decade 的斜率。该斜率一直持续到曲线持续超过 0 dB。开环增益曲线与 0 dB 的交点处的频率为 7 MHz。

当外部电路 (RISO|CISO) 加载放大器时,会修改开环增益曲线。在图 4 中,蓝色曲线代表修改后的开环曲线。RISO 和 CISO 以及放大器的输出电阻在 fPX 处产生一个极点,在 fZX 处产生一个零点。如图 4所示,RISO 和 CISO 的极点出现在 769 kHz,而零点出现在 1.6 MHz。这条修改后的开环增益曲线的斜率从 –20 dB/decade 变为 –40 dB/decade 斜率,fPX 变为 –20 dB/decade 斜率,fPZ 在 1.6 MHz 为零。

电路稳定性定义在开环增益曲线和闭环增益曲线的交点 (3.2 MHz)。在这个交点处,如果这两条曲线的斜率之差为 20 dB/decade,则放大器将是稳定的。如果这些斜率之间的差异大于 20 dB/decade(例如,40 dB/decade),则放大器电路将略微稳定。

为了尽量减少内部采样电容的非线性效应,以及尽量减少电荷注入对输入电压的影响,最小 CISO 值是内部 SAR-ADC 采样电容大小的 20 倍。通过注意这个 R|C 电路必须在转换器的采集时间内完全稳定,可以找到 RISO 值。

结论

这是对 SAR-ADC 输入结构和模拟驱动级设计策略的快速概述。SAR-ADC 的输入结构在转换器的采集时间内等于采样电容阵列。为了确保输入信号在采集期间保持稳定,一种有效的设计策略是在放大器的输出和转换器的输入之间放置一个 R|C 对。

参考

1.“外部组件提高 SAR-ADC 精度”,Baker,Oljaca,EDN,2007 年 6 月 7 日。

2.“在驱动 SAR ADC 时从正确的运算放大器开始,”Oljaca,Baker,EDN,2008 年 10 月 16 日

。3 。 下载这些数据表:OPA364、ADS8361。

关于作者

Bonnie Baker是德州仪器 (TI) Webench 团队的高级应用工程师,从事模拟和数字设计及系统工作超过 25 年。她撰写了数百篇文章、设计和应用说明、会议论文,并撰写了一本书:“A Baker‘s Dozen: Real Analog Solutions for Digital Designers”。

-

运算放大器

+关注

关注

218文章

6470浏览量

181893 -

模数转换器

+关注

关注

26文章

4104浏览量

130258

发布评论请先 登录

为什么使用24位转换器来替代多个12位器件

基于SAR-ADC架构的此类系统的实现需求

根据系统和技术选择转换器

解析SAR-ADC 的内部工作原理和转换器的驱动器要求

解析SAR-ADC 的内部工作原理和转换器的驱动器要求

评论