作者:一博科技高速先生 姜杰

Layout组有个雷工,大家叫他老雷,尽管画板多年阅板无数,但还是被SI同事给出的DDR4信号优化建议整懵圈了;SI组也有个雷工,大家叫他小雷,尽管初出茅庐时默默无闻,但是在他优化的这版一驱九DDR4稳定运行在3200Mbps后,他将被尊称为豹哥。

一驱九DDR4设计一直是行业公认的难点,尤其是板载颗粒的方案,当然,具体难度也因板而异。不幸的是,两位雷工这次遇到的是个硬骨头,不光是板载颗粒设计,还是个改板,之所以改板,原因很简单,之前的板子DDR4数据信号没有达到3200Mbps的预期速率。 客户反馈前一版本已经可以跑到2933Mbps, 改板的需求也很简单,就是能稳定运行到3200Mbps,毕竟,上一版离目标速率也就差那么一点点。

与客户的乐观不同,小雷觉得事情可能不像预期的那么容易。可以判断的是,上一版是裕量不足导致的marginal fail,问题是,从2933Mbps到3200Mbps,这点看似不起眼的裕量去哪找?

熟悉高速先生文章的朋友一定还记得,一驱多DDRX,难点往往不在速率较高的数据信号,而在于速率只有数据信号一半的地址控制类信号,原因这里再解释哈:数据信号一般都是点到点的拓扑,而且大多有片上端接(ODT),走线拓扑简单,又有端接,信号想跑不起来都难;地址控制类信号的处境就难多了,难就难在一驱多的走线拓扑对信号的影响太大,即便速率相比数据信号减半。

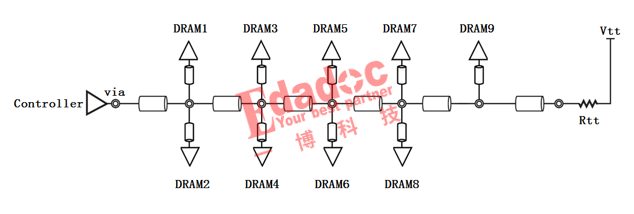

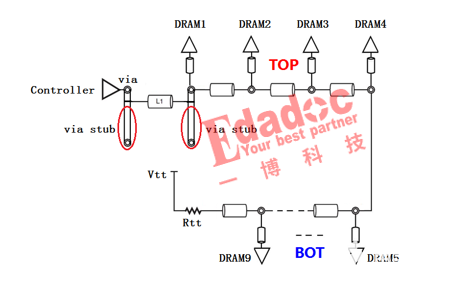

小雷也深知这一点,所以上一版数据信号跑不到3200Mbps,大概率是因为DDR4的地址控制类信号达不到1600Mbps,于是查板从此类信号入手,上一版的走线拓扑为Clamshell,看不懂单词没关系,画出来你就秒懂了:

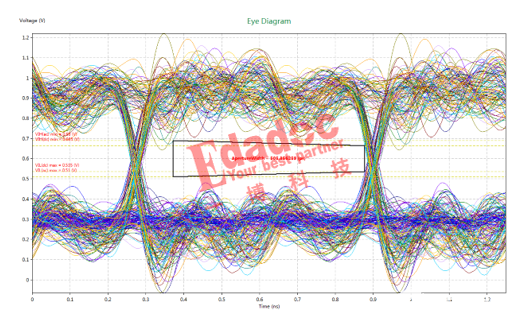

对于空间受限的单板而言,一驱九DDR4选择这个拓扑也算合理。Clamshell拓扑可以认为是Flyby拓扑和T拓扑的组合,所以既有Flyby拓扑的特点,也就是近端颗粒的信号质量特别差;也有T拓扑的特点,近端的DRAM1和DRAM2一样差。小雷的仿真结果也验证了这一点,上一版近端颗粒的眼图(地址信号速率1600Mbps)确实在Pass和Fail的边缘疯狂试探,无怪乎压力测试速率总是差那么一点点。

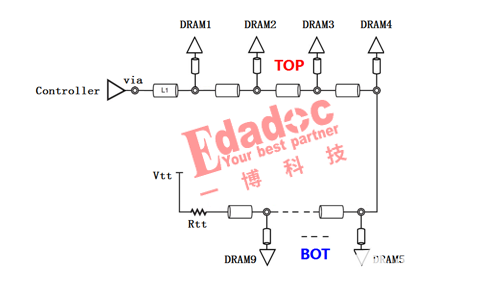

令人沮丧的是,无论小雷如何调整Clamshell拓扑参数,近端颗粒的信号质量始终不见改善,看来前一版的设计也是下过功夫的。关键时刻,客户提供了另外一个信息:同样的主控芯片,在板载颗粒方案之前,有过DIMM条成功的案例,当时的DIMM条上的DDR颗粒采用Flyby拓扑,设计如下:

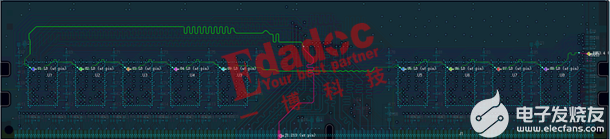

苦无良方的小雷决定照葫芦画瓢,让老雷把板载颗粒也改为Flyby拓扑试试,不过,由于单板空间不像DIMM条充足,板载DDR芯片需要双面布局,调整后的地址信号拓扑如下:

老雷不愧设计老炮儿,三下五除二把板子改了出来,除了因空间受限与DIMM条的布局无法做到一样,DDR信号的各段走线长度、阻抗控制都与DIMM条保持一致,还很贴心了调整了信号走线层,让过孔stub尽量短。

小雷查板之后相当满意,老雷得到认可后也很得意,甚至自信满满的与客户确定了投板日期,万事俱备,只欠仿真验证了。

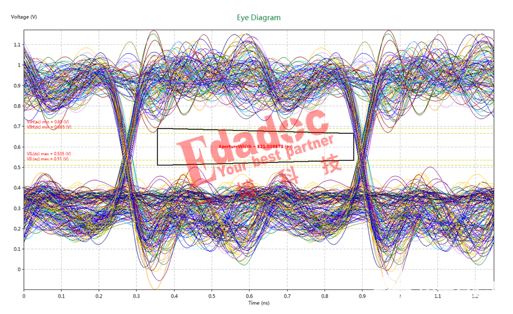

调整为Flyby拓扑的板载颗粒方案仿真结果居然又翻车了,近端颗粒信号质量略有改善,但是仍没达到预期效果:

小雷迷茫了,目前的仿真结果显然无法支持数据信号稳定运行到3200Mbps。拓扑、走线、阻抗都控制的和DIMM一毛一样,为啥结果还差着一截?

一定是漏了什么?小雷对着DIMM条和板载设计的Flyby一点点的排查,功夫不负有心人,经过一整天的对比验证,终于发现了关键影响因素。最后给出的优化方案让老雷惊掉了下巴:调整主控芯片与近端颗粒之间走线的层面,控制过孔stub越长越好。

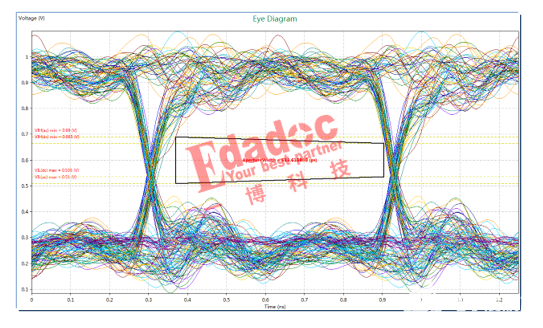

“都知道SI同事的套路深,没想到这么深。众所周知过孔stub越短越好,小雷为何这次却不走寻常路,偏偏要加长?!”老雷将信将疑,还是耐着性子按照小雷的要求调整走线层,过孔stub由调整前的35mil增加到94mil。不曾想,仿真结果再次颠覆了老雷的认知,近端颗粒的信号质量竟然鬼使神差的好了起来:

老雷心中疑云密布: “为什么会这样?难道以前的经验有错?”

小雷仿佛看透了老雷的想法,于是解释起来:“其实,一开始自己也是百思不得其解,后来从stub的特点切入,才慢慢有了眉目:过孔stub本质是一种能量泄放的通道,越是高频的能量受到的影响越大,因此,高速串行信号需要控制过孔stub尽量短,以避免能量损耗。但是,本项目的特殊之处在于主控芯片的驱动较强,加上一驱多拓扑的反射更容易在近端颗粒处积累,所以近端颗粒的信号质量就成了通道的瓶颈,增加近端颗粒的过孔stub长度能够很好的衰减高频分量,使主芯片输出的强度减弱,上升沿变缓,最终达到减少反射的目的,相应的,信号质量也得到了改善。不过,这也是一家之言,要深入理解这个现象还有待进一步的研究。”

“这是不是说所有DDRX的Flyby信号拓扑都要控制近端颗粒过孔stub尽量长呢?”老雷继续问道。

小雷沉吟半晌:“不是,增加过孔stub这种非常规操作需要慎用,这个项目这么做也是因为有仿真的验证。如果主控芯片的驱动本身比较弱,这时再增加过孔stub可能就适得其反了。”

老雷秒懂了:“所以,It depends!实在拿不准的还是要仿真。”

两人会心一笑,顺利投板。两个月以后,客户反馈了改板调试成功的消息,给这个项目画上了圆满的句号。

问题来了

大家接触过的DDRX最多拖了几个颗粒呢?地址信号采用什么拓扑?欢迎分享

审核编辑:符乾江

-

DDR

+关注

关注

11文章

712浏览量

65355 -

数据信号

+关注

关注

0文章

58浏览量

11971

发布评论请先 登录

相关推荐

DDR3、DDR4、DDR5的性能对比

DDR5内存与DDR4内存性能差异

DDR5内存的工作原理详解 DDR5和DDR4的主要区别

如何选择DDR内存条 DDR3与DDR4内存区别

DDR4时序参数介绍

什么是DDR4内存的工作频率

DDR4的主要参数

DDR4的结构和寻址方式

DDR4接口引脚定义及功能

DDR4寻址原理详解

DDR4内存频率最高多少

DDR4时钟频率和速率的关系

DDR4的基本概念和特性

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动

DDR4设计过孔STUB长,DDR信号“强”?

DDR4设计过孔STUB长,DDR信号“强”?

评论