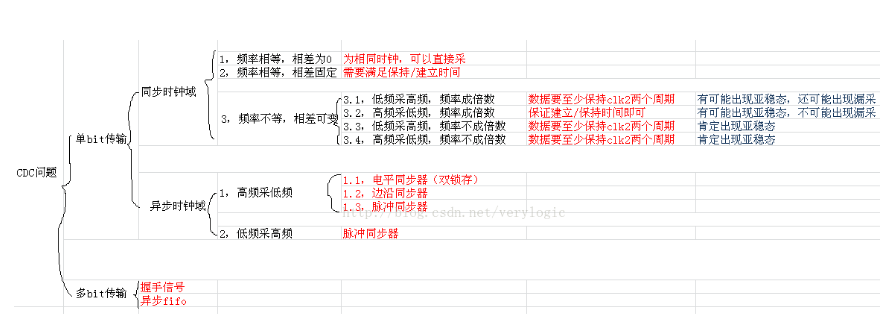

CDC(不同时钟之间传数据)问题是ASIC/FPGA设计中最头疼的问题。CDC本身又分为同步时钟域和异步时钟域。这里要注意,同步时钟域是指时钟频率和相位具有一定关系的时钟域,并非一定只有频率和相位相同的时钟才是同步时钟域。异步时钟域的两个时钟则没有任何关系。这里假设数据由clk1传向clk2。

单bit传输时,同步时钟域因为频率和相位关系都是已知的,可以推导的,所以不需要采用额外的硬件电路就可以解决CDC问题,只需要源数据在clk1端保持足够长时间即可。让其保持足够长时间有两个好处:即便出现亚稳态,也可以在两个clk2时钟周期后数据变得稳定下来,从而采到正确的结果。还可以防止低频采高频时,因为频率跟不上而导致数据丢失。

单bit传输时,异步时钟域的传输就必须使用额外的电路模块(同步器)来保证数据正确的传输。最基本的同步器是双锁存结构的电平同步器,其余的同步器都是由其衍生而来。该同步器的基本原理,也是让数据至少在clk2的时钟下保存两个周期,消除亚稳态。当然同步器能解决异步时钟域的同步问题,自然也可以拿来解决同步时钟域的问题,毕竟同步时钟域更简单一些。

实际的电路设计中,才不会管那么多细节,不管你是同步时钟域还是异步时钟域,只要是不同的时钟之间传数据,就加上同步器的结构,这当然是一种偷懒的解决办法。脉冲同步器就是这么一种万能的结构,对于单bit跨时钟域传输而言,使用脉冲同步器就够了,不需要区分时钟有没有关系,也不需要区分是高频采低频还是低频采高频,毕竟也很少有人能掌握这么全的细节。

对于多bit传输,不能采用单bit传输的方法。原因在于,单bit传输时,不能确定该数据到底经过1个clk2时钟周期之后有效还是两个clk2时钟周期之后才有效。所以对多个bit各自采用单bit的同步机制,会导致输出一些错误的中间状态。对于多bit传输,只能使用握手信号或者异步fifo。

总结如下:

1、有关系的时钟之间传单bit数据,理论上只需要源数据保持足够长的时间(clk2的两个周期)即可;

2、无关系的时钟之间传单bit数据,必须要使用同步器;

3、不管有无关系的时钟进行单bit传输,脉冲同步器都可以解决这个问题;

4、多bit传输只能使用握手机制或者异步fifo;

5、低频采高频,为防止数据不丢失,应当让源数据变慢,多保持一些周期;高频采低频则不需要,但是高频采低频得到的结果可能带有很多冗余。

原文标题:FPGA学习-CDC问题的解决方案总结--异步时钟

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

602978 -

asic

+关注

关注

34文章

1199浏览量

120434 -

异步时钟

+关注

关注

0文章

17浏览量

9404 -

同步时钟

+关注

关注

0文章

47浏览量

3219

原文标题:FPGA学习-CDC问题的解决方案总结--异步时钟

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ASIC和FPGA的优势与劣势

cogoask讲解fpga和ASIC是什么意思

如何在FPGA和ASIC设计中结合高速USB功能

ASIC设计-FPGA原型验证

FPGA和ASIC芯片解密有哪些性能分析

高密度IC设计中ASIC与FPGA选择谁

ASIC和FPGA有什么区别

ASIC和FPGA设计中的多点综合技术

ASIC设计转FPGA时的注意事项

如何使用report_cdc命令分析、调试和修复CDC问题

FPGA_ASIC-MAC在FPGA中的高效实现

ASIC/FPGA设计中的CDC问题分析

ASIC/FPGA设计中的CDC问题分析

评论