自中科昊芯推出专题讲解SCI串口通信以来,第一期主要讲解SCI串口FIFO通信原理,第二期主要讲解SCI串口自动波特率,本期主要讲解FIFO中断通信逻辑。

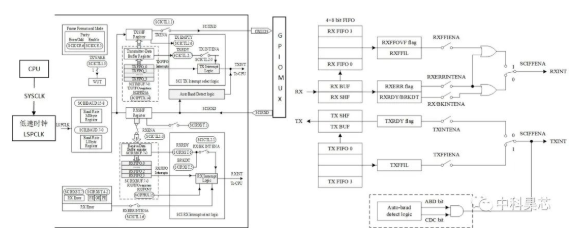

HX2000系列SCI模块原理与中断逻辑如下,中断逻辑为:当SCITXBUF数据被传输到TXSHF寄存器时,将通过SCICTL[TXRDY]产生一个发送中断,使能SCICTL[TXINTENA]打开发送中断信号,将通过PIE响应CPU执行,使得CPU可以连续写数据到SCITXBUF,使得SCI模块可以向PC端连续发送数据。当SCI接收一个完整帧,并将RXSHF寄存器中的数据传输到SCIRXBUF寄存器中,将通过SCIRXST[RXRDY]产生一个接收中断,使能SCICTL[RXBKINTENA]打开接收中断信号,将通过PIE响应CPU执行,使得CPU读取PC端发送的数据帧。

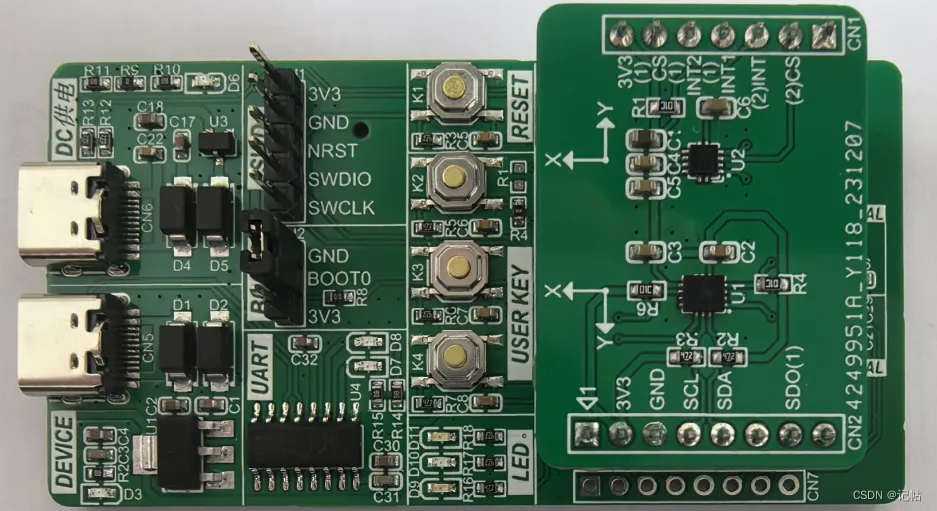

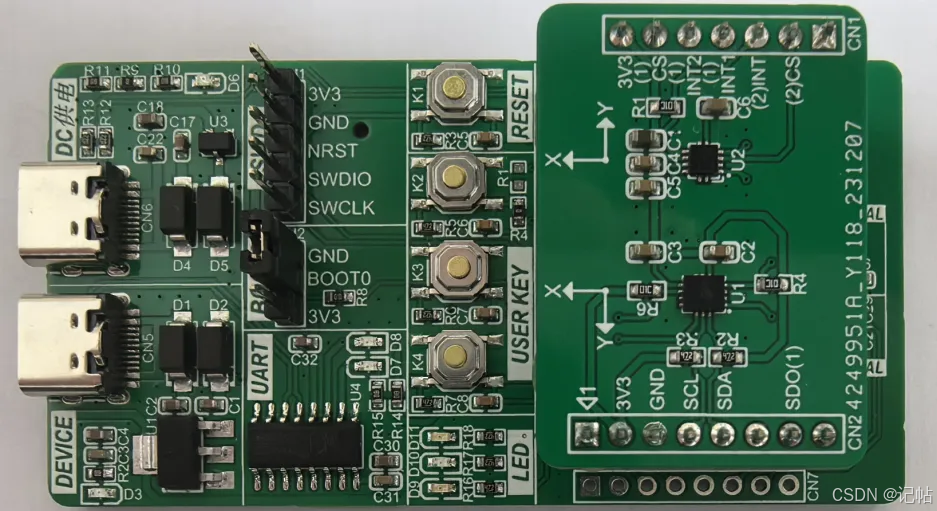

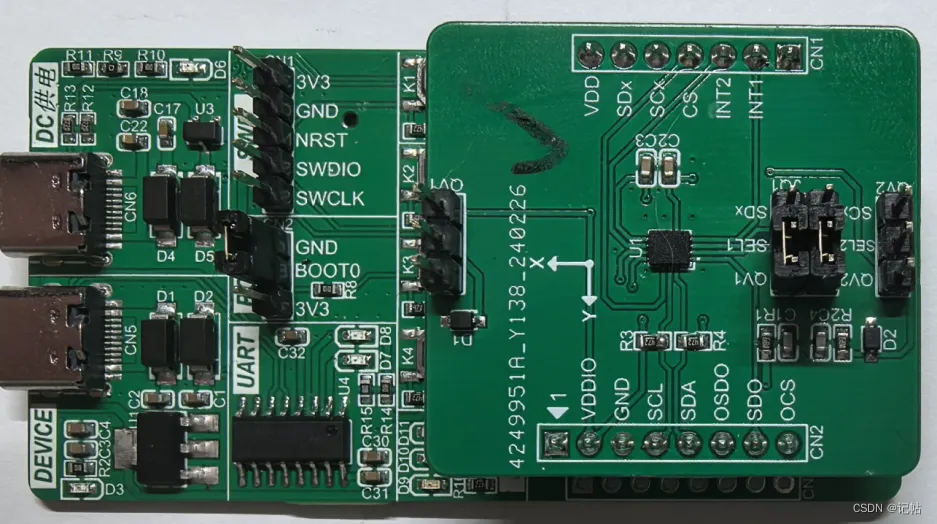

由此设计SCI串口FIFO中断通信实例:采用SCI与串口CH340,连续发送数据,PC端接收发送的数据;通过串口调试助手,向CPU发送任意一组数据,CPU接收发送的数据。

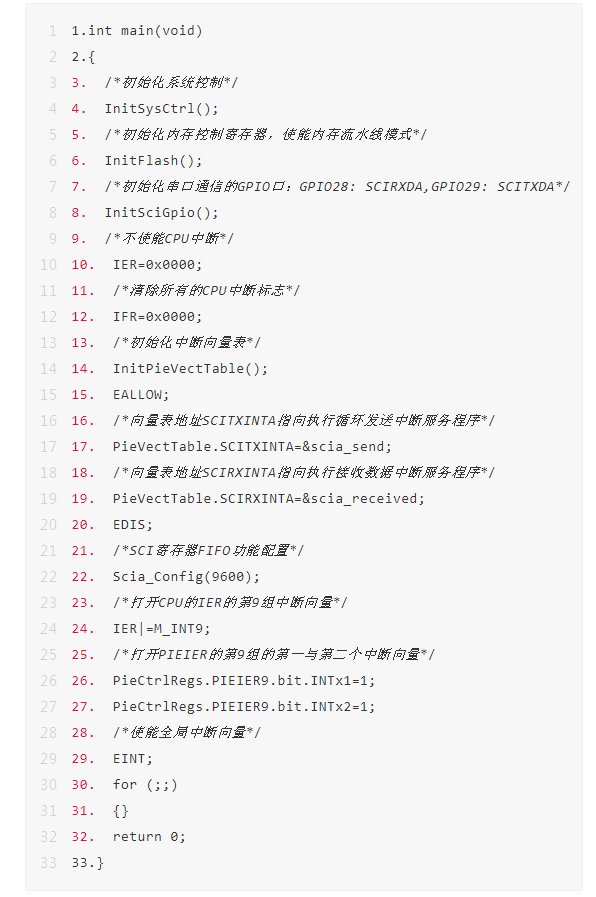

基于以上分析,在CDK上开发SCI串口FIFO中断通信输出程序,代码包括:SCI GPIO外设引脚配置,FIFO功能配置,发送与接收中断程序,主程序调用执行。主要代码如下:

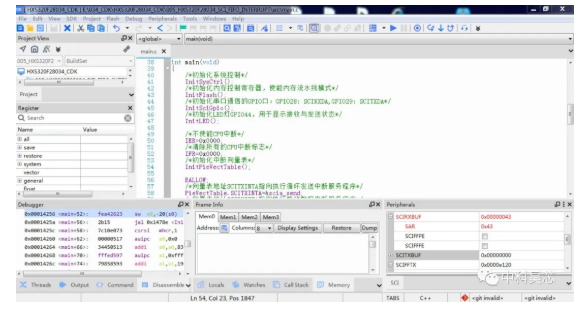

CDK上开发SCI串口FIFO中断通信程序,其编译结果为:

编译通过后,就可以开始调试了,DSP端连续发送数据的调试结果如下:

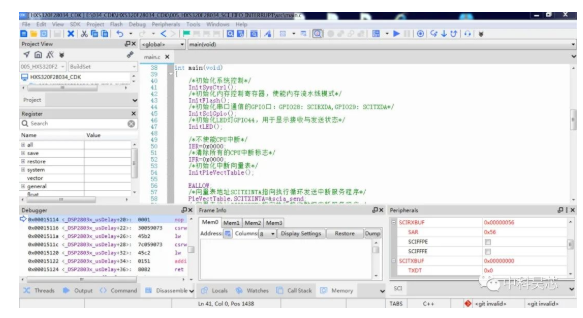

PC端发送数据的调试结果如下:

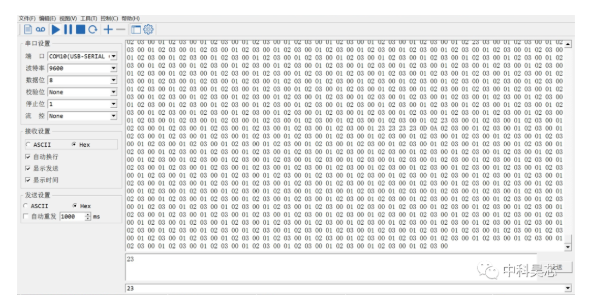

调试后,可通过串口调试助手查看发送与接收到的数据如下图:

-

dsp

+关注

关注

553文章

7998浏览量

348869 -

寄存器

+关注

关注

31文章

5342浏览量

120325 -

数据

+关注

关注

8文章

7017浏览量

89011 -

串口通信

+关注

关注

34文章

1624浏览量

55523

发布评论请先 登录

相关推荐

AFE4960如何正确的从FIFO中读取样本呢?

FIFO Generator的Xilinx官方手册

陀螺仪LSM6DSOW开发(4)----中断获取FIFO数据

ASM330LHH使用FIFO阈值中断输出时工作异常的原因?

驱动LSM6DS3TR-C实现高效运动检测与数据采集(8)----中断获取FIFO数据并应用MotionFX库解析空间坐标

陀螺仪LSM6DSV16X与AI集成(9)----中断获取FIFO数据并应用MotionFX库解析空间坐标

上位机与pLc通讯中断如何判断

同步FIFO和异步FIFO区别介绍

FIFO中断通信逻辑介绍

FIFO中断通信逻辑介绍

评论