基于UVM搭建验证环境和构造验证激励,调试的工作总是绕不开的。实际上,对验证环境和激励的调试,往往伴随着验证阶段的前半程,并且会花掉验证工程师很多时间和精力。然而,大部分细节被隐藏在复杂的环境内部。这里的复杂,指的是UVM本身构造的不同机制(比如factory、config_db、objection等),以及在不同机制内部使用的数据结构。

作为UVM的用户,我们需要相信在绝大部分情况下这些机制本身是没有问题的。因此,从顶层获得有效的调试信息就非常关键,比起潜入到内部要高效得多。

这也是本文的目的,盘点UVM针对不同机制提供给用户的调试功能。建议收藏和关注,总有一天你会用到。本文的示例代码都是在UVM类库提供的例程上进行少量修改得到的。

01 PLUGARG(命令行参数)

01 PLUGARG(命令行参数)

UVM将不同机制的调试功能封装成了命令行参数。在运行仿真的时候带上这些参数,就可以在仿真日志中打印出来对应的详细调试信息。本节将这些命令行参数都梳理出来,并附有仿真日志截图。

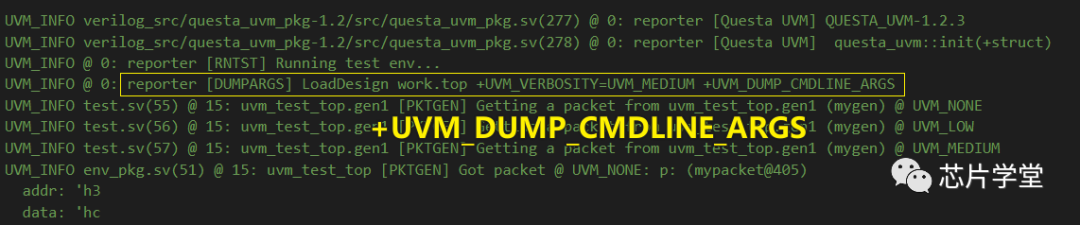

+UVM_DUMP_CMDLINE_ARGS:导出所有的命令行参数,确认当前的命令行参数符合你的预期。

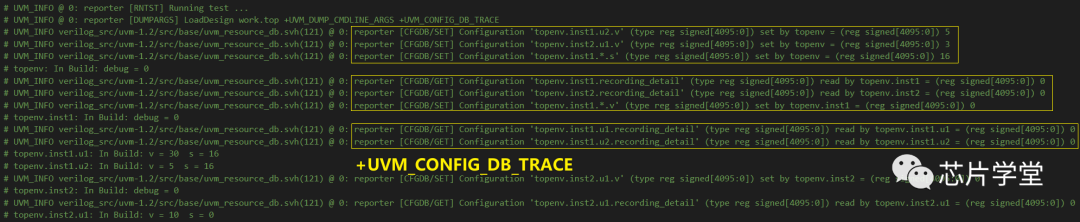

+UVM_CONFIG_DB_TRACE: 打开访问Config_db的追踪(tracing)功能,可以看到config_db的set和get操作在什么时间由什么组件发起。

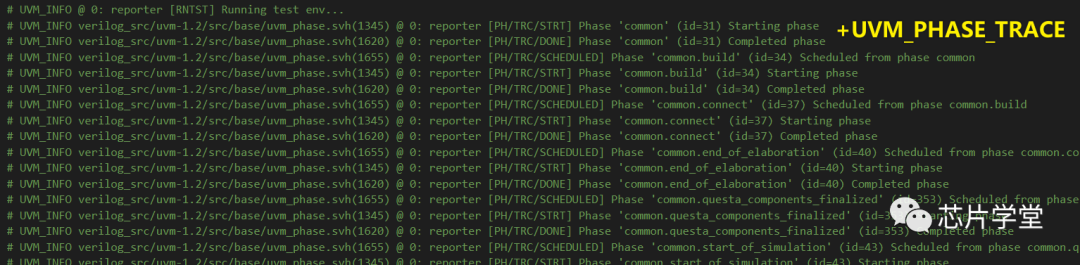

+UVM_PHASE_TRACE:打开Phase执行的追踪功能,可以看到不同phase的执行顺序。

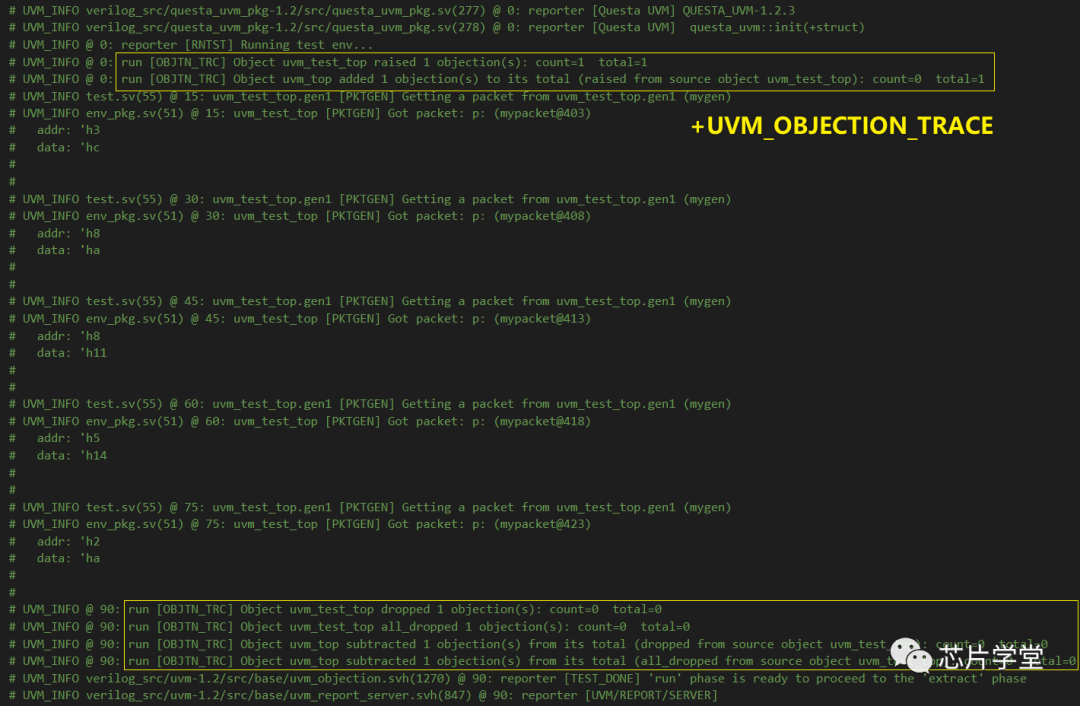

+UVM_OBJECTION_TRACE:打开Objection相关活动的追踪功能,可以清晰地呈现出objection在运行中的状态。

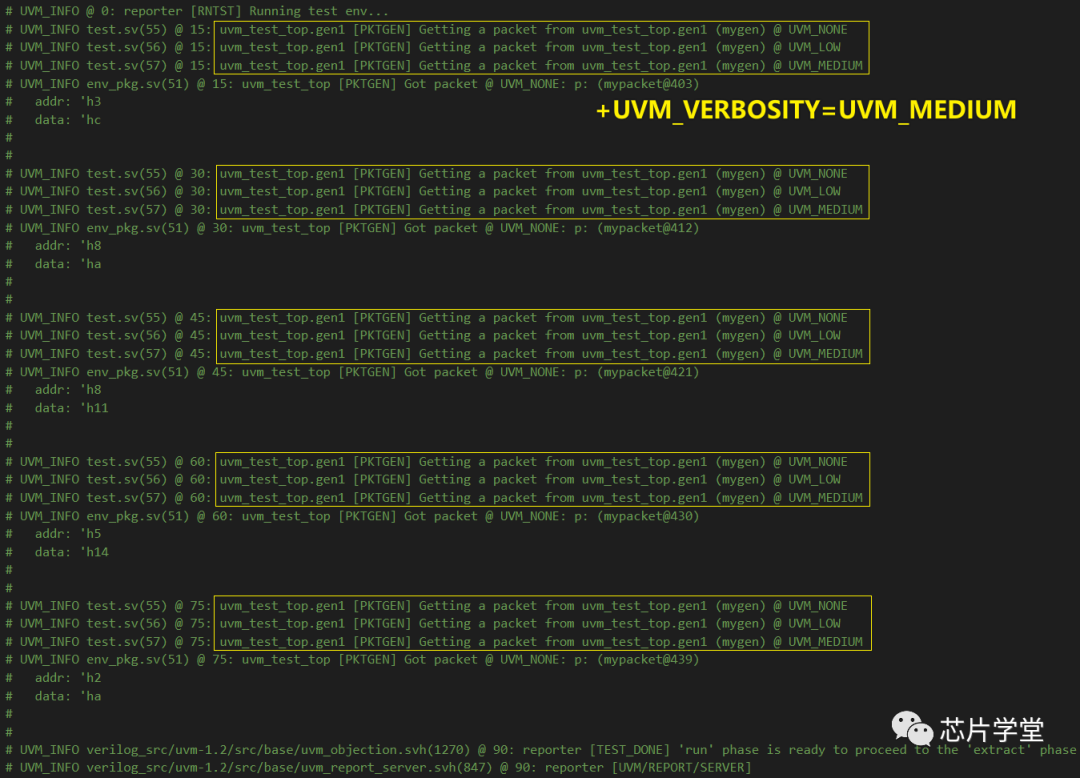

+UVM_VERBOSITY:设置打印信息的冗余程度,有效地控制不同重要性信息的打印和屏蔽。

02 PRINT(打印)

02PRINT(打印)

除了命令行参数,UVM还提供了很多内置打印函数。这些函数可以在验证环境中被调用,调用后会将对应的数据结构按照强可读性的格式打印到仿真日志中,为环境调试工作提供极大的便利。

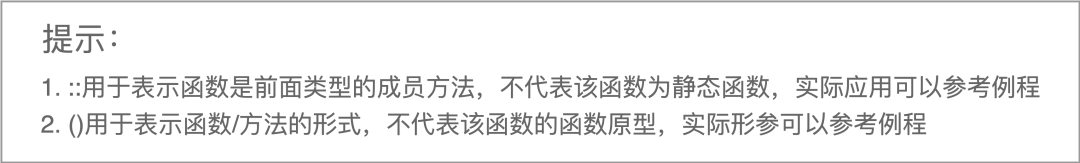

uvm_root::print_topology():打印整个验证环境的组件拓扑结构

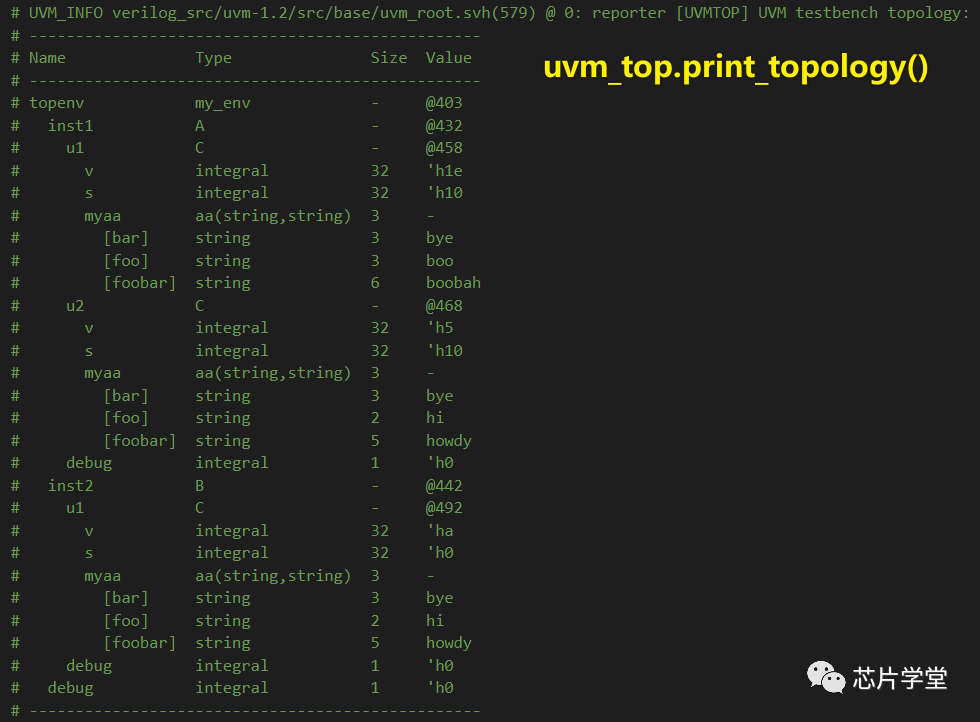

uvm_component::print_config():打印当前组件可见视角下的所有配置资源信息

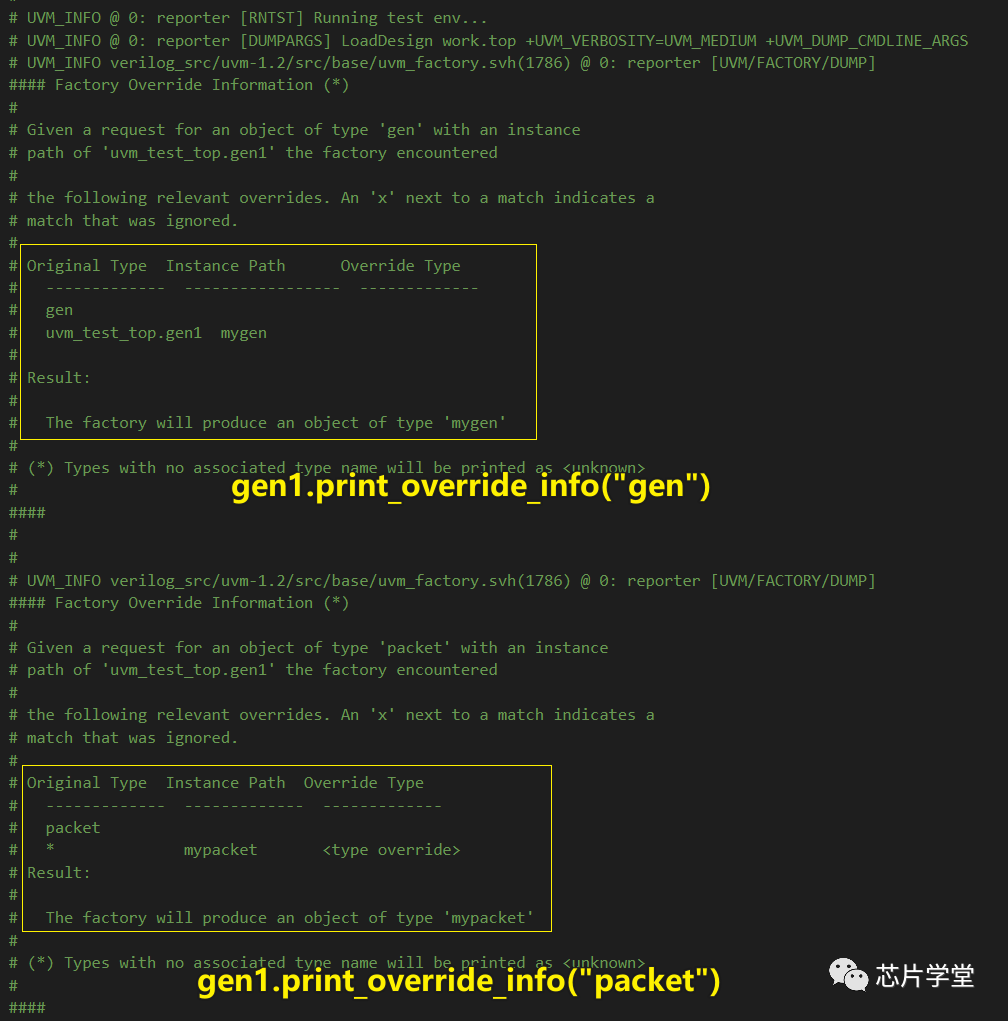

uvm_component::print_override_info():打印当前组件的工厂重载信息

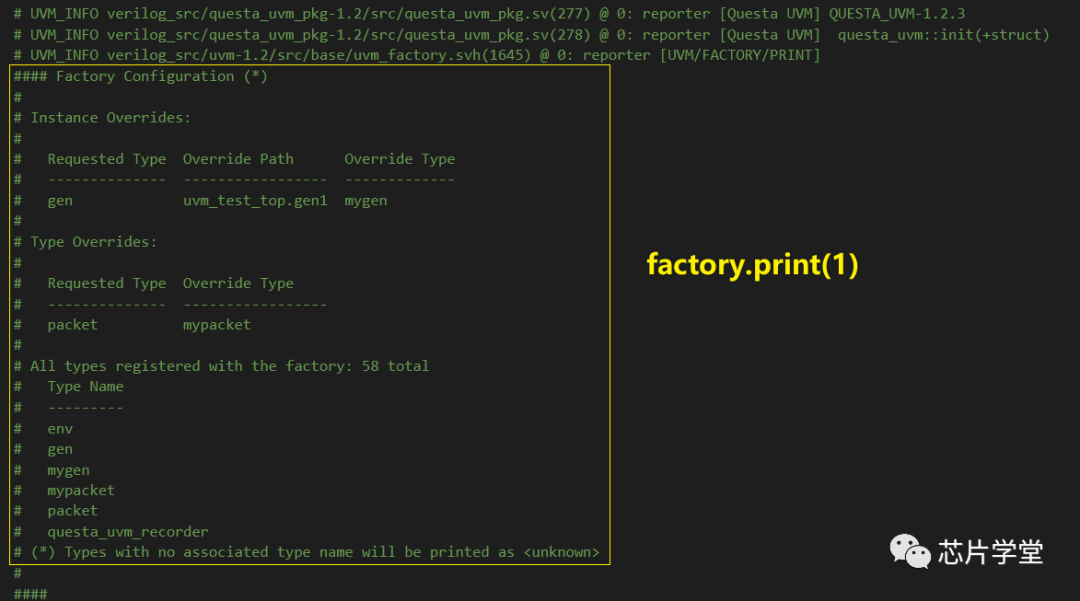

uvm_factory::print():打印全局工厂中注册的类型以及instance和type重载信息

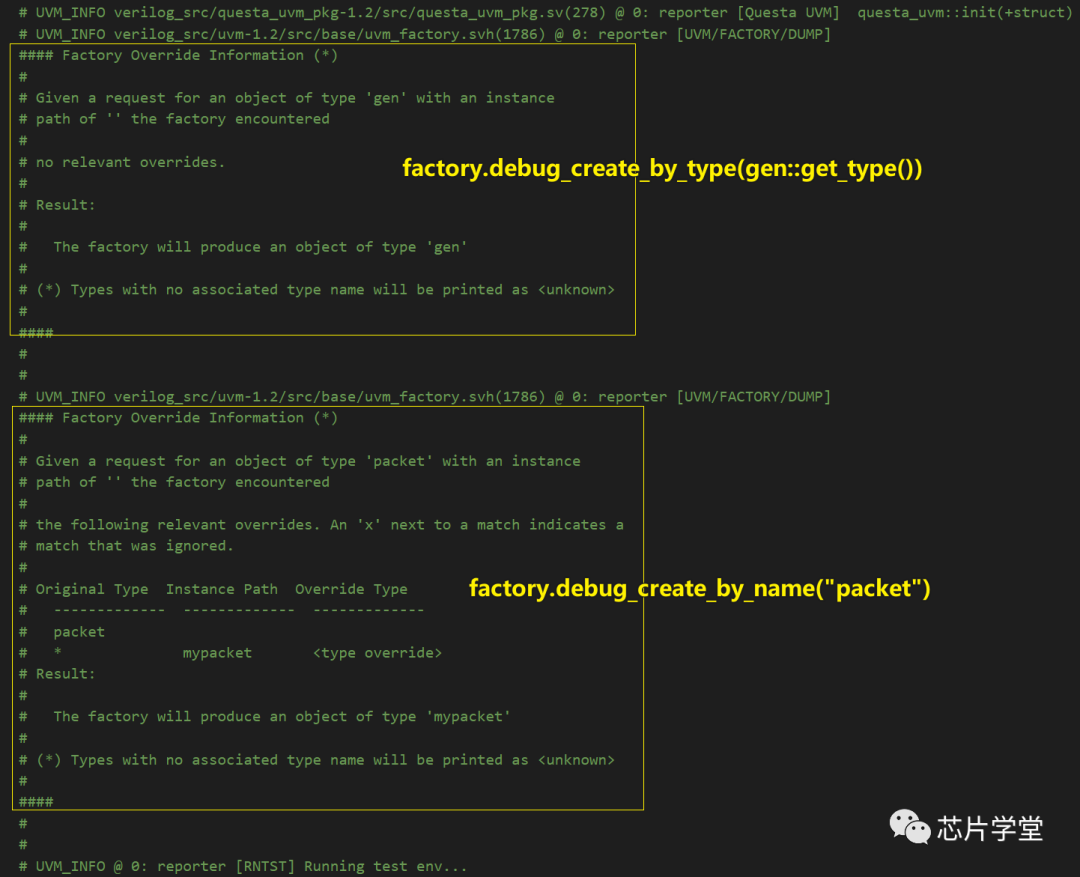

uvm_factory::debug_create_by_type():打印工厂根据参数实际会创建的类型

uvm_factory::debug_create_by_name():打印工厂根据参数实际会创建的类型

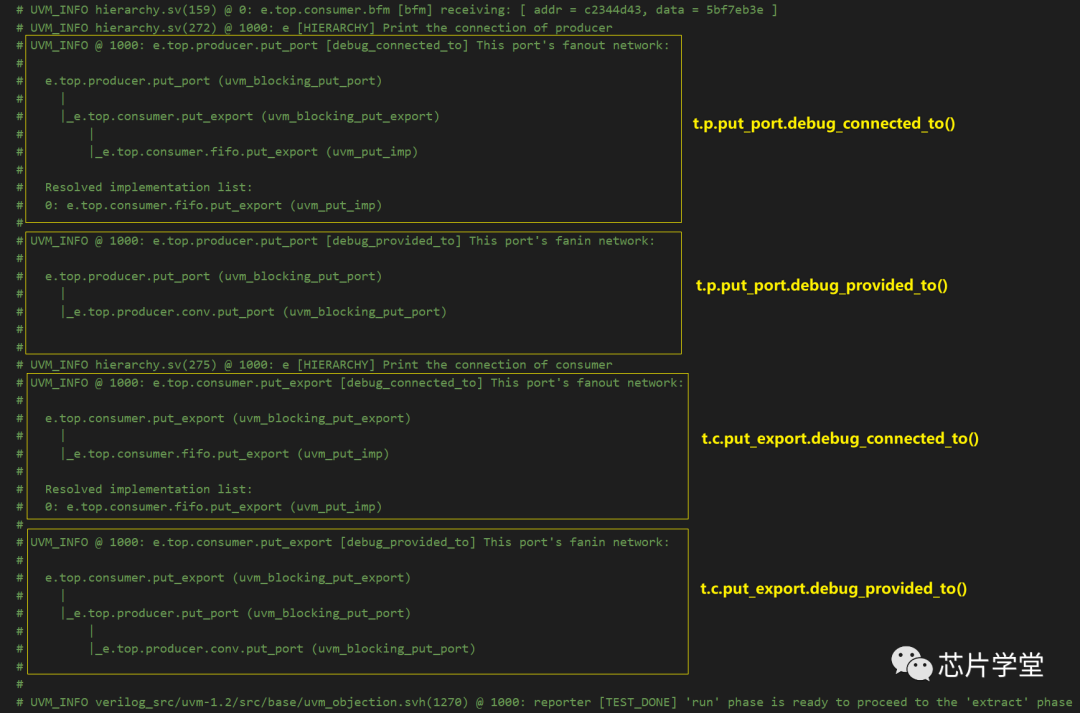

uvm_port_base::debug_connected_to():打印当前端口连接的下游端口网络,包括port/export/imp

uvm_port_base::debug_provided_to():打印当前端口连接的上游端口网络,包括port/export

审核编辑 :李倩

-

仿真

+关注

关注

50文章

4152浏览量

134409 -

UVM

+关注

关注

0文章

182浏览量

19271 -

机制

+关注

关注

0文章

24浏览量

9846

原文标题:SystemVerilog | UVM | 超实用!盘点UVM不同机制的调试功能

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

盘点UVM针对不同机制提供给用户的调试功能

盘点UVM针对不同机制提供给用户的调试功能

评论