一般Fabless公司设计的芯片在工程批回来之后,都会做芯片级的ESD测试和latchup等测试,对很多客户朋友来说,有可能对latchup稍微陌生,本篇文章将简要介绍latchup。

latchup的中文译名为闩锁或闩锁效应,要想了解清楚latchup,需要先了解MOS管的结构。

1MOS管的结构

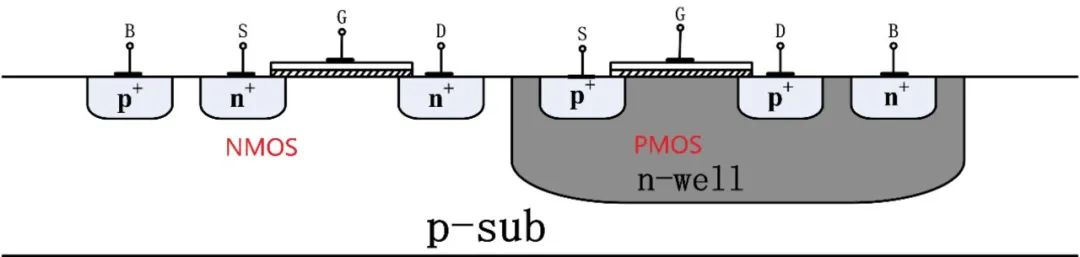

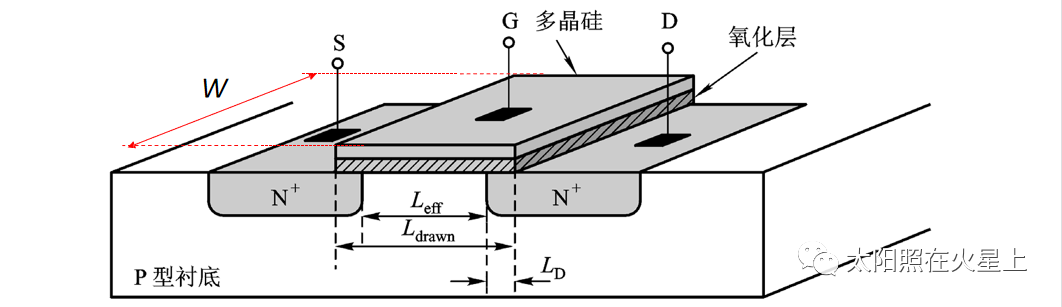

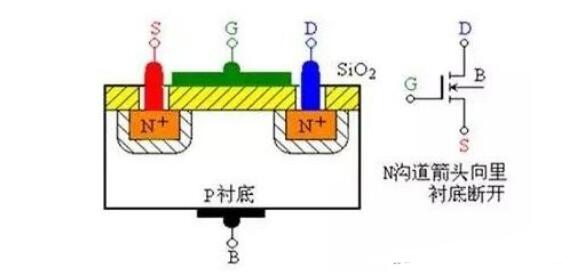

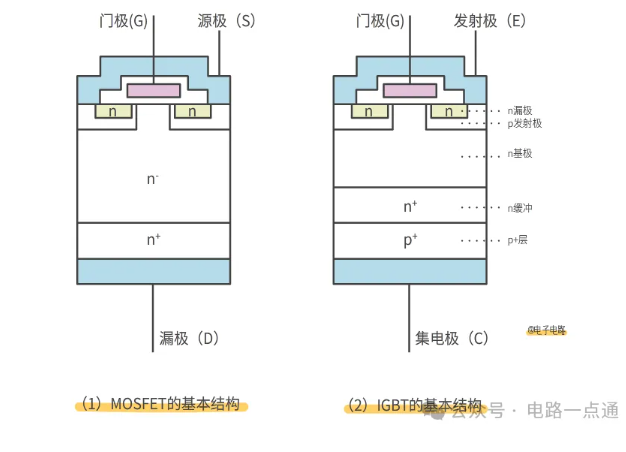

在CMOS电路中,有NMOS 和PMOS两种晶体管。在制作NMOS时,首先是有一个P型衬底,一般称为P-substrate,为避免将substrate和Source混淆(因首字母一样),经常将P衬底称为P-Body或P-Bulk。在P型衬底上,两个重掺杂n区形成源端(Source)和漏端(Drain),重掺杂的多晶硅区(简称poly)作为栅(Gate),一层薄SiO2(简称栅氧)使栅与衬底隔离,而器件的有效作用就发生在栅氧化层的衬底区,因为衬底电位对器件特性有很大的影响,所以MOSFET是一个四端器件(即Gate、Drain、Source、Bulk)。

关于栅氧层,因为SiO2是绝缘的,所以NMOS管的输入阻抗Rgs是无穷大,输入电流趋近于零。现在国内发展得如火如荼的电容隔离器,隔离栅使用的绝缘介质也是SiO2。

在现代CMOS工艺中,PMOS器件做在n阱(即n-well)中,而之所以这么做,是因为在实际生产中,NMOS器件和PMOS器件必须做在同一衬底上,所有的NMOS器件都共享一个P衬底,而每一个PMOS可以处于各自独立的N阱中。对于PMOS,源和漏重掺杂P型元素,导电载流子为空穴,栅源电压足够负,在氧化层-硅界面才会形成一个由空穴组成的反型层,从而为源和漏之间提供一个导电沟道,所以PMOS器件的阈值电压通常是负的。

2latchup的形成原因

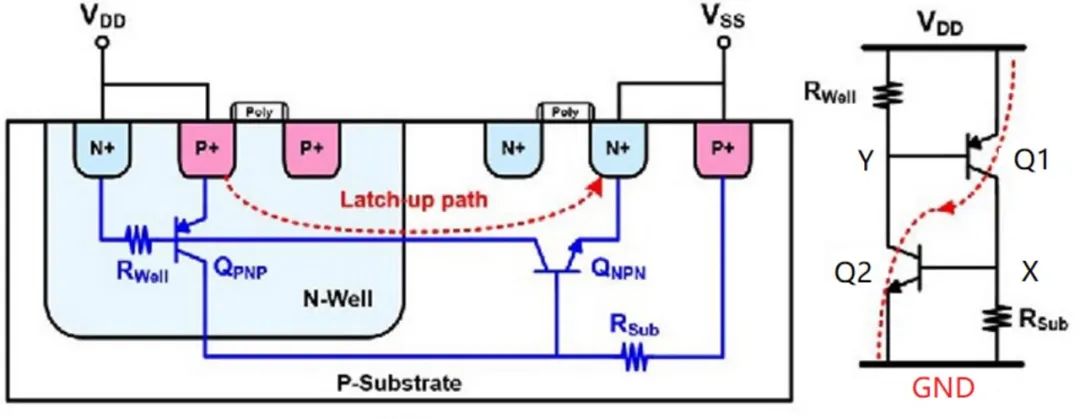

如下图所示的NMOS和PMOS器件,会寄生出Q1 PNP管和Q2 NPN 管,从图中可以看出,每个双极型晶体管的基区必然与另一个晶体管的集电区相连接,而且由于n阱和p衬底均有一定的电阻,所以Q1和Q2会形成一个正反馈环路。

实际上,如果有电流注入结点X使Vx上升,则Q2的Ic2增大,那么Vy=VDD-Rwell*Ic2会减小,Vy减小会导致IC1增大,进而导致Vx进一步上升。如果环路增益≥1,这种现象会持续下去,直至两个晶体管都完全导通,从VDD抽取很大的电流。此时称该电路被闩锁。

触发闩锁效应的起始电流可以由集成电路中的各种原因产生,例如当漏端的一个大电压摆动,会通过容性耦合向n阱或衬底注入相当大的位移电流,从而引发闩锁效应。

闩锁效应通常发生在大尺寸的输出反相器的情况下,因为在这种情况下,一是这种电路容易通过晶体管较大的漏结电容向衬底注入大电流,另外一种情况,是由于在与地相连的键合线上,产生相当大的瞬态电压,通过正偏源衬二极管向衬底注入大电流。

Latchup就是闩锁效应,它是CMOS工艺所特有的寄生效应,是指在CMOS电路中,电源VDD和地GND之间由于寄生的NPN和PNP双极性BJT的相互影响而产生一个低阻通路,低阻通路会在电源和地之间形成大电流,可能会使芯片永久性损坏。

荣湃半导体

荣湃半导体创立于2017年,专注于高性能模拟集成电路产品的研发与设计,聚焦数字隔离器、驱动器、隔离放大器等产品系列,并广泛应用于工业控制、新能源汽车、数字电源、智能电器等领域,致力于建立物理世界与数字世界的安全联结。凭借自主知识产权的电容智能分压(iDivider)技术,实现国产数字隔离芯片的突破,匠心智造不一样的隔离好产品,用“芯”创造新价值。

原文标题:技术课堂之十二 | 浅谈latchup

文章出处:【微信公众号:荣湃半导体】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

ESD

+关注

关注

48文章

2012浏览量

172736 -

MOS管

+关注

关注

108文章

2396浏览量

66603 -

latchup

+关注

关注

1文章

2浏览量

1159

原文标题:技术课堂之十二 | 浅谈latchup

文章出处:【微信号:gh_fb935efbb3e1,微信公众号:荣湃半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MOS管的基本结构 MOS管的二级效应

MOS管种类和结构

分析MOS管发烫原因

mos管损坏的原因分析

MOS管的结构与latchup的形成原因

MOS管的结构与latchup的形成原因

评论