数字硬件建模SystemVerilog(九)-网络和变量的未压缩数组

SystemVerilog有两种类型的数组:压缩数组和非压缩数组。压缩数组是连续存储的位的集合,通常称为向量。非压缩数组是网络或变量的集合。

集合中的每个网络或变量称为数组元素。未压缩数组的每个元素的类型、数据类型和向量大小都完全相同。每个未压缩的数组元素可以独立于其他元素存储;这些元素不需要连续存储。软件工具,如仿真器和综合编译器,可以以工具认为最佳的任何形式组织未压缩数组的存储。

未压缩数组的基本声明语法为:

数组的维度定义了数组可以存储的元素总数。未压缩的数组可以用任意数量的维度声明,每个维度存储指定数量的元素。声明数组维度有两种编码样式:显式地址和数组大小。

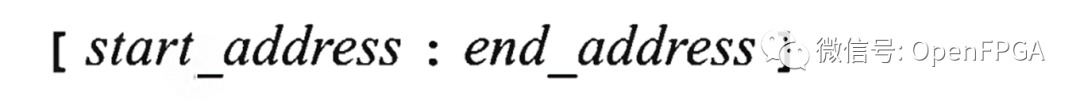

显式地址样式指定方括号之间数组维度的起始地址和结束地址,格式为:

Start_address 和 end_address可以是任何整数值,数组可以以地址0、地址512或被建模硬件所需的任何地址开始。起始地址和结束地址之间的范围表示数组维度的大小(元素数)。

数组大小样式定义要存储在方括号中的元素数(类似于C语言数组声明样式)。

[size]

使用array_size样式,起始地址始终为0,结束地址始终为size-1

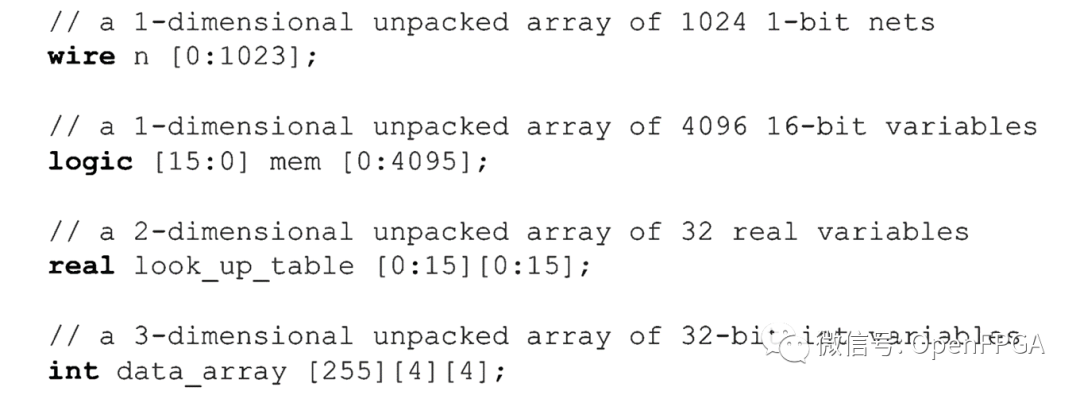

以下是一些未压缩的数组声明示例:

前面的mem声明是16位logic变量的一维数组。一维阵列有时被称为内存阵列,因为它通常用于仿真硬件内存设备(如RAM和ROM)的存储。

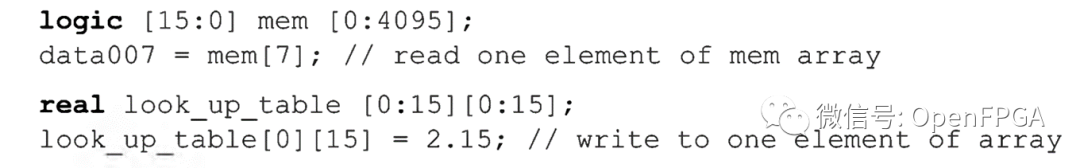

访问数组元素

可以使用数组索引引用未压缩数组的每个元素,索引紧跟在数组名称之后,并且位于方括号中,多维数组需要多组方括号才能从数组中选择单个元素:

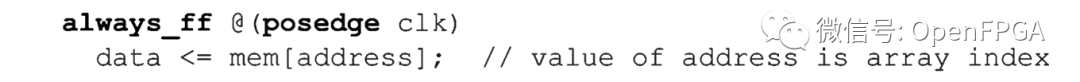

数组索引也可以是网络或变量的值,如下一个示例所示:

复制数组(阵列)

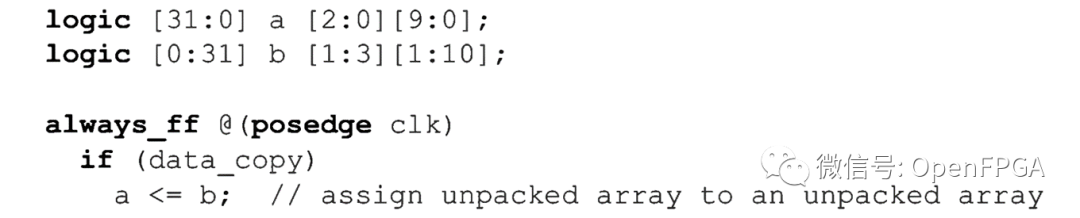

如果两个数组(阵列)具有相同的布局,则可以使用赋值语句将一个未压缩的数组(阵列)复制到另一个未压缩的数组(阵列)。也就是说,这两个数组(阵列)必须存储相同向量大小的相同数据类型,必须具有相同的维度数,并且每个维度的大小都相同-

数组(阵列)复制会将源数组(赋值的右侧)的每个元素复制到目标数组(阵列)(赋值的左侧)中相应的元素。两个数组(阵列)的索引编号不需要相同。数组(阵列)的布局和类型必须完全匹配。

与复制数组(阵列)的方式类似,如果两个切片的布局相同,则可以将数组(阵列)的一部分(称为数组(阵列)切片)复制到另一个数组(阵列)的切片。切片是数组(阵列)一维内的一个或多个连续编号的元素。

在成为SystemVerilog之前,最初的Verilog语言将对数组(阵列)的访问限制为一次只能访问数组中的一个元素。不允许对数组(阵列)的多个元素进行数组(阵列)复制和读/写操作。

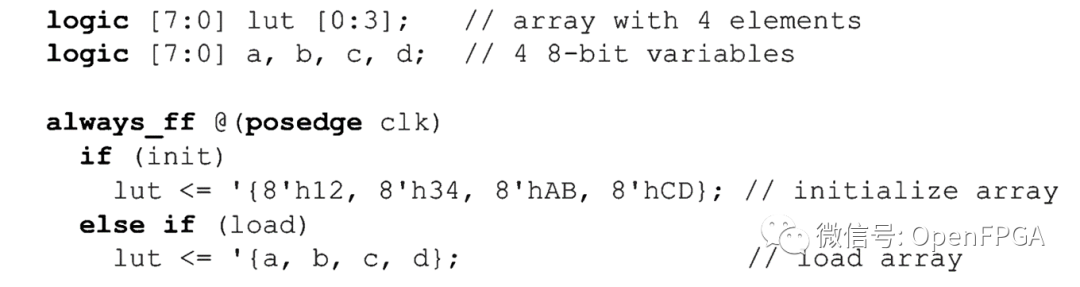

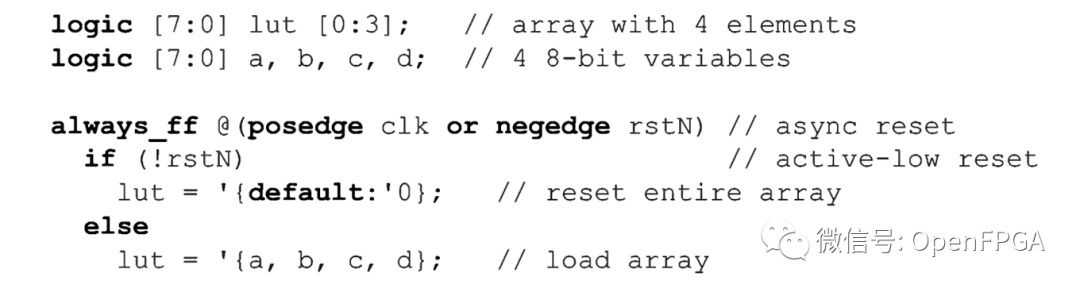

数组列表赋值

可以为未压缩的数组或数组的一个片段分配一个值列表,这些值包含在每个数组维度的’{and}大括号之间。

列表语法类似于在C中为数组指定值列表,但在大括号前添加了撇号使用’-“作为开头分隔符”表明,所包含的值是表达式列表,而不是SystemVerilog连接运算符(后面会详细介绍)。

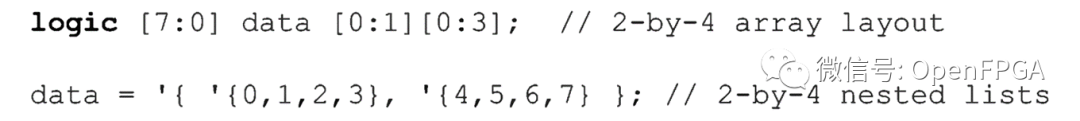

还可以使用嵌套列表为多维数组分配值列表。嵌套的列表集必须与数组的维度完全匹配。

此数组分配相当于以下各项的单独分配:

通过指定默认值,可以为未压缩数组的所有元素指定相同的值。默认值是使用’{default:}指定的,如以下代码段所示:

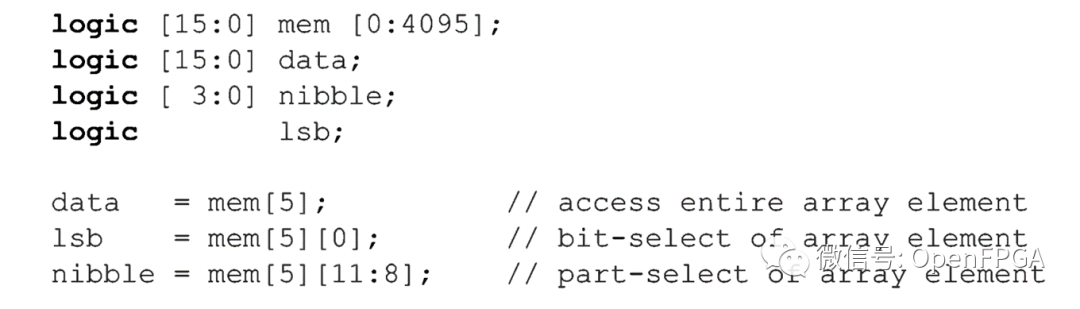

数组元素的位选择和部分选择

可以从数组元素向量中选择一位或一组位。必须首先选择数组的单个元素,然后进行位选择或部分选择。

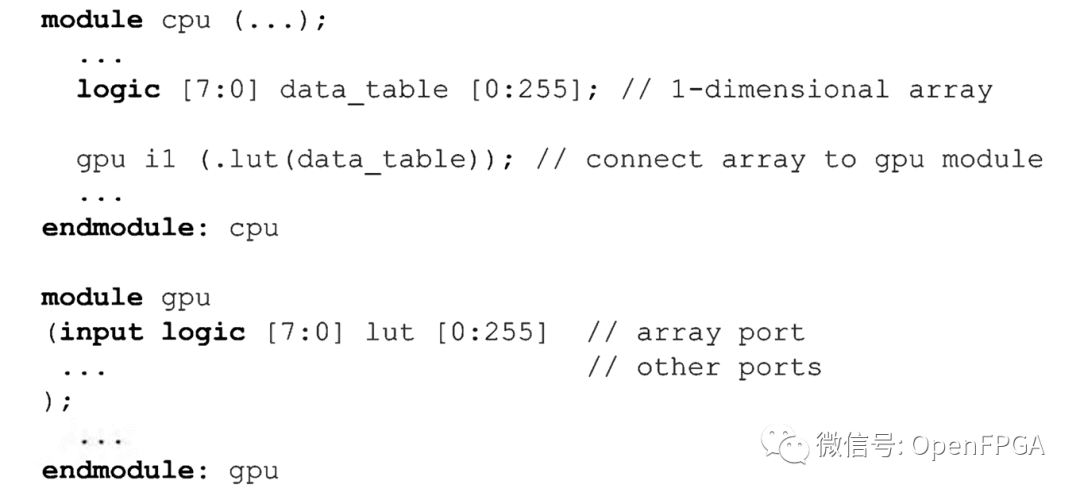

通过端口将数组传递给任务和函数。任何类型和任意数量的未压缩数组都可以通过模块端口传递,也可以传递到任务和函数参数。端口或任务/函数形式参数也必须声明为数组,端口或参数数组必须与要传递的数组具有相同的布局(与数组复制的规则相同)。

最初的Verilog语言只允许简单的向量通过模块端口,或传递到任务或函数参数。要传递上述示例中表数组的值,需要256个端口,数组的每个元素一个端口。

审核编辑 :李倩

-

编译器

+关注

关注

1文章

1672浏览量

51895 -

变量

+关注

关注

0文章

616浏览量

29566 -

数组

+关注

关注

1文章

420浏览量

27458

原文标题:SystemVerilog(九)-网络和变量的未压缩数组

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何为 S32DS 中的特定变量(RAM、闪存、数据闪存)强制使用特定内存区域?

飞凌嵌入式ElfBoard-环境变量之添加修改环境变量putenv

飞凌嵌入式ElfBoard-环境变量之获取环境变量

基于凌羽派的OpenHarmony北向应用开发:ArkTS语法-数据类型和变量声明

面向嵌入式部署的神经网络优化:模型压缩深度解析

MinGW-w64工具集压缩包的下载

linux的压缩和解压操作

电能质量在线监测装置的数据压缩存储功能对数据传输速度的影响有多大?

第7章 变量进阶与点阵LED(7.1 7.2)

数组的初体验

NMSIS神经网络库使用介绍

低内存场景下的高效压缩利器:FastLZ压缩库应用实践指南

网络和变量的未压缩数组

网络和变量的未压缩数组

评论