引言

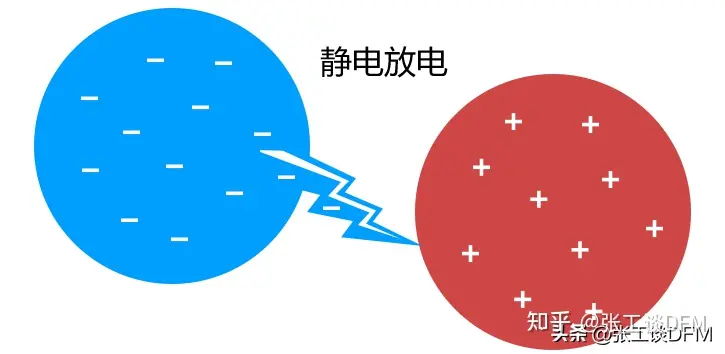

近年,随着半导体工艺技术的持续发展,大量手机、物联网、人工智能、高性能计算等领域所应用的专业芯片陆续采用FinFET先进工艺来实现,以满足高性能设计需求。面对先进工艺技术、高复杂度产品设计等方面的挑战,如何保证产品达成静电防护能力的需求指标?本文将分享芯耀辉静电防护团队的经验及应对策略。

先进工艺带来的挑战

芯片级别的静电防护,我们通常是指HBM(人体放电模式),MM(机器放电模式)和CDM(充电放电模式),其中MM在JESD22-A115标准中不再推荐测试。对于HBM/CDM传统的设计方式是为被防护的内部电路(例如Gate Oxide)添加静电防护电路(例如GGNMOS ESD device),这些位于IO pad或者内部电路的防护器件通常具备相比Gate oxide Breakdown Voltage(Vbox)较低的开启电压(Vt1),并留有一定的电压安全余量,以保证内部电路的安全,如下图1所示。

图1:GGNMOS TLP IV-Curve&防护窗口

如下图2实际管脚的TLP IV curve图所示,可以看到GGNMOS在Vt1=8V左右触发防护,并且提供了It2=2.0A左右的防护能力,根据HBM静电放电模型(R=1.5KΩ),大致可以推算等效HBM 3KV(2A*1.5K=3KV)的HBM静电防护能力。

图2:实测GGNMOS TLP IV-Curve

28nm以下的先进工艺,器件channel length/oxide厚度持续缩减,对应的Breakdown电压也一再持续降低。过往0.35um~40nm工艺时代,无论IO器件或是相对脆弱的Core器件,尽管Vgs breakdown/Vds breakdown电压持续走低,但其特性基本都延续了Vgs_bv> Vds_bv的趋势,并且保留了一定的安全设计余量,使得静电放电事件发生时,防护器件可以比被防护器件更先启动,达成保护被防护器件的功能。

图3:成熟工艺节点Breakdown Voltage

(来源:Industry Council on ESD Target Levels)

图4:FinFET高级工艺节点Breakdown Voltage

然而来到FinFET工艺时代,如图4所示,Vds/Vgs Breakdown电压不仅降低到3.0V附近,远低于65nm时代的6V,并且Vgs breakdown/Vds breakdown已经非常接近,“安全余量”窗口消失不见了,这就使传统的防护结构特别是CDM防护受到了挑战。

芯耀辉静电防护设计团队基于测试结构表现的实际Silicon数据、静电防护和电路设计,通过防护器件选型、防护电路结构调整等方面的共同创新,达到促进防护器件提前Breakdown、降低被防护器件在放电发生时遭受的电压降、恢复具备足够余量的“安全窗口”,从而使得基于FinFET工艺的IP拥有了几乎接近成熟工艺的表现,并且不会带来漏电或者过大面积的开销。

“TEST-TO-FAIL”的理念也深入贯彻在芯耀辉的静电防护设计中。通常芯片级ESD测试按照JEDEC或者AECQ-100的标准执行完成后,出于测试芯片数量或者成本的考虑,静电防护测试就算完成了。但芯耀辉静电防护团队的测试方案不会止步于此,秉承“TEST-TO-FAIL”的理念,团队会尽力收集每类实测结构的最大值。如图5所示,例中的芯片CDM+500V下,某一管脚放电波形Ipeak可以达到6A。有些尺寸较小的芯片CDM+500V对应的放电电流可能只有1~2A,如仅简单复用1~2A 的方案,6A 产品将无法达标。得益于“TEST-TO-FAIL”的测试支出带来的数据积累,静电设计人员在项目开始之初就能选用合适的设计规格,确保IP开发的成功。

图5:CDM测试电流

高度集成SoC的复杂度

所带来的挑战

先进的SoC芯片不仅采用FinFET高级工艺以持续提升产品性能和竞争优势,而且集成度、复杂度也越来越高,如图6为芯耀辉科技的一款测试芯片Ball POD,就具备几百个Ball。

ESD需要处理众多不同Ball间跨电压域的防护问题,相比单一器件级的产品会复杂很多。

图6:测试芯片Ball POD

系统级静电防护

设计带来的挑战

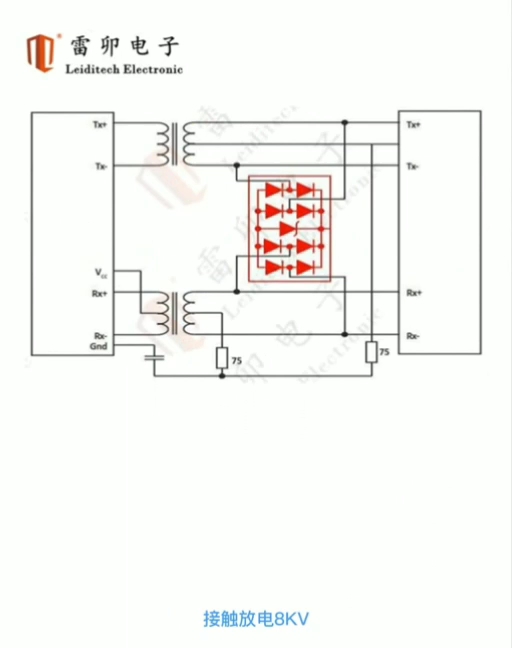

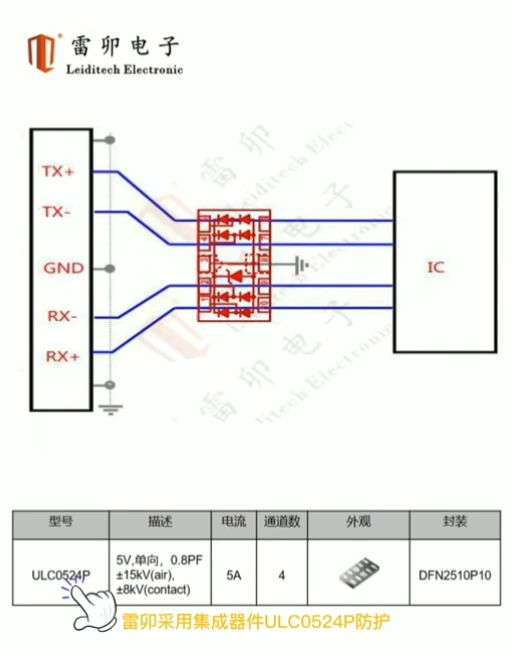

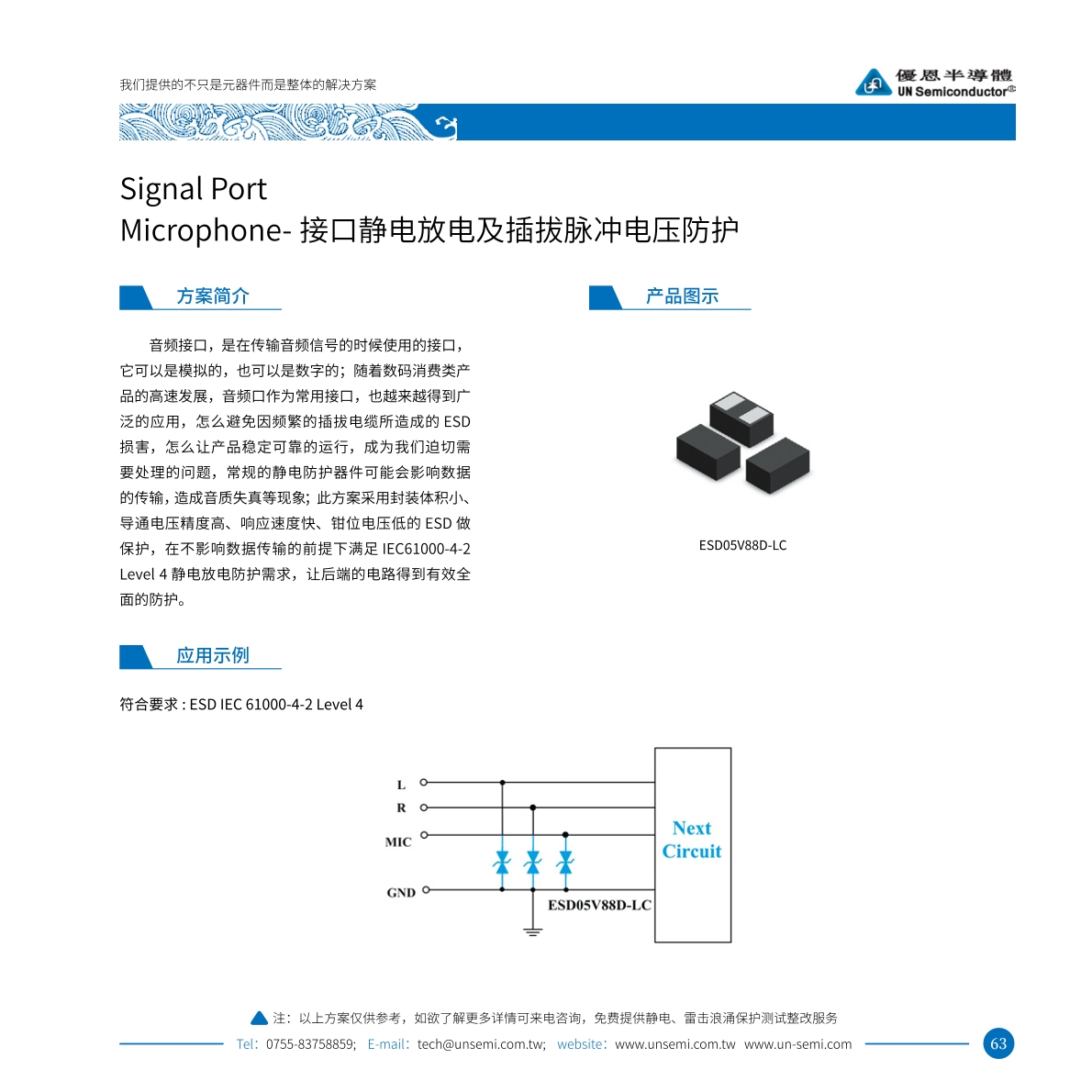

SoC芯片组装系统后,按照IEC-61000-4-2标准进行电子枪接触放电或者空气放电测试的时候,还会有芯片重启、芯片管脚电路烧坏等现象出现,有些现象可以通过串联外接电阻,并联TVS防护器件解决。传统的防护观念认为这是系统级别防护的问题,需要系统级别进行优化。但在芯片设计阶段也应有相应的方式给予提升,比如在芯片FloorPlan设计阶段,可以对于芯片敏感信号例如CLOCK/Reset信号进行隔离,IO/ESD单元库设计阶段对特定管脚提高耐压度等,可以使得系统级别实现达标更为容易,这些需要静电防护设计团队结合芯片级、封装级、系统级等各设计阶段给予考虑。

高速接口性能需求所带来的静电防护设计挑战

先进工艺的使用,使得高速接口设计指标可以不断攀升,ESD防护电路中过大的寄生电容将会使得电路带宽受损,影响性能。实际设计中我们使用T-Coil防护结构,ESD和模拟电路设计,经过多次的迭代,在不损失静电防护性能的情况下保证了电路带宽性能的达标,图8展示了我们协同设计的效果。

图7:High Speed Serial Link Data Rates and HBM Protection levels vs Capacitive Loading requirements

(来源:Industry Council on ESD Target Levels)

图8:T-Coil结构优化前后仿真对比

完善而先进的SoC静电防护

设计方法和流程

大型复杂SoC项目的实现往往是由不同团队共同协作完成,从基础的模块设计到芯片顶层集成各开发节点,如何把静电防护相关的各环节(如图9所示)嵌入到整个项目的开发流程中,是一个巨大的挑战。芯耀辉有完整的SoC静电防护设计方法、流程和工具,让各个设计团队可以逐层确保IP/Die/Chip的静电防护能力,从而保证SoC Chip系统芯片静电防护顺利达标。

图9:SoC ESD设计流程环节

以实际设计为例,静电防护设计工程师推荐的防护方案,在实际的电路实现中有可能会有偏差,如图12所示,以致无法完全达到理想的防护效果。完善的防护流程则可以有效的避免此类偏差的出现。

图10:推荐方案和实际实现之间的不符合

自主开发的静电防护可靠性

设计的自动检查流程和工具

为应对设计的高复杂度和巨大工作量,基于EDA工具的ESD自动化检查方案应运而生,芯耀辉科技ESD团队总结大量的量产实战经验后形成规则建议,并由公司CAD团队自主开发了ESD可靠性设计的自动检查流程方案,分别覆盖:(1)电路级别检查(2)版图级别检查(3)静电防护通路寄生电阻(P2P)和电流密度检查(CD)

图11:自主开发的ESD可靠性设计自动检查流程方案

图12是电流密度(CD)检查的一条示例,以HBM 2KV为例,注入的ESD电流等效为1.33A,如果放电路径Diode Metal宽度或者VIA个数不能支撑2KV需求,则会报出该处坐标位置。另外需要提及的是,大封装规模SoC芯片CDM 500V对应的电流超过了6A,HBM 1.33A有时候并不能覆盖CDM的要求,需要设定更大的注入电流,芯耀辉自行开发的CAD Flow可以根据实际需求赋予不同的激励电流,以保证覆盖规格要求。

图12:CD path check示例

除了包含Chip level ESD/Latch-up相关的检查和设计规则以外,在量产阶段,ESD失效也经常包含了RDL/Package等相关的设计问题而导致的静电防护失效,芯耀辉的静电防护设计团队也在这些方面积累了大量的失效分析和处理经验。一些实际量产中的失效案例在相关文献中也有过许多报道。

静电防护防护规则自动化检查流程的建立,一方面使得静电防护工程师免于人工检查面对的巨大工作量,也使得集体经验能够得以积累和传承,使得产品质量能够以精确的量化数据来支撑。

总结

静电防护设计在之前一直被认为是半导体设计中的炼金术和黑魔法,高度依赖实践的经验,但实际更需要扎实的理论支撑以及系统性的设计方法。大量的实际工艺器件的试验数据仍然是重要的静电防护设计基础;复杂的设计和需求使得静电防护设计和模拟电路、硬件系统之间的联合设计也越来越多,完善而先进的SoC静电防护设计方法和流程使得SoC设计的各团队能够有明确的实现方法来保障芯片级及系统级的静电防护能力;自动化检查的方法和流程作为实际测试数据、团队经验的总结,使得芯片的静电防护性能在Tapeout之前就具备扎实的设计理论数据作为支撑。

芯耀辉的静电防护设计团队拥有完整的静电防护解决方案,结合静电防护技术、自动化工具的检查方法和流程、联合设计的方法和流程,以保证芯片静电防护的达标。当复杂度越来越高、速度越来越快的SoC设计给芯片设计带来了巨大的挑战,芯耀辉已经具备为客户提供解决先进工艺下所涉及的各项挑战的能力,用高质量IP和完整的SoC前后端服务,帮助合作伙伴加速SoC开发,助力客户SoC量产。

来源:芯耀辉科技

-

静电保护

+关注

关注

1文章

193浏览量

19202 -

芯耀辉

+关注

关注

2文章

38浏览量

9925

发布评论请先 登录

相关推荐

芯耀辉DDR PHY训练技术简介

芯耀辉科技展示在静电保护方面的策略

芯耀辉科技展示在静电保护方面的策略

评论