本文作者:Guozhi XuCadence公司 DSG Product Validation Group

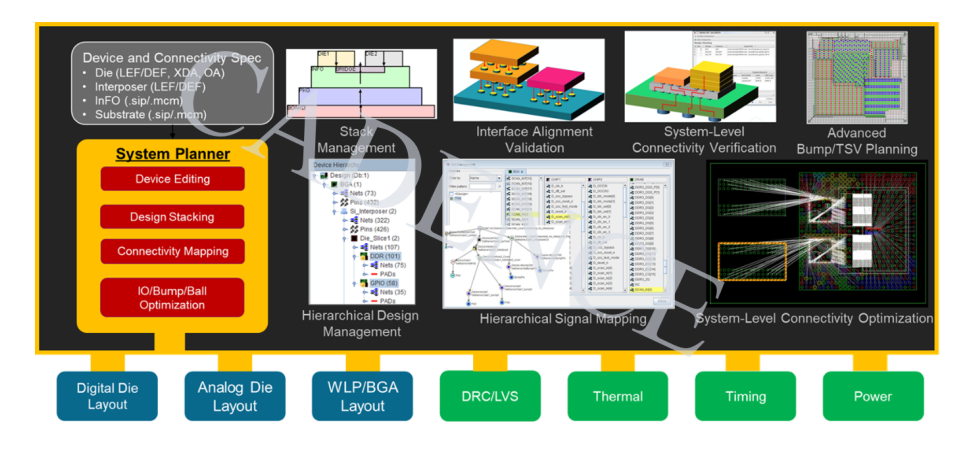

Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

近几年,随着摩尔定律的失效,集成电路的设计发展逐渐从传统的二维平面转向立体,人们获得了三维带来的诸多优势,比如:更短的引线、更低的功耗、更高的性能和带宽、更小的封装尺寸、以及更好的良率,但同时三维设计也带来了新的挑战:例如设计的聚合与管理、额外的系统级验证等。

过去行业中的解决方案多借助于点工具搭建的流程,裸片和裸片、裸片和封装之间的设计缺少联系,无法进行早期的探索和获得反馈。为了使集成后的系统仍能满足设计要求,必须过度设计以留下余量,造成性能受限并且成本高昂。

Cadence 在 2021 年推出的 Integrity 3D-IC 平台,正是为了应对这些挑战而设计。

Cadence Integrity 3D-IC 平台集成了 3D 设计规划与物理实现,能够支持系统级的早期和签核分析,全面完整地助力设计者实现由系统来驱动的 PPA 目标。

3D-IC的流程包括从系统级规划,到单个芯片物理实现,再到系统级分析和验证。

今天我们主要介绍:

Cadence Integrity 3D-IC 系统级规划

1.系统级规划和优化

2.系统连接性检查

3.Integrity 3D-IC 与系统分析工具的融合

1. 系统级规划和优化

芯片的堆叠

Feedthrough 的插入

Bump 的规划与优化

3D 图形界面

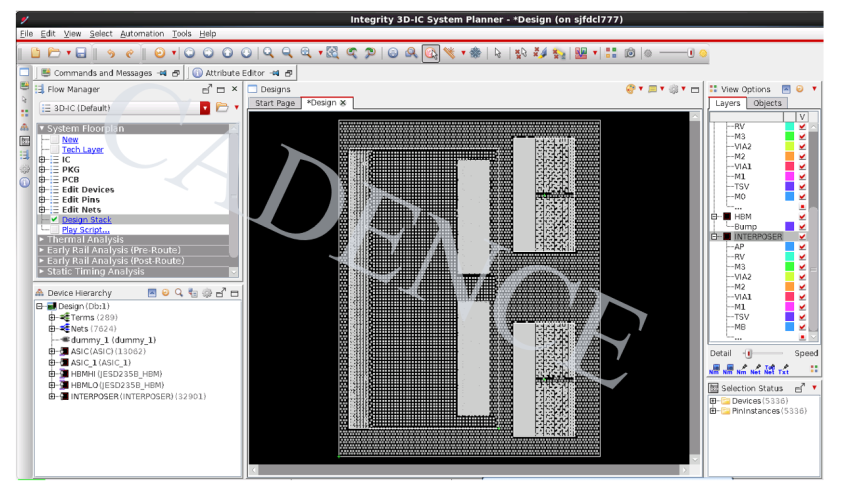

在传统的 3D-IC 设计当中,系统级规划通常是通过人工规划来实现的。这使得系统级的更新需要比较长的迭代周期。Integrity 3D-IC 系统级规划工具可自动高效地实现芯片的堆叠、feedthrough 的插入、Bump 的规划和优化等功能。工具可以实时显示每个操作的结果,让用户对于设计的结果一目了然。

与此同时,TCL 命令的引入让用户可以像使用数字后端工具一样,通过脚本来进行系统设计和定制自动化流程。这也是 Integrity 3D-IC 平台最为突出的特点之一。

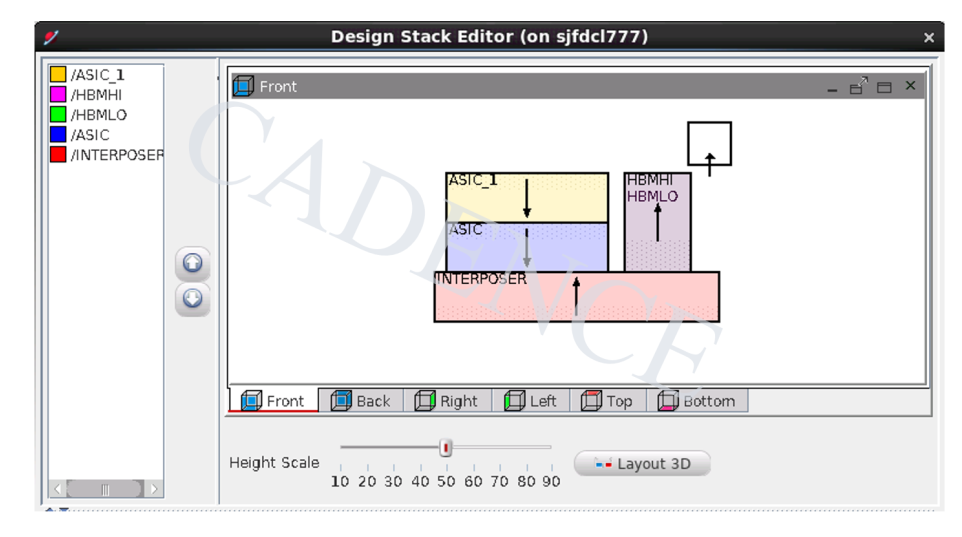

芯片的堆叠:

在 Integrity 3D-IC 当中,用户可以在图形界面上或者 TCL 命令轻松地更改芯片的摆布和堆叠。Integrity 3D-IC 支持所有的堆叠方式,包括 Face-to-Face, Face-to-Back, Back-to-Back 和 Back-to-Face。堆叠方式更新的结果也能够实时显示在图形界面上。

Feedthrough 的插入:

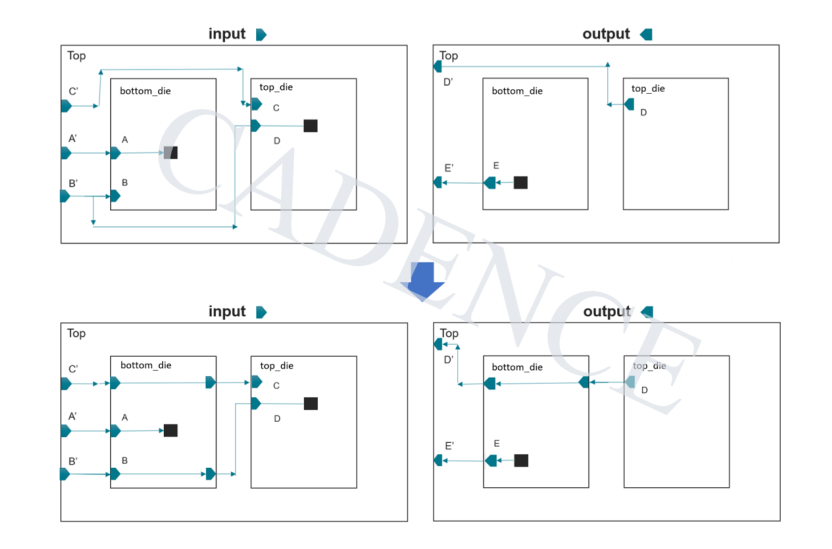

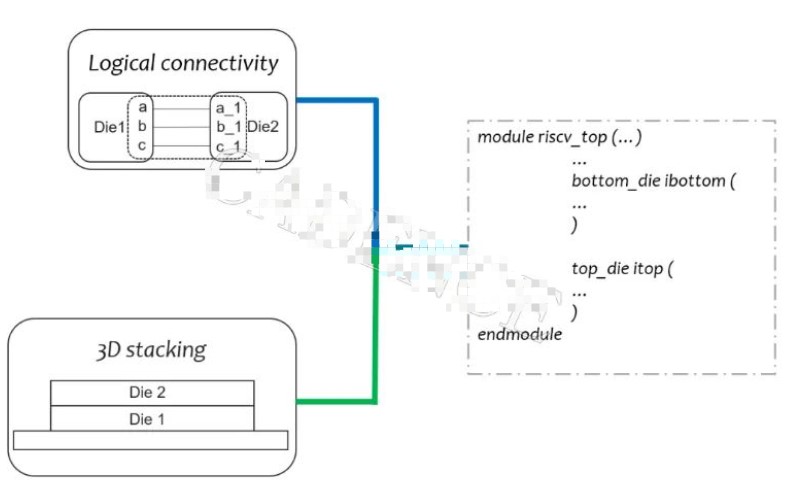

系统的输入输出通常存在于封装上,上层芯片输入输出信号有时候需要穿过下层芯片,而并不与下层芯片发生数据交换,这样的路径我们称为 feedthrough。比如在下图所示的系统中,bottom_die 当中的路径A起到了连接 top_die 和封装 PKG 的作用。这样的路径就是 feedthrough :

然而,feedthrough 路径可能并没有被插入到下层芯片的逻辑网表当中。比如上图所示路径A,就可能直接由 PKG 的端口连接到 top_die 的端口。Integrity 3D-IC 提供了自动插入 feedthrough 的功能。

在下图当中,我们列出了一些比较常见的 feedthrough 的插入:

Bump 的规划与优化:

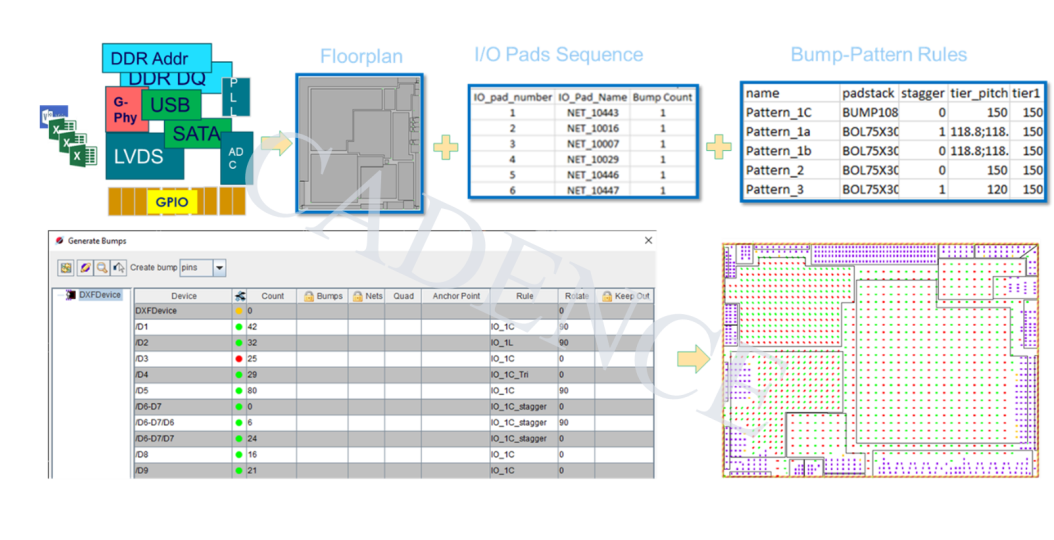

Bump 的规划和芯片当中的功能模块密切相关。如果 Bump 距离功能模块的输入输出太远,会对时序产生不好的影响。Integrity 3D-IC 可以快速地完成基于芯片功能模块的 Bump 规划。用户可以分区域指定 Bump pattern(包括Bump cell,Bump pitch,stagger等),从而可以对不同的 power domain 或 IP block 区域创建不同的 Bump,如下图所示:

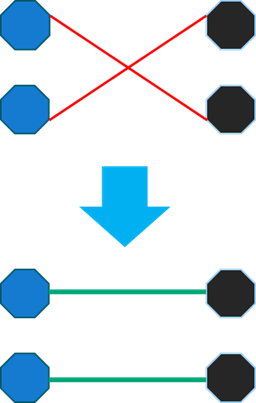

Bump 规划完成之后,需要检查 Bump 之间的连接关系有没有交叉的部分。如果发生交叉,对后续的 Bump 绕线有比较大的影响。我们最好能够在系统级规划的阶段解决交叉的问题,避免绕线完成之后再进行迭代。

Integrity 3D-IC 提供了一种自动解决连接交叉的方案:

将比较关键的 Bump 端固定,对另一端进行自动优化。经过优化,达到 Bump 连接交叉比较少的状态,从而让后续 Bump 绕线变得更加容易。

3D图形界面:

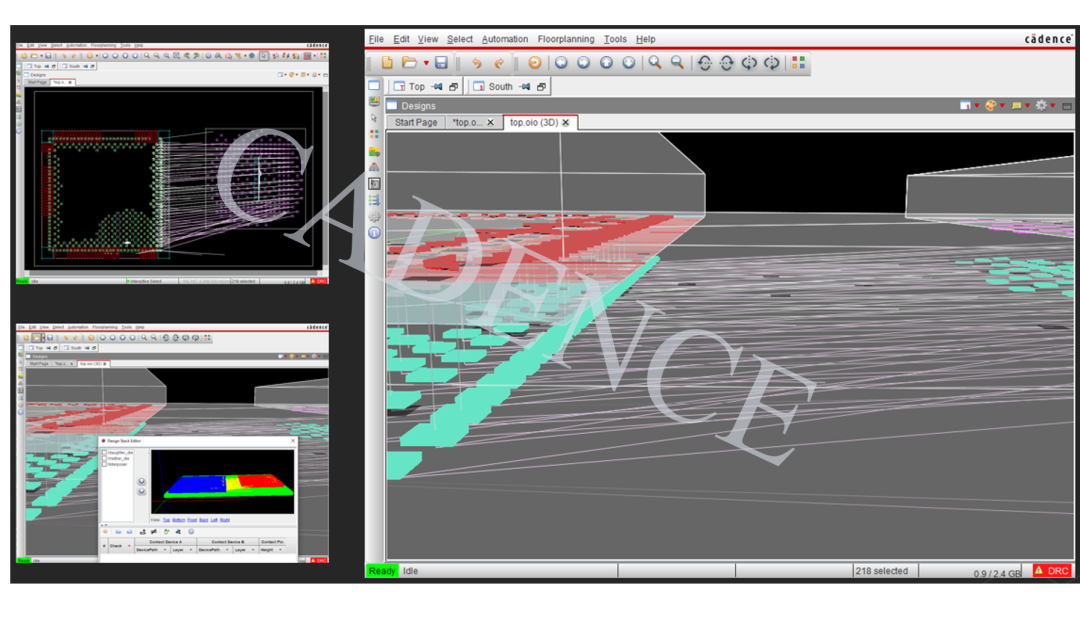

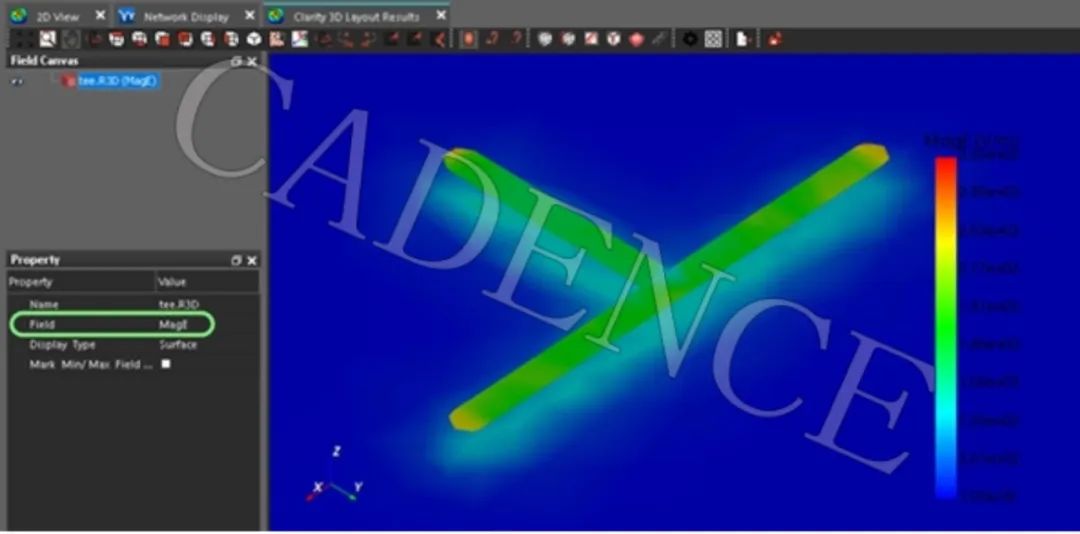

芯片设计进入三维之后,连接关系也从平面走向立体。Integrity 3D-IC 推出了三维图形界面,让 3D-IC 设计更加直观具体。

2.系统连接性检查

芯片间接口连接性实时自动检查

系统连接关系图

在 3D-IC 设计中,芯片间接口连接性是非常关键的,会直接影响最后的 LVS 核签。Integrity 3D-IC 提供了自动检查和手动检查两种方式。

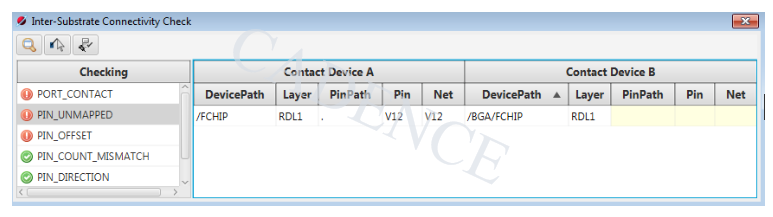

芯片间接口连接性实时自动检查:

Integrity 3D-IC 提供了实时自动检查的功能,用来检查做完 Bump 规划和优化之后,Bump 的物理连接关系是不是和逻辑连接关系一致。这个检查是实时的,不需要通过LVS签核工具来进行迭代。

如果有悬空的 Bump、Bump offset、不正确的 Bump 物理连接等问题都会被报出来。用户可以在早期解决这些问题,从而避免在物理实现做完之后才通过 LVS 核签工具发现这些问题,增加迭代的周期。这个检查有一点类似于 Innovus 当中的 connectivity check。

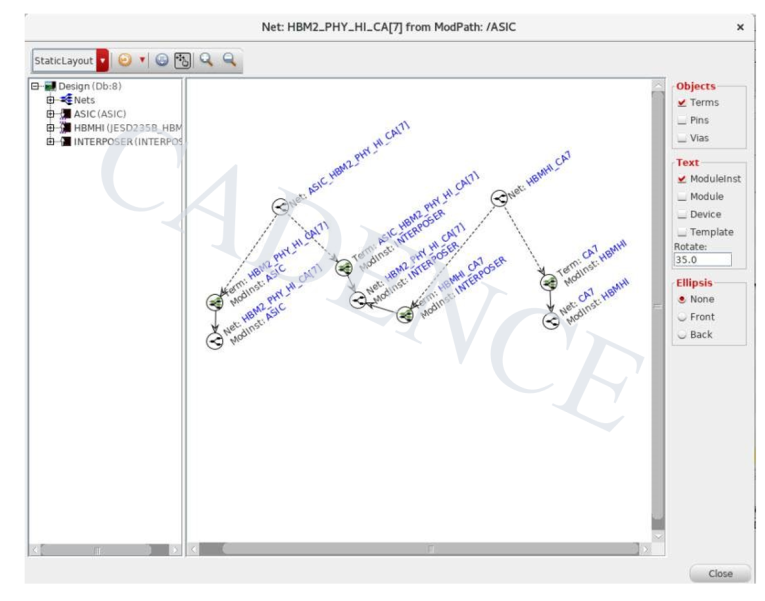

系统连接关系图:

在系统连接性检查当中,用户如果想对某一条路径的连接性进行 debug,可以使用 Integrity 3D-IC 的系统连接关系图。这个图可以将特定路径的全部系统连接关系显示出来。用户可以基于结果进行调试。

3.

Integrity 3D-IC

与系统分析工具的融合

在做完系统级规划之后,我们希望能够直接进入物理实现工具做芯片物理实现,或者进入分析和验证工具做早期系统分析验证。

Integrity 3D-IC 和 Cadence 的数字后端工具 Innovus、模拟版图工具 Virtuoso、封装设计工具 Allegro 工具等都实现了不同程度的集成。不同工具之间可以实现数据的无损交换和设计环境的自由切换。

Integrity 3D-IC 也提供了和部分常用 Cadence 分析工具的接口,包括热分析工具 Celsius、功耗分析工具 Voltus、静态时序分析工具 Tempus、物理验证工具 Pegasus。工具提供了 Flow Manager 的图形界面,来方便用户方便地使用各种分析验证工具,而不受制于分析验证工具使用经验这部分内容我们后续会做具体详细的介绍,这里就不再赘述。

至此,我们简单地介绍了 Integrity 3D-IC 系统级规划平台的特点,包括系统级规划和优化、系统连接性检查、Integrity 3D-IC 与其他工具的融合。希望 Integrity 3D-IC 能够方便越来越多工程师的系统设计,加速优秀的芯片产品落地,推动后摩尔时代的发展。

Integrity 3D-IC 介绍:

Cadence Integrity 3D-IC 平台提供了一个高效的解决方案,用于部署 3D 设计和分析流程,以实现强大的硅堆叠设计。该平台是 Cadence 数字和签核产品组合的一部分,支持 Cadence 公司的智能系统设计战略(Intelligent System Design) ,旨在实现系统驱动的卓越 SoC 芯片设计。

关于 Cadence

Cadence 在计算软件领域拥有超过 30 年的专业经验,是电子系统设计产业的关键领导者。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续八年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 cadence.com。

2022 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

-

集成电路

+关注

关注

5391文章

11618浏览量

362930 -

IC设计

+关注

关注

38文章

1302浏览量

104221 -

封装

+关注

关注

127文章

7990浏览量

143329 -

Cadence

+关注

关注

65文章

930浏览量

142388 -

3DIC

+关注

关注

3文章

83浏览量

19438

原文标题:3D-IC 设计之如何实现高效的系统级规划

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cadence携手TSMC开发3D IC设计基础架构

如何建立正确的3D-IC设计实现流程和实现项目高效管理的挑战

Cadence推出Clarity 3D场求解器,拥有近乎无限的处理能力

Cadence 凭借突破性的 Integrity 3D-IC 平台加速系统创新

TSMC 和 Cadence 合作开发3D-IC参考流程以实现真正的3D堆叠

Cadence Integrity 3D-IC平台Ô支持TSMC 3DFabric技术,推进多Chiplet设计

Cadence Integrity 3D-IC平台进行工艺认证

Cadence Clarity 3D Solver 2022版本发布 电磁设计同步分析功能提高效率

3D IC制造技术已成主流,异构3D IC还有待进步

Cadence Integrity 3D-IC Platform荣膺“年度EDA/IP/软件产品”

7.2小时完成868个HBM封装端口——Cadence Clarity 3D Solver仿真案例详解

产品资讯 | 3D-IC 设计之自底向上实现流程与高效数据管理

Cadence 扩大了与 Samsung Foundry 的合作,依托 Integrity 3D-IC平台提供独具优势的参考流程

系统分析大讲堂:Clarity 3D Solver 课程新内容

Cadence分析 3D IC设计如何实现高效的系统级规划

Cadence分析 3D IC设计如何实现高效的系统级规划

评论