从正式发布至今,PCI Express®(PCIe®)发展迅速,在现代数字世界中无处不在,已经成为高性能计算、人工智能/机器学习(ML)加速器、网络适配器和固态存储等应用不可或缺的一项技术。不仅如此,PCIe技术近期在速度和延迟方面取得的突破让其在存储器架构中也获得了广泛应用(例如通过PCIe/CXL插槽连接的持久内存和DRAM)。

人工智能/机器学习(ML)应用的变革以及企业工作负载加速迁移至云端的趋势,持续推动数据流量前所未有的增长。为了应对未来对数据带宽的需求,PCI-SIG于2019年发布了PCIe 6.0,将数据传输速率翻倍至64GT/s。最终版PCIe 6.0标准已于2022年1月正式发布。

IO带宽增长预测和PCIe标准的演化(图片:Cadence)

PCIe 6.0的主要挑战

将I/O带宽从PCIe 5.0的32GT/s翻倍至64GT/s给信号完整性(SI)带来了巨大挑战。PCIe向后兼容的需求必须持续支持PCB、连接头和扩展卡等传统通道。数据速率为32GT/s且采用不归零制(NRZ)编码时,传统通道的插入损耗总和在奈奎斯特频率(16GHz)下可达到36dB以上;当速率提升至64GT/s NRZ时,奈奎斯特频率翻倍至32GHz,通道的频率相关损耗将增加到70dB以上。如此的全通道信号损失将令噪音完全无法识别,传输的数据将无法被有效还原。

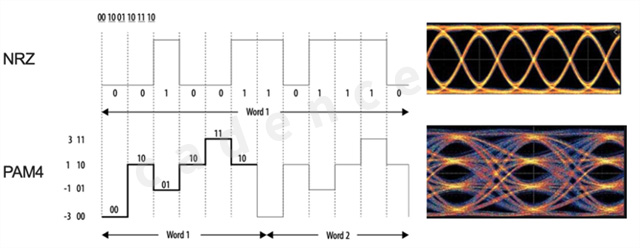

PAM4加持PCIe

将信号调制模式从非归零编码(NRZ)改至四电平脉冲幅度调制(PAM4)是PCIe 6.0克服通道信号损失挑战的方法。PAM4是一种多电平信号传输技术,每个单位时间(UI)传输2比特,而NRZ每个单位时间仅传输1比特(见图2)。采用PAM4信号调制技术的PCIe 6.0每个UI可以传输2比特数据,数据速率在奈奎斯特频率不变的情况下增加一倍,成为PCIe 6.0的一大优势。通道损失也因此与PCIe 5.0一样可控。

PAM4信号调制(图片:Cadence)

然而,升级至采用PAM4信号调制的PCIe版本还需要解决一系列挑战,并应对因此导致的复杂性上升。幸运的是,Cadence对PAM4并不陌生。早在2017年,Cadence就通过对Nusemi公司的收购开始研发112Gb/s的PAM4技术。今天,Cadence已经是多个先进FinFET节点下112G/56G PAM4 SerDes IP的领先供应商,客户使用我们的IP已经开发出多项成功的芯片设计。

协议更新,为效率而生

PIPE到控制器的接口也升级到了6.0版本,延迟进一步降低。

PCIe 6.0标准引入了流控制单元的概念(FLIT),与PAM4所需的前向纠错(FEC)高效协同,为采用最常见配置的主流负载提供更低的延迟。

PCIe前代版本通过动态链路带宽和低功耗状态实现节能。但在此过程中,动态链路带宽会干扰数据流的传输。PCIe 6.0采用全新的低功耗状态L0p,可在不干扰数据流的前提下允许功耗相对带宽的按比例调整。

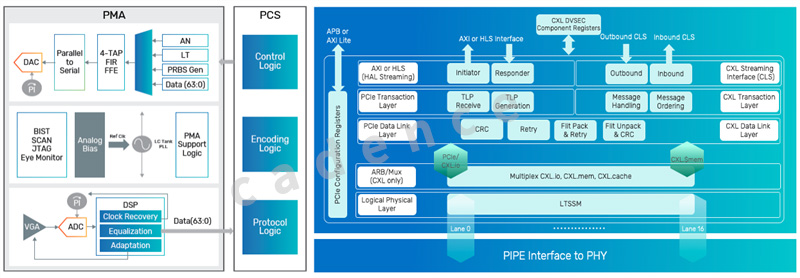

Cadence针对PCIe 6.0的完整IP解决方案

Cadence的PCIe PHY和控制器解决方案(图片:Cadence)

Cadence致力于引领行业采用最新的PCIe 6.0标准,用PCIe 6.0 IP解决方案应对前沿领域快速变革的技术需求。过去20年,Cadence一直是PCIe PHY和控制器的领先供应商。采用Cadence领先的PAM4技术以及经过验证的112G/56G PAM4以太网PHY IP,结合在PCIe领域深厚的经验,Cadence致力于为市场提供最先进的PCIe 6.0 PHY和控制器IP。

-

PCIe

+关注

关注

15文章

1278浏览量

83532 -

人工智能

+关注

关注

1799文章

48000浏览量

241758 -

复杂系统

+关注

关注

0文章

7浏览量

7002

发布评论请先 登录

相关推荐

如何加速实时操作系统的硬件?

一文读懂教育直播系统开发模式

如何降低开发难度,有哪些难度

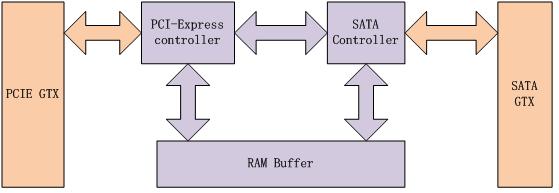

支持第三代6.0Gbps的PCIE-SATA适配器系统IP

软件无线电中双缓冲模式PCIE总线的设计与实现

Arduino单片机系统开发设计(Proteus虚拟技术)

楷登电子发布PCIe 6.0规范Cadence IP

利用辅助工具SIG为OpenHarmony操作系统开发化解疑难

PCIe 6.0的新变化与新挑战

PCIe 6.0入门之什么是 PCIe 6.0

成熟的PCIe 6.0 IP可极大降低复杂系统开发难度

成熟的PCIe 6.0 IP可极大降低复杂系统开发难度

评论