概述

USB-2432采集卡是一款基于USB2.0总线,高速、高精度32通道同步采集卡,高达24位精度、256KSPS采样率。支持外触发和软件触发。32路差分信号及触发信号通过板上的SCSI68端子输入。

USB-2432模拟量输入信号采用差分输入方式进入ADC转换,AD转换结果存储在大容量存储器SDRAM(容量4M字)中。AD芯片自带差分放大器和数字滤波器。

USB-2432卡的USB主控芯片采用CYPRESS公司的CY68013A。本板是一款USB2.0总线高速、高精度数据采集板,支持热插拔,即插即用。运用现场可编程门阵列FPGA设计,提高可靠性。

出厂时提供XP/WIN7/WIN10下驱动程序和动态链接程序(DLL)及编程指导(DEMO程序),有VB/VC/LABVIEW采集程序例程,并提供两年的质保服务。

产品应用

USB-2432是一款基于USB2.0总线的数据采集卡,可直接和计算机的USB口相连,构成实验室、产品质量检测中心等各种领域的数据采集、波形分析和处理系统。也可构成工业生产过程监控系统。它的主要应用场合为:

▪ 电子产品质量检测

▪医学检测

▪高精度信号同步采集

▪IO控制

性能特点

▪A/D转换器:24-bit Σ-Δ型ADC:AD7768

▪本体噪声低,通道隔离度高;

▪差分输入范围:±10V;

▪AD触发方式:软件触发、外触发;

▪工作时钟:内时钟、外时钟(可选择同步时钟/触发时钟);

▪多通道:32通道

▪采样频率可软件设置(范围:1KHz~256KHz/1KHz~200KHz/1KHz~160KHz模式可选);

▪板载大容量存储器(4M字),支持连续采集,实现实时监控;

▪板卡ID识别(0~15),支持多卡操作;

▪提供WIN7/WIN10/XP下驱动程序及动态连接库;

▪尺寸大小(不含外壳):92(W) × 140(L) (mm);

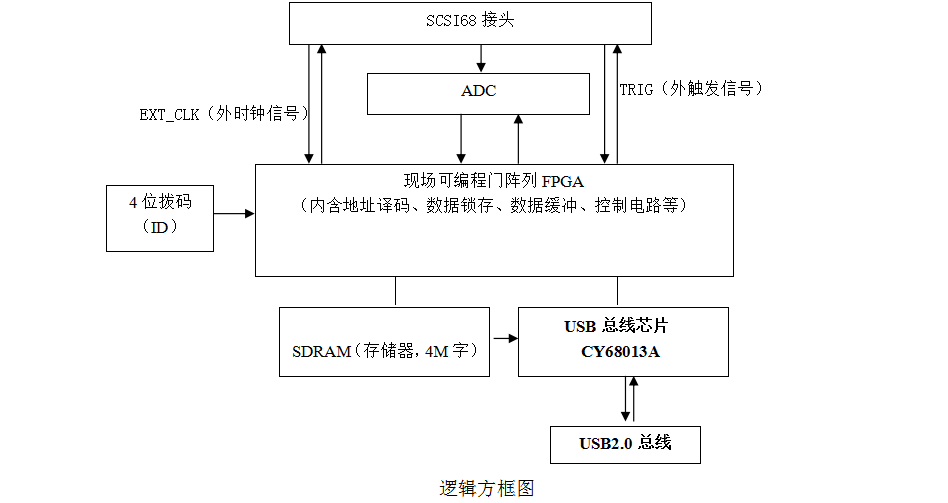

1、逻辑框图

2、工作原理简述

USB-2432由以下功能模块组成:USB2.0总线桥电路,AD转换,数据存储等功能组成。

地址译码:由现场可编程门阵列FPGA芯片控制。由于是USB2.0总线,用户可以不关心具体I/O地址,直接调用我公司提供的动态连接库即可。

AD转换:外部模拟信号由SCSI68接头接入,经过前级运放,进入ADC,AD控制时序由FPGA完成。

数据存储:AD转换的结果存储在SDRAM中。读、写数据的时序由FPGA控制。

3、工作模式

3.1、软触发

在这种模式下,用户配置采样频率和同步通道后,启动AD,便可进行连续不间断采样,每一通道都能达到设定的采样频率,各通道之间无相差。

3.2、外触发

在这种模式下,需要接入外触发信号,用户配置采样频率和同步通道后,启动AD,AD并不马上开始工作,而是等待外触发信号到来,给与有效的电平后,AD开始工作。

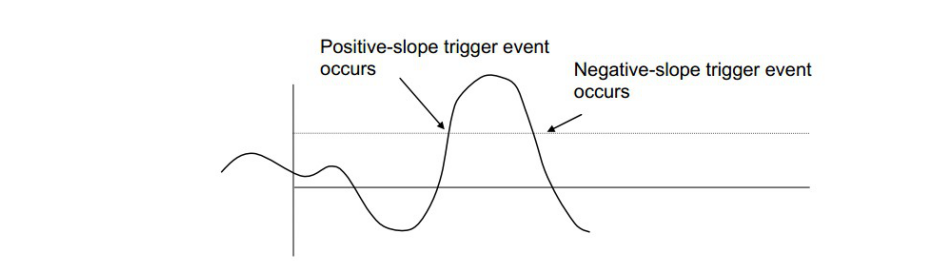

在这种模式下,触发源为模拟信号(模拟触发)或TTL电平信号(数字触发),模拟信号幅值在0V -- +5V之间,信号越平滑越好,如下图示;

外触发默认为输入模式,输入外触发信号。多卡时可将外触发引脚通过跳线设置为输出模式,用以提供外触发信号。

3.3、外时钟

外时钟模式可选择外触发时钟模式或者多卡同步时钟使用。外触发时钟模式:采样频率由该时钟确定,每个CLK上升沿采集一个点;同步时钟:用于ADC工作时钟,需提供特定的时钟,才可正常工作。

4、SDRAM中数据存放顺序

本卡采用SDRAM FIFO化的技术,数据位宽为16位(D0~D15),32路模拟信号(CH0~CH31)通过AD转换以后,结果存放在FIFO中。以四通道同时工作为例,其他依此类推。软件可任意勾选几个通道同时工作。一个通道的转换结果占用4个字节,其中数据占3个字节,1个字节的状态位。

以选择4通道为例:CH1、CH2、CH3、CH4的转换结果依次存放在FIFO中的第1、2,3、4,5、6,7、8个位置,第二轮CH1、CH2、CH3、CH4的转换结果依次存放在FIFO中的第9、10,11、12,13、14,15、16个位置。。。依此类推(分两次写,一次写16bit)

32路同步的情况,CH1、CH2、…、CH31被同步采样;各通道之间无相差。数据交织存放。具体可参照DEMO软件。

5、FIFO容量

本卡采用1片SDRAM,容量为4M字,FPGA将SDRAM FIFO化,USB主控芯片内含1K字FIFO,所以本板总的FIFO容量为:硬FIFO+软FIFO = 4M字+1K字(构成海量FIFO),上位机一次读取18432个字节的数据量,该数据量能被2、3整除,分配到每个通道上的数据是一样多。

上位机是一次读取18432个字节,也可以更多或更少,但必须是512的倍数,因为USB端点2数据满512字节时,才打包提交。同时,为了上位机处理方便,一次读取的字节数最好能被(通道数×4)整除。

6、批量数据的传输

USB的主控芯片的端点2我们配置为批量读方式,端点0配置为控制传输,当外部FIFO(SDRAM)不为空且USB端点2的FIFO不满,USB就自动从外FIFO中读取一个数至内FIFO中,当端点2数据满512时,就自动打包提交。

外部FIFO(SDRAM)满标志为高时,代表数据有溢出,应当停止AD,清空FIFO后,重新开始采样。否则FIFO中的数据存放顺序会被打乱。

由于USB主控芯片采用胶链接,与16位宽度的SDRAM无缝对接。

审核编辑:符乾江

-

数据采集

+关注

关注

39文章

6180浏览量

113795 -

振动信号

+关注

关注

0文章

23浏览量

8864 -

声音信号

+关注

关注

0文章

9浏览量

6677

发布评论请先 登录

相关推荐

如何选择适合您需求的采集卡

如何使用图像采集卡

图像采集卡:增强视觉数据采集

多通道数据采集卡各通道不独立的原因

数字采集卡的功能介绍

数字采集卡有哪些 数字采集卡的作用是什么

数字采集卡通过什么接口传输

数字采集卡属于什么设备类型

数字采集卡有哪些类型

图像采集卡的选择技巧

ni数据采集卡的工作原理解析

图像采集卡的工作原理是什么?

机器视觉图像采集卡:关键的图像处理设备

多通道同步采集卡的性能特点及工作原理的说明

多通道同步采集卡的性能特点及工作原理的说明

评论