半导体设备技术和工艺控制的不断进步,加上制造亚微米尺寸器件对衬底清洁度提出的更严格要求,重新引起了人们对汽相HF氧化物蚀刻技术的兴趣,在文中描述了一种系统

我们华林科纳通过将氮气通过HF水溶液引入HF蒸汽,为了最小化由于蒸发导致的源组成的变化,可以使用38.26重量% of的共沸混合物。

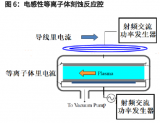

这项工作使用的反应器的示意图中,该反应器由一个惰性碳化硅反应室和两个装有适当溶液的加热蒸发器组成,电容器既不接受氧化后惰性环境,也不接受金属化后形成气体退火,

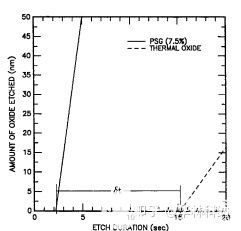

培养时间和蚀刻速率,用汽相HF氧化物蚀刻可以实现两种不同的蚀刻选择性模式,各种硅氧化物和氮化物的蚀刻速率列于表中,与含水HF的情况一样,对于不同的硅氧化物,气相等效物表现出不同的蚀刻速率,从而产生蚀刻选择性,从热生长到沉积氧化物,以及从未掺杂到掺杂氧化物,蚀刻速率增加,尽管氮化硅的低蚀刻速率使其成为硅氧化物的合适蚀刻掩模,但应该注意的是,气相HF,像其含水对应物一样,产生各向同性蚀刻。

在蚀刻过程开始时,存在发生可忽略蚀刻的时间,该培养时间与在晶片表面形成薄水膜所需的时间有关。如图所示,对于不同的氧化物,孵化时间是不同的,这产生了第二种蚀刻选择性,在热氧化物的培养时间内的时间间隔8t中,PSG的非零蚀刻速率意味着PSG对热氧化物的无限蚀刻选择性,这种现象的一个具体应用是从包含热氧化物作为成分之一的电介质材料的图案化叠层中选择性去除掺杂氧化物,通过执行具有由抽空/解吸步骤分隔的几个蚀刻循环的多步蚀刻工艺,无限选择性的持续时间可以进一步增加到8t以上。

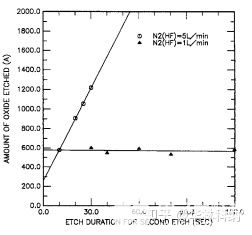

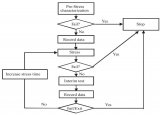

为了区分长培养时间和短培养时间与可忽略蚀刻速率的可能组合,设计了连续多步蚀刻工艺来表征在减少的氮载气流量下的热氧化物蚀刻速率,结果总结在下图,第一步包括用流速为15升/分钟的氮气载气进行10秒钟的蚀刻,随后的步骤是可变时间蚀刻,其中氮载气的流量减少,同时通过注入额外量的纯氮气将通过蚀刻室的总流量保持在15升/分钟的恒定值,第一步导致浓缩膜的形成,因此,第二步的有效培养时间基本为零,在第一步和向第二步过渡期间,蚀刻的厚度略小于60纳米,对于5升/分钟的氮载气流速,使用该技术测量的蚀刻速率为3.2纳米/秒,而当流速进一步降低至1升/分钟时,基本上没有观察到蚀刻。

在较低流速下较长的培养时间可以理解为H2O蒸汽分压随着载气流速的降低而降低,对这种培养时间对H2O蒸汽分压的依赖性的进一步验证来自于对固定注射HF的观察,培养时间随着H2O蒸汽注射量的增加而减少,例如,当10升/分钟的氮气流被转移通过H~O蒸发器时,热氧化物蚀刻的培养时间下降到小于5s。

对于掺杂氧化物膜,蚀刻速率进一步受到与膜致密化工艺相关的热处理的影响,BPSG的固定持续时间蚀刻的结果在表中,除了在氮气环境中于850℃退火20分钟的薄膜外,致密化实际上导致了氧化物的更多蚀刻,这是由更快的蚀刻速率或保温时间的减少引起的。未致密化膜和在850℃退火的膜的腐蚀速率是相当的,而致密化膜的保温时间是沉积态膜的两倍多一点,对于相同的工艺参数,PSG膜的腐蚀速率通常比BPSG膜的腐蚀速率高,而相应的培养时间较短,例如,当用5升/分钟的氮气载气流速蚀刻PSG时,蚀刻速率和培养时间分别为17.2纳米/秒和4.7秒。

在这组实验中,使用H2O含量远大于共沸组合物的蒸汽混合物,第一个观察结果是蚀刻速率远低于在具有相同HF分压的共沸蒸汽中的蚀刻速率,蚀刻速率的下降直接源于浓缩膜中HF浓度的降低,这使得蚀刻动力学对注入的少量HCl更加敏感,根据浓缩膜的pH值,可以给出观察到的孵育时间和蚀刻速率对HCl的依赖性的可能解释。

在没有H~O稀释的共沸蒸汽混合物的情况下,冷凝膜中高得多的HF浓度使得蚀刻速率和培养时间对注入少量HCl几乎不敏感,在有和没有(100 SCCM)HCl注入的情况下,蚀刻速率分别为3.2和3.3 nm/s,培养时间分别为15.0和15.4 s,对表面处理的依赖,除了蚀刻速率依赖于氧化膜的形成和掺杂方法之外,培养时间的存在还带来了另一个工艺参数,必须仔细研究其变化。

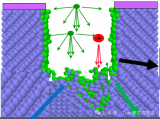

高颗粒密度有助于水在晶片表面的凝结,从而有效地缩短了颗粒周围区域的培养时间,这种成核降低了蚀刻均匀性,并导致更高的有效蚀刻速率,在一些严重的情况下,在气相HF处理的氧化物表面上可以观察到颗粒成核的腐蚀斑点,因此,为了达到可接受的工艺控制程度,氧化物表面必须保持相对无颗粒。

与典型的硅加工特别相关的表面处理的另一个例子是扩展的,将氧化物暴露在热磷酸中,通过在160℃下在磷酸中浸泡一小时,培养时间没有显著,处理后蚀刻速率提高了约18%,蚀刻均匀性提高了略小于50%,较高的蚀刻速率可能与氧化物表面的轻微掺杂有关,源自磷的非挥发性掺杂剂停留在氧化物的表面,通过降低浓缩膜的pH值而导致更高的蚀刻速率。

在NH~OH/H~OJH~O溶液中处理氧化物也对腐蚀特性有影响,在一个特定的蚀刻配置中,培养时间减少了3秒,蚀刻速率稍微降低,粒子性能-对于许多需要无自然氧化物的硅表面的工艺,通常在清洗程序的最后使用短时间的HF蚀刻来去除自然或化学氧化物,这种方法有许多缺点,在HF处理之后的水冲洗和旋转干燥步骤期间,发生了有限量的天然氧化物再生长,第二,一般认为如果HF溶液中存在颗粒和重金属,这些污染物很容易沉积在干净的硅表面上,当气相HF用于蚀刻天然或化学氧化物时,可以消除冲洗和干燥晶片的需要。

薄氧化物表征-使用具有12 nm栅极氧化物的LOCOS隔离MOS电容器研究了用气相HF蚀刻代替含水HF蚀刻的电气含义,电容器既不接受氧化后惰性环境退火,也不接受栅极形成气体退火,在将晶片分成三份之前,对晶片进行常规的预氧化清洗。

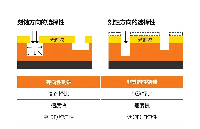

不同HF治疗组,处理是含水(1%) HF、气相I-IF和气相HF,然后用水冲洗,在所有晶片上测量了相似的有效固定氧化物电荷密度和中间带隙界面态,图中总结了斜坡电压击穿分布,观察到从含水HF到气相HF的改善趋势,并且气相HF和水冲洗的组合获得了最佳分布,随着超过四倍的改善,时间相关的介电击穿数据显示了当含水HF被气相HF替代时最显著的变化。

各种硅氧化物的气相HF蚀刻已经被广泛表征,已经开发了基于不同氧化物的培养时间变化的新方法,用于实际应用,例如在也包含热氧化物的图案化叠层中选择性去除PSG,用气相HF工艺代替传统的含水HF工艺,不仅可以获得更好的清洁度,而且可以提高薄氧化物的耐电应力性。

审核编辑:符乾江

-

半导体

+关注

关注

335文章

27835浏览量

223891 -

晶片

+关注

关注

1文章

405浏览量

31610

发布评论请先 登录

相关推荐

8寸晶圆的清洗工艺有哪些

半导体湿法刻蚀残留物的原理

芯片湿法刻蚀残留物去除方法

金属氧化物和柔性石墨烯MOS的区别

芯片制造中的湿法刻蚀和干法刻蚀

多晶氧化物中的晶界和异质界面概念、形成机理以及如何表征

使用Keithley 4200-SCS半导体表征系统进行氧化物可靠性测试

蒸汽相氟化氢对晶片清洗和氧化物刻蚀的表征

蒸汽相氟化氢对晶片清洗和氧化物刻蚀的表征

评论