引言

半导体器件的制造工程已使光电仪器、激光二极管和无线通信设备以及许多其他现代设备成为可能。从巴丁、布里泰因和肖克利1947年在贝尔实验室发明晶体管,到大约十年后基尔比和诺伊斯推出集成电路,半导体器件极大地推动了计算和电子工业的发展。

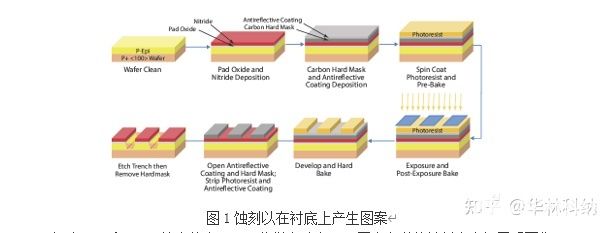

半导体材料,如硅、锗、砷化镓和磷化铟,既不是良好的绝缘体,也不是良好的导体,但它们具有固有的电学性质,因此通过控制杂质的加入,可以改变它们的导电性。由于需要制造微米级和纳米级的器件,半导体工业遵循了“摩尔定律”,即集成电路上的晶体管数量大约每两年呈指数级增长。制造这些集成电路的微小特征是通过对半导体材料进行等离子体蚀刻来实现的材料。等离子体蚀刻过程在室内进行,在室内气体混合物被部分电离以产生等离子体或辉光放电。等离子体中的高能离子轰击半导体材料,气体混合物中的化学反应成分与半导体形成蚀刻产物。这种工艺能产生精确的蚀刻特征,也是缩小设备尺寸的主要原因之一,这使得手机和笔记本电脑等技术成为可能。

介绍

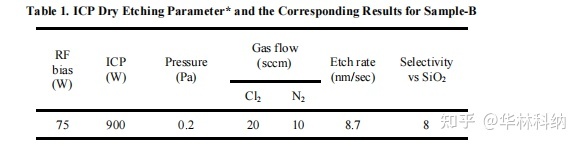

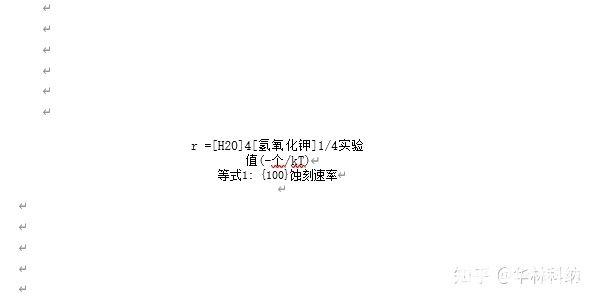

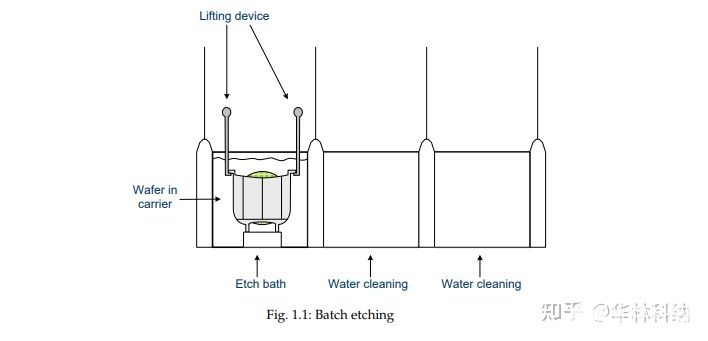

诸如InGaP和InGaAsSb的半导体对于发光器件以及通信器件和电子器件来说是重要的。这些器件的制造是通过等离子体蚀刻实现的,在等离子体蚀刻中,离子化的气体混合物通过化学反应和物理轰击来蚀刻衬底。在用于这些目的的等离子体蚀刻中,铟产物不易挥发,并且通常比其他半导体材料更难去除。对于这个实验,只有现有的晶片在下面的InGaP层上生长的外延GaAs盖层是可用的。为了发展用于InGaP层的电感耦合等离子体(ICP)蚀刻工艺,顶部GaAs层必须首先被蚀刻掉以暴露下面的InGaP层。用于做到这一点的常用技术包括选择性湿法化学蚀刻,该蚀刻将在不蚀刻或损坏InGaP层的情况下移除GaAs层。确定用于移除GaAs层的选择性和蚀刻速率是化学湿法蚀刻发展的主要目标。一旦完成,就可以创建去除外延GaAs层的“配方”。

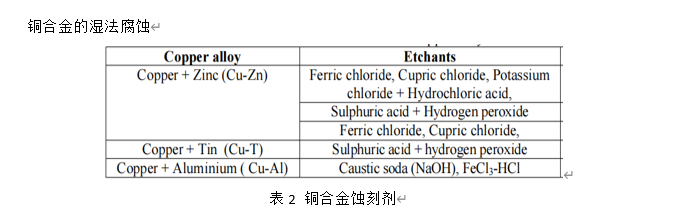

选择性化学湿法蚀刻

通过液体溶液中的一系列化学反应去除晶片的盖层。对于该蚀刻工艺,h2so 4∶H2O 2∶去离子水(去除GaAs的常用溶液)以1∶8∶640的比例使用。当半导体浸没在电解质系统中以产生Ga2O3和As2O3时,该反应发生在包括氢氧离子氧化反应的一系列步骤中。这些氧化物溶解在蚀刻溶液的酸中,形成可溶性盐。

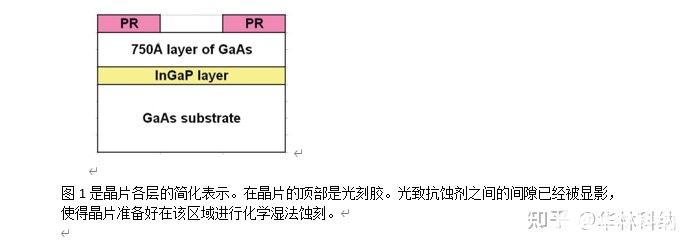

使用在顶部具有750 GaAs盖层、InGaP中间层和GaAs厚基层的晶片样品。这些晶片的层结构如下所示。后面的蚀刻将使用InGaAsSb晶片。然而,因为铟是最难蚀刻的层,InGaP是一个好的起点。

结果和讨论

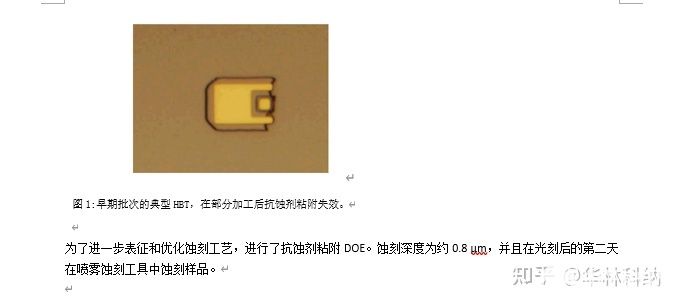

在第一轮蚀刻过程之后,结果是不确定的。似乎湿法蚀刻溶液没有选择性地蚀刻晶片。据推测,晶片可能是上下颠倒的,这意味着蚀刻的是较厚的GaAs底层,而不是750的顶层。在第二轮蚀刻过程中,小心地用划线器标记每个样品的底侧。在第二轮中还使用了控制晶片,其被有目的地翻转底侧准备蚀刻。在第二轮中,还使用了来自每种晶片类型的样品。

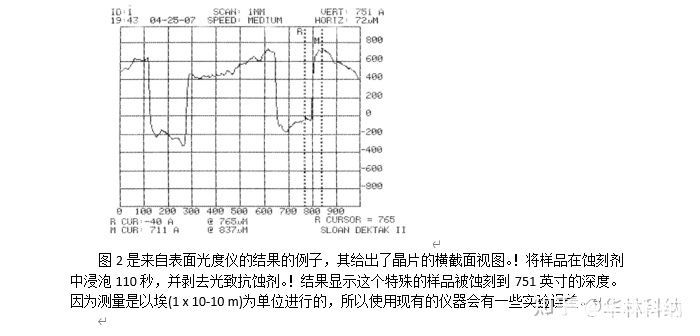

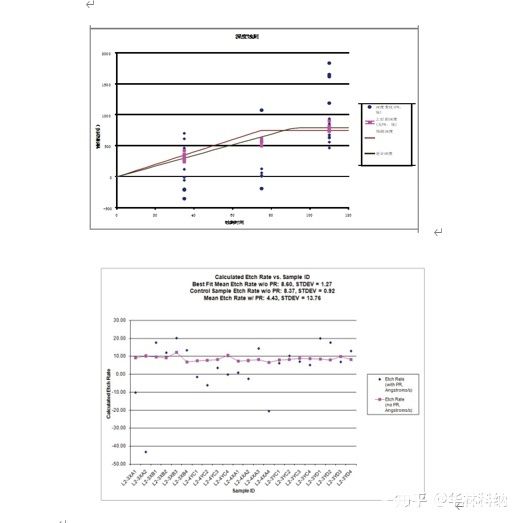

因为蚀刻溶液会侵蚀光致抗蚀剂,这可以从图3中的负蚀刻速率和图4中大于750的蚀刻深度中看出,所以必须剥离晶片上的光刻胶,以测量精确的蚀刻深度。这是通过在丙酮中搅拌晶片2分钟,用甲醇冲洗2分钟,并吹干来完成的用氮气清洗晶片。重复该过程,直到去除所有的光刻胶。然后用pro- filometer再次测量晶片,以确定实际的蚀刻速率和深度。获得了可再现的蚀刻速率,如图2所示。

3.剥离样品的蚀刻速率

PR平均值为8.37,标准偏差为0.92,接近预期的蚀刻速率10。

第二轮蚀刻过程表明,在回归分析找到数据的最佳拟合后,750 GaAs层在H2SO4: H2O2:去离子水溶液中被选择性蚀刻,平均蚀刻速率为8.6/s。结果还得出结论,湿法蚀刻停止在InGaP层,因为蚀刻时间大于去除GaAs层所需的时间仍然导致相同的蚀刻深度。在图4中,在没有光致抗蚀剂的测量中示出了蚀刻选择性,其中曲线变平。此时,所有的GaAs层被蚀刻掉,留下下面的InGaP层暴露出来。

结论

用H2SO4: H2O2:去离子水的溶液,以约8.6/s的速率,开发了从下面的InGaP层去除GaAs外延盖层的选择性湿法蚀刻工艺。在未来的工作中,这种蚀刻将用于制备晶片难以等离子体蚀刻的InGaP层,其可以通过感应耦合等离子体(ICP)中的反应离子蚀刻(RIE)来蚀刻。最后,对InGaP等离子体蚀刻速率的研究将引导对InGaAsSb蚀刻速率的研究,InGaAsSb是一种用于中红外激光二极管等应用的重要半导体。

-

半导体

+关注

关注

334文章

27010浏览量

216309 -

蚀刻

+关注

关注

9文章

413浏览量

15346 -

晶片

+关注

关注

1文章

401浏览量

31444

发布评论请先 登录

相关推荐

使用n型GaSb衬底优化干法和湿法蚀刻工艺

半导体器件制造中的蚀刻工艺技术概述

GaAs的湿法蚀刻和光刻工艺

KOH硅湿法蚀刻工艺详解

湿法蚀刻工艺的原理

InGaP层去除GaAs外延盖层的选择性湿法蚀刻工艺

InGaP层去除GaAs外延盖层的选择性湿法蚀刻工艺

评论