使用Xilinx Vivado 创建自己板卡文件-以 EBAZ4205(旷板ZYNQ7010) 为例

我们在使用Vivado创建工程时,每次都需要选择相关的板卡器件,比较麻烦,这篇文章就教你怎么创建属于自己的板卡文件,在创建工程时就可以像官方板卡一样在板卡列表里选择。

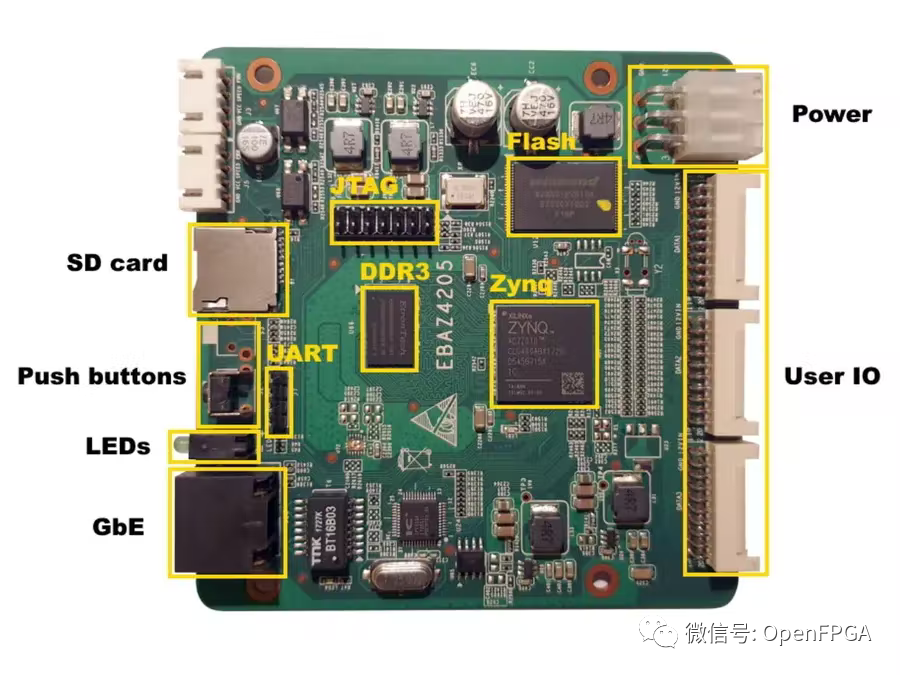

板子

这次的板卡很多人应该不陌生,EBAZ4205-传说中的旷板,之前20元就能买到,使用非常广泛。

参考

UG895 文档描述了电路板文件的结构和内容。

板文件的结构

Xilinx Vivado 板文件存放在 Vivado 安装目录中:

//data/boards/board_files/

在这个目录中,我们可以创建新文件夹并以我们的板子命名(例如 ebaz4205)。在这个目录中,我们将创建另一个以板版本命名的文件夹(例如 1.0)。

该文件夹将包含我们的电路板图片和三个重要的 XML 文件:

-

board.xml - 定义关于板的所有信息。它包括基本信息(例如电路板名称、描述、供应商)、有关板上组件的信息(例如 FPGA 部件、LED、按钮)、有关板上组件所需接口的信息以及实现这些接口的首选 IP 内核。

-

preset.xml - 预设 board.xml 文件中指定的 IP 内核定义。

-

part0_pins.xml - 为board.xml 文件中指定的物理引脚接口定义和 I/O 标准。

创建所有必需的文件夹和文件后,我们的板文件文件夹结构应如下所示:

ebaz4205/

└──1.0

├──board.xml

├──ebaz4205.jpg

├──part0_pins.xml

└──preset.xml

下面针对每个文件简单介绍一下内容。

board.xml

该文件以名为的 XML 标记开头,我们将在其中提供有关该板的基本信息:

"2.1"vendor="miner.ebang.com.cn"name="ebaz4205"display_name="EBAZ4205DevelopmentBoard"url="http://miner.ebang.com.cn"preset_file="preset.xml">

首先,我们定义板文件架构版本 - 告诉 Vivado 软件如何解释文件中提供的数据的属性(在 Vivado 2020.1 中,我目前使用的架构的最新版本是 2.1)。接下来,我们为电路板供应商定义供应商名称、电路板名称和网页。在标签中,我们还指定了稍后将使用的预设文件的名称。在此之后,我们必须通过在新行中写入来关闭标记。所有其他板信息必须在这两个标签之间定义。

为了确保板文件的正常工作,我们必须添加

1.0

"1">1.0

我们可以通过在 中指定图像和在标签中指定描述来添加板的图片和描述:

"ebaz4205.jpg"display_name="EBAZ4205DevelopmentBoard"sub_type="board">

EBAZ4205DevelopmentBoard

EBAZ4205isminingboardusedinEbangEbitE9+bitcoinminermachine.Thisboardfeatures256MBDDR3memory,128MBNANDFlashmemory,10/100MBitEthernetandspeedgrade-1Zynq7010.

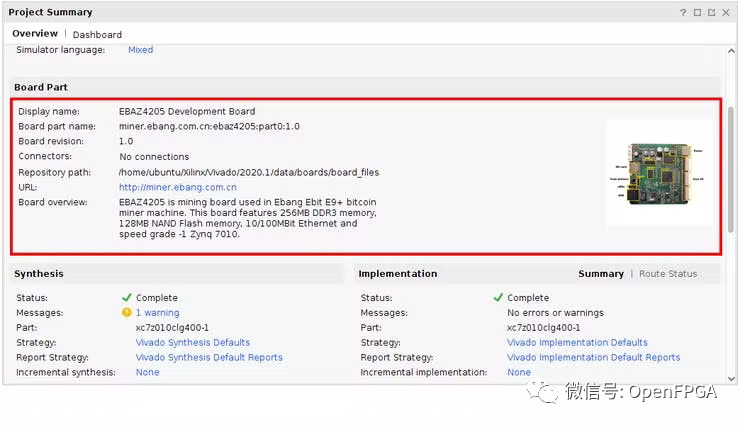

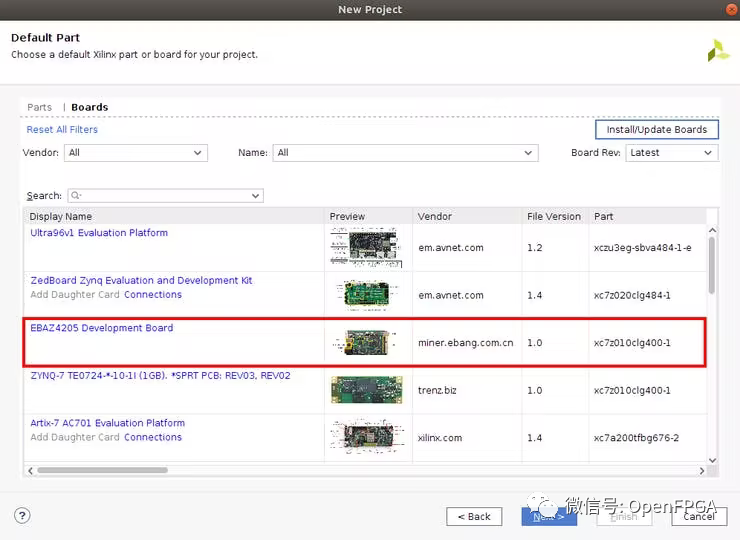

创建新项目时,大部分信息将显示在板选择窗口中:

或在 Vivado 项目摘要窗口中:

提供基本信息后,现在我们可以通过在标签之间添加信息来指定板上的组件:

"part0"display_name="EBAZ4205"type="fpga"part_name="xc7z010clg400-1"pin_map_file="part0_pins.xml"vendor="xilinx"spec_url="www.xilinx.com">

FPGApartontheboard

"master"name="ps7_fixedio"type="xilinx.comfixedio_rtl:1.0"of_component="ps7_fixedio"preset_proc="ps7_preset">

"xilinx.com"library="ip"name="processing_system7"order="0"/>

"master"name="leds_2bits"type="xilinx.comgpio_rtl:1.0"of_component="leds_2bits"preset_proc="leds_2bits_preset">

"xilinx.com"library="ip"name="axi_gpio"order="0"/>

"TRI_O"physical_port="leds_2bits_tri_o"dir="out"left="1"right="0">

"0"component_pin="leds_2bits_tri_o_0"/>

"1"component_pin="leds_2bits_tri_o_1"/>

"ps7_fixedio"display_name="PS7fixedIO"type="chip"sub_type="fixed_io"major_group=""/>

"leds_2bits"display_name="LEDs"type="chip"sub_type="led"major_group="GeneralPurposeInputorOutput">

LEDs,ActiveLow

首先我们必须定义板上使用的 FPGA 型号, EBAZ4205 的情况下它是 xc7z010clg400-1。我们还定义了这个组件的供应商和引脚映射文件。所有用于实现 FPGA 和电路板组件之间接口的 IP 内核都必须在 FPGA 标签之间定义。

第一个定义的接口将是 Zynq 处理系统的固定 I/O。我们必须指定接口模式、名称、首选 IP 核来实现此接口和预设名称(preset_proc),它将 IP 核与 preset.xml 文件中的预定义配置进行链接:

```

第二个定义的接口用于 LED。为了实现这个接口,我们将使用 AXI GPIO IP 内核。对于此接口,我们还必须定义端口引脚映射,因为 AXI GPIO IP 内核端口引脚必须连接到物理 FPGA 引脚:

"master"name="leds_2bits"type="xilinx.comgpio_rtl:1.0"of_component="leds_2bits"preset_proc="leds_2bits_preset">

"xilinx.com"library="ip"name="axi_gpio"order="0"/>

"TRI_O"physical_port="leds_2bits_tri_o"dir="out"left="1"right="0">

"0"component_pin="leds_2bits_tri_o_0"/>

"1"component_pin="leds_2bits_tri_o_1"/>

在定义 FPGA 部分及其接口之后,我们必须定义其他组件。默认情况下一个是 Zynq 7000 处理系统,另一个是 LED。之前创建的接口将通过称为组件名称的属性链接到这些组件:

"ps7_fixedio"display_name="PS7fixedIO"type="chip"sub_type="fixed_io"major_group=""/>

"leds_2bits"display_name="LEDs"type="chip"sub_type="led"major_group="GeneralPurposeInputorOutput">

LEDs,ActiveLow

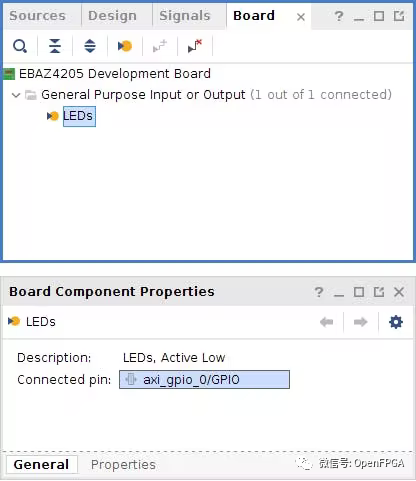

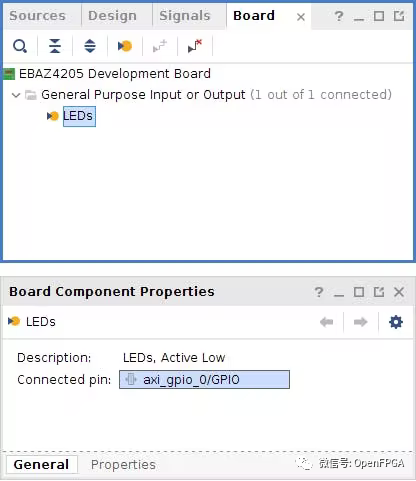

该声明还让我们可以在 Vivado 模块设计窗口的 Board 选项卡中找到我们的组件:

在 board.xml 文件中,如果方便,我们还必须为板上的所有组件定义 JTAG 链。在这种情况下,我们只有一个用于 FPGA 部分的 JTAG 链:

"chain1">

"0"component="part0"/>

当然,我们必须指定将我们的组件接口链接到在 part0_pins.xml 文件中声明的物理 FPGA 引脚的连接:

"part0_leds_2bits"component1="part0"component2="leds_2bits">

"part0_leds_2bits_1"c1_st_index="0"c1_end_index="1"c2_st_index="0"c2_end_index="1"/>

这里 c1_st_index 和 c1_end_index 对应 part0_pins.xml 文件中的 pin 索引,而 c2_st_index 和 c2_end_index 对应 IP 核端口 pin 索引。

preset.xml

preset.xml 文件以名为

"1.0">

我们必须通过在新行中写入 来关闭

首先我们为 Zynq 处理系统 IP 核添加配置。这些配置通过名为 preset_proc_name 的属性链接到 board.xml 文件:

"ps7_preset">

"xilinx.com"library="ip"name="processing_system7"version="*">

"CONFIG.PCW_UART1_PERIPHERAL_ENABLE"value="1"/>

"CONFIG.PCW_UART1_UART1_IO"value="MIO24..25"/>

"CONFIG.PCW_SD0_PERIPHERAL_ENABLE"value="1"/>

"CONFIG.PCW_SD0_SD0_IO"value="MIO40..45"/>

"CONFIG.PCW_NAND_PERIPHERAL_ENABLE"value="1"/>

"CONFIG.PCW_NAND_GRP_D8_ENABLE"value="0"/>

"CONFIG.PCW_ENET0_PERIPHERAL_ENABLE"value="1"/>

"CONFIG.PCW_ENET0_ENET0_IO"value="EMIO"/>

"CONFIG.PCW_ENET0_GRP_MDIO_ENABLE"value="1"/>

"CONFIG.PCW_ENET0_PERIPHERAL_FREQMHZ"value="100Mbps"/>

"CONFIG.PCW_GPIO_MIO_GPIO_ENABLE"value="1"/>

"CONFIG.PCW_GPIO_MIO_GPIO_IO"value="MIO"/>

"CONFIG.PCW_ENET_RESET_ENABLE"value="0"/>

"CONFIG.PCW_USB_RESET_ENABLE"value="0"/>

"CONFIG.PCW_I2C_RESET_ENABLE"value="0"/>

"CONFIG.PCW_UIPARAM_DDR_BUS_WIDTH"value="16Bit"/>

"CONFIG.PCW_UIPARAM_DDR_PARTNO"value="MT41K128M16JT-125"/>

在 Zynq 7000 处理系统中,我们启用 UART1、SD0、NAND、ETHERNET0 和其他外设,为这些外设选择 MIO 引脚并配置 DDR 内存。

接下来,我们为 AXI GPIO IP 内核添加配置,该内核将用于在板上实现 FPGA 和用户 LED 之间的接口:

"leds_2bits_preset">

"xilinx.com"library="ip"name="axi_gpio"ip_interface="GPIO">

"CONFIG.C_GPIO_WIDTH"value="2"/>

"CONFIG.C_ALL_OUTPUTS"value="1"/>

"CONFIG.C_ALL_INPUTS"value="0"/>

"CONFIG.C_DOUT_DEFAULT"value="0x00000003"/>

在这里,我们将 AXI GPIO IP 内核配置为只有 2 个引脚将用作默认逻辑值为 1 的输出,因为该板上的 LED 处于低电平有效(通过提供逻辑 0 开启)。

part0_pins.xml

part0_pins.xml 文件在

"xc7z010clg400-1">

"0"name="leds_2bits_tri_o_0"iostandard="LVCMOS33"loc="W14"/>

"1"name="leds_2bits_tri_o_1"iostandard="LVCMOS33"loc="W13"/>

此处列出的引脚通过引脚名称属性链接到 board.xml 文件中指定的 IP 核端口引脚。我们将 I/O 标准设置为 LVCMOS33,因为这些引脚所在的 FPGA bank 的电压在 EBAZ4205 板上设置为 3.3V。最后,我们通过提供位置属性 loc 将 IP 核端口引脚链接到物理 FPGA 封装引脚。

我希望本教程能帮助各位更好地了解 Xilinx Vivado 电路板文件结构以及如何为你的开发板定制电路板创建这些文件。

完整的 EBAZ4205 板文件可以在下面的链接中找到,只需要放到文章开头的路径下即可:

https://github.com/suisuisi/EBAZ4205/tree/main/Documents/Board%20files

路径下还有Spartan Edge Accelerator开发板的文件。

-

电路板

+关注

关注

140文章

4963浏览量

98060 -

Vivado

+关注

关注

19文章

812浏览量

66617

原文标题:使用Xilinx Vivado 创建自己板卡文件-以 EBAZ4205(旷板ZYNQ7010) 为例

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SRIO介绍及xilinx的vivado 2017.4中生成srio例程代码解释

Xilinx_Vivado_SDK的安装教程

Vivado使用小技巧

使用Xilinx Vivado创建自己板卡文件

使用Xilinx Vivado创建自己板卡文件

评论